RISC-V 명명 코드 잠금 해제

RISC-V 명령어 세트 아키텍처(ISA)는 특별한 기회를 제공합니다. 개발자는 이 구조를 통해 전례 없는 소프트웨어 호환성을 제공하는 다양한 크기와 성능의 프로세서를 사용할 수 있습니다. 이 호환성을 활용하는 핵심은 RISC-V 코어 명명 코드를 이해하는 것입니다.

대부분의 프로세서 아키텍처와 달리 RISC-V는 오픈 소스이며 라이선스나 로열티 비용 없이 개발자에게 제공됩니다. 또한 ISA는 개발자가 구현하고자 하는 명령어 블록을 선택하고 필요 없는 것은 생략할 수 있으며, 사용자 지정 명령도 추가할 수 있도록 유연하게 설계되었습니다. 그 목적은 공통 기반을 공유하는 다양한 크기와 성능 속성을 가진 다중 프로세서 코어의 개발을 촉진하는 것입니다.

이 공통 기반은 기능 세트와 관계없이 프로세서 간에 높은 수준의 소프트웨어 호환성을 제공합니다. 예를 들어 정수 명령어 세트만 구현하는 최소 RISC-V 프로세서의 코드는 정수 및 부동 소수점 기능을 모두 갖춘 보다 강력한 프로세서에서 수정되지 않은 상태로 실행됩니다. 물론 부동 소수점 명령어를 사용하는 코드는 정수 전용 기계에서 실행되지 않지만 프로세서 충돌 원인이 되지도 않습니다. 구현되지 않은 명령어는 단순히 잘못된 명령어 트랩을 생성합니다.

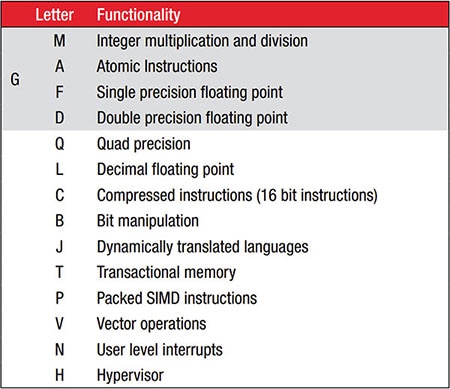

RISC-V ISA는 중복되지 않는 기계 코드를 갖는, 본질적으로 독립적인 그룹으로 명령어들을 분할하여 유연성을 확보합니다. 이러한 명령어 그룹을 '표준 확장'이라고 하며, ISA는 개발자에게 필요한 대부분의 기능을 제공하는 수많은 표준 확장을 정의했습니다. 각 표준 확장은 문자 코드로 식별됩니다. 예를 들어 'M' 표준 확장은 레지스터에 있는 두 정수를 곱하거나 나누는 명령어를 제공합니다. 마찬가지로 'F' 표준 확장은 단정밀도 부동 소수점 연산에 대한 명령어를 제공합니다.

프로세서 개발자는 RISC-V 코어를 구현할 때 표준 확장을 짜 맞출 수 있기 때문에 사용자는 설계하려는 프로세서가 실제로 무엇을 할 수 있는지 결정하기 위해 사양서와 프로그래밍 설명서를 주의 깊게 읽어야 할 것처럼 보입니다. 하지만 더 간단한 해결책이 있습니다. RISC-V는 사용자에게 코어의 기능을 즉시 알려주는 코어 번호 지정 규칙을 사용합니다.

번호 지정 규칙은 기본 사양부터 시작합니다. RISC-V는 다음 네 가지 기본 사양을 정의했습니다.

- RV32I - 32비트 정수 명령어 세트가 있으며 32개의 범용 레지스터를 제공합니다.

- RV32E - 16개의 레지스터가 있는 내장형 응용 제품을 대상으로 하는 32비트 명령어 세트를 사용합니다.

- RV64I - 32개의 레지스터가 있는 64비트 정수 명령어 세트가 있습니다.

- RV128I - 32개의 레지스터가 있는 128비트 정수 명령어 세트가 있습니다.

이러한 기본 사양은 완전히 기능하는 프로세서를 정의합니다. 그러나 대부분의 개발자는 설계에 하나 이상의 표준 명령어 세트 확장을 추가하기를 택합니다. 이러한 표준 확장과 식별 문자는 그림 1에 나열되어 있습니다.

그림 1: RISC-V 프로세서의 표준 명령어 세트 확장은 문자 코드를 사용하여 코어의 넘버링 규칙에 문자 코드가 있음을 나타냅니다. (이미지 출처: DigiKey)

그림 1: RISC-V 프로세서의 표준 명령어 세트 확장은 문자 코드를 사용하여 코어의 넘버링 규칙에 문자 코드가 있음을 나타냅니다. (이미지 출처: DigiKey)

완전한 RISC-V 코어 지정은 그림 1에 나열된 순서대로 구현하는 표준 확장 문자가 추가된 기본 사양을 제공합니다. 최소 리소스를 사용하는 소규모 SoC에는 RV32EMAB라는 지정이 있을 수 있습니다. 이는 코어가 내장형 장치에 32비트 정수 명령어 세트를 구현하고, 16개의 레지스터를 포함하고 있으며, 원자적 명령어뿐만 아니라 정수 곱셈 및 나눗셈을 실행한다는 것을 의미합니다. 부동 소수점 연산 기능은 없지만 비트 조작을 지원합니다.

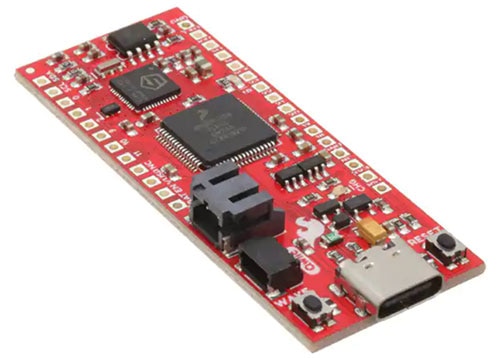

따라서 설계에 사용할 RISC-V 칩을 선택할 때 사용자는 어떤 기능을 제공하는지 알기 위해 코어 지정만 검토하면 됩니다. 예를 들어 SparkFun Electronics의 DEV-15799 FE310 Thing Plus RISC-V 평가 기판의 프로세서는 RV32IMAC 코어로 나열됩니다(그림 2).

그림 2: DEV-15799 기판의 RISC-V 프로세서의 이름은 RV32IMAC이며 다른 기능으로는 32비트 정수 명령어 세트, 32개의 레지스터를 가지고 있으며 원자적 명령어를 제공합니다. (이미지 출처: SparkFun Electronics)

그림 2: DEV-15799 기판의 RISC-V 프로세서의 이름은 RV32IMAC이며 다른 기능으로는 32비트 정수 명령어 세트, 32개의 레지스터를 가지고 있으며 원자적 명령어를 제공합니다. (이미지 출처: SparkFun Electronics)

이는 코드 공간 최소화를 위하여 32비트 정수 명령어 세트, 32개 레지스터, 정수 곱셈 및 나눗셈 구현, 원자성 명령어 제공, 압축(16비트) 명령어를 지원함을 의미합니다. 이 기판에서 개발된 모든 코드는 곱셈 및 누적(MAC) 표준 확장을 사용하는 다른 RV32I 코어에서도 실행할 수 있습니다.

또 다른 예로, Seeed Technology의 114991684 Sipeed MAXIX-I RISC-V SoC 모듈은 RISC-V 코어를 RV64IMAFDC로 나열합니다. 정수 곱하기 및 나누기, 원자적 명령어, 단정밀도 및 배정밀도 부동 소수점, 압축 명령어를 포함한 64비트 명령어 세트가 있습니다. 이 프로세서를 위해 개발된 코드는 코어 지정이 동일한 모든 RISC-V 프로세서에서 실행되어야 하지만 주변기기 등의 메모리 매핑을 조정해야 할 수도 있습니다.

결론

RISC-V 명명 코드를 사용하면 이 강력한 아키텍처로 사용자는 자신 있게 실험을 시작할 수 있습니다. 코어 코드를 일치시킴으로써 사용자는 하나의 프로세서를 사용한 프로그래밍 작업이 다른 RISC-V 프로세서로의 이식성이 높다는 것을 확신할 수 있습니다.

이 실험을 시작하기 전에 여러 RISC-V 평가 기판의 초기 설정과 사용법을 안내하는 Guide to RISC-V를 확인하면 도움이 될 수 있습니다.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum