RISC-V 곱셈 확장이 RV32I에 효율적인 32비트 곱셈을 추가하는 방법

RISC-V 명령어 집합 아키텍처(ISA)는 2010년 Berkley에서 시작되었습니다. 제조업체는 RISC(축소 명령어 집합 컴퓨터/코어) ISA를 사용하며 여기에 명령어를 추가하고, 새로운 주소 지정 모드를 추가하여 RISC보다는 CISC가 될 때까지 연산 부호 맵을 채웁니다. 그러나 RISC-V의 Berkley 개발자들은 코어를 아주 엄격하게 진정한 RISC로 유지했습니다. RV32I RISC-V ISA는 47개의 기본 명령어(오랜 Star Trek 팬에게는 의미가 있는 숫자)만 갖도록 설계되었으며 11년이 지난 지금도 동일한 수를 유지하고 있습니다.

기본 명령어 수를 낮게 유지하는 기본 원칙은 복잡한 CISC 명령어를 일련의 간단한 RISC 명령어로 재현할 수 있다는 것입니다. 제 경험에 따르면 이것이 코드 효율성을 높이고 코드 크기를 줄이는지는 애플리케이션에 따라 다릅니다. 과거에는 분명히 사실이었습니다. Arm이 복잡한 명령어를 연산 부호 맵에 추가했을 정도였습니다.

추가 명령어를 사용하면 성능 향상에 도움이 되지만 32비트 명령어가 있는 32비트 코어가 있고 일부 32비트 명령어를 16비트 명령어로 압축하여 공간을 절약하려는 기능을 추가하려는 경우 상황이 더 복잡해집니다 그러나 16비트 명령어를 추가하기 위해 코어에는 이러한 압축된 명령어를 위한 연산 부호 맵에 추가 공간이 있어야 하며, CISC 명령어를 추가하면 사용 가능한 연산 부호 수가 줄어듭니다.

바로 여기서 RISC-V의 장점이 빛을 발합니다. Arm은 이후에 Thumb2 압축 명령어 형식을 추가하고 별도의 16비트 ISA를 추가하여 이러한 16비트 명령어를 기존 ISA에 맞추었습니다. 그러나 RISC-V ISA는 처음부터 압축 명령어를 위한 옵션을 사용하여 설계되었으며, 따라서 하나의 ISA만 있습니다. 이는 코어를 단순하고 효율적으로 유지하며 반도체 설계 및 테스트를 단순화합니다.

곱셈 명령어를 사용한 RISC-V RV32I ISA

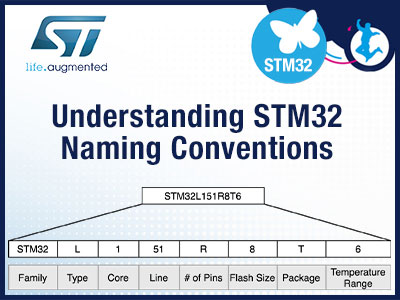

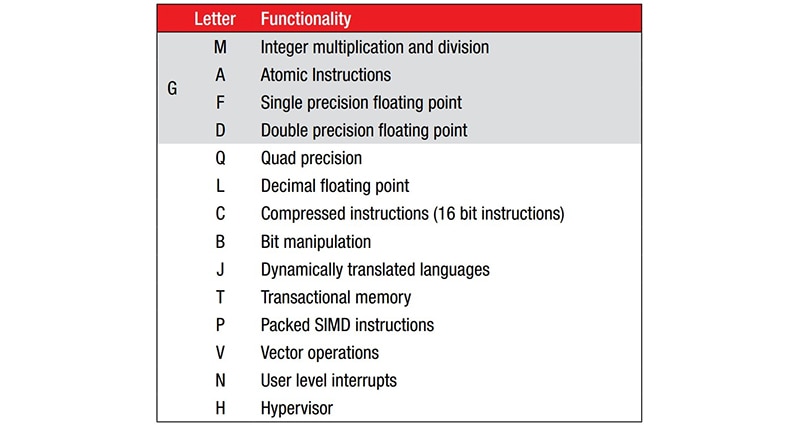

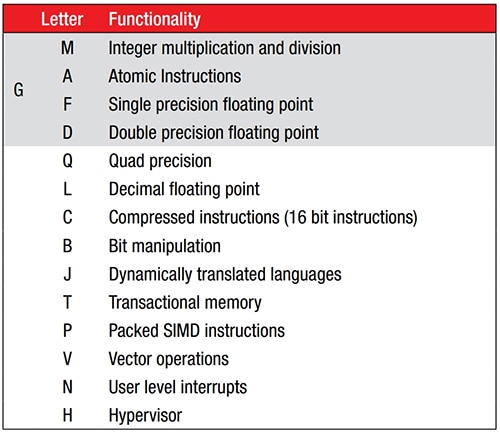

제조업체는 표준화된 명령어 확장을 추가하여 47개 명령어 ISA를 확장할 수 있습니다(그림 1). 기본 ISA에는 곱셈 또는 나눗셈 명령어가 없으므로 M 확장이 해당 기능을 제공합니다. 예를 들어, M 확장자를 가진 RV32I는 RV32IM으로 지정됩니다.

그림 1: 47개 명령어의 RISC-V 기본 ISA는 코어 이름 뒤에 문자 접미사로 표시되는 표준화된 명령어 확장을 추가하여 확장할 수 있습니다. (이미지 출처: RISC-V.org)

그림 1: 47개 명령어의 RISC-V 기본 ISA는 코어 이름 뒤에 문자 접미사로 표시되는 표준화된 명령어 확장을 추가하여 확장할 수 있습니다. (이미지 출처: RISC-V.org)

M 확장 코어의 예시로는 오픈 소스 150메가헤르츠(MHz) Freedom E310(FE310) 32비트 RISC-V 마이크로 컨트롤러가 있는 SparkFun Electronics RED-V Thing Plus가 있습니다. FE310 코어는 RV32IMAC으로 지정됩니다. 기본 정수 연산(I) 기능 외에도, 정수 곱셈(M), 원자 명령어(A) 및 압축 명령어(C)를 지원합니다(그림 1 참조).

SparkFun DEV-15799 RED-V('레드 파이브'로 발음됨) RISC-V 평가 기판(그림 2)에는 32메가바이트(MB)의 프로그램 메모리 QSPI 플래시가 있으며 전력, 프로그래밍 및 디버깅을 위해 호스트 컴퓨터에 인터페이스하는 USB-C 커넥터가 있습니다. 배터리 전원 공급에 사용할 수 있는 추가 커넥터도 있습니다.

그림 2: SparkFun DEV-15799 기판은 오픈 소스 150MHz FE310 RV32IMAC RISC-V 코어 평가에 사용됩니다. 이는 USB-C 인터페이스를 통해 호스트 컴퓨터에 인터페이스합니다. (이미지 출처: SparkFun Electronics)

그림 2: SparkFun DEV-15799 기판은 오픈 소스 150MHz FE310 RV32IMAC RISC-V 코어 평가에 사용됩니다. 이는 USB-C 인터페이스를 통해 호스트 컴퓨터에 인터페이스합니다. (이미지 출처: SparkFun Electronics)

M 확장자는 signed 및 unsigned 32/32 분할 명령어 DIV 및 DIVU뿐만 아니라 signed 및 unsigned 나머지 명령어 REM 및 REMU를 추가합니다. 또한 다음 4개의 곱셈 명령어를 추가합니다.

- MUL은 32 x 32 레지스터 곱셈을 수행하고 64비트 결과의 하위 32비트를 레지스터에 저장합니다.

- MULH와 MULHU는 각각 signed 및 unsigned 레지스터 곱셈을 수행하고 64비트 결과의 상위 32비트를 레지스터에 저장합니다.

- MULSHU는 signed x unsigned 레지스터 곱셈을 수행하고 64비트 결과의 상위 32비트를 레지스터에 저장합니다.

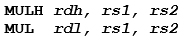

따라서 32 x 32 = 64 unsigned 곱셈의 경우 권장 코드 시퀀스는 다음과 같습니다.

여기서 레지스터 rs1 및 rs2는 피승수 및 승수이고 레지스터 rdh 및 rdl은 각각 상위 및 하위 32비트 결과입니다.

ISA는 64비트 곱셈 결과를 두 개의 32비트 연산 나눗셈으로 나누기 때문에 복잡한 32 x 32 = 64 CISC 명령어를 추가할 필요가 없습니다. 이는 간단한 명령어를 사용하여 CISC 작업을 수행한다는 RISC 원칙과 일치합니다.

기본 RV32I ISA에 있는 대부분의 명령어는 한 번의 명령어 클록 주기에서만 실행되지만 RED-V FE310의 이러한 곱셈 명령어에는 다섯 번이 필요합니다. 이런 이유로, 위에서 권장된 코드 시퀀스를 실행하려면 열 번의 클록 주기가 필요합니다. 이는 150MHz에서 허용될 수 있지만, 제가 본 초저전력, 저클록 속도 마이크로 컨트롤러 애플리케이션에서는 인터럽트가 매우 중요하기 때문에 10주기를 곱하는 것은(5MHz 기준) 중대한 인터럽트를 기다리기에 너무 길었습니다. 이런 경우에 펌웨어 개발자는 인터럽트가 허용된 복잡한 어셈블리 하위 루틴을 사용하여 곱셈을 수행했습니다.

그러나 FE310 코어는 연속적인 명령어를 받아 매크로 연산 융합을 통해 내부적으로 더 빠른 하나의 명령어로 융합할 수 있습니다. 코어 마이크로 아키텍처는 2개의 명령어를 10주기보다 빠르게 실행되는 하나의 내부 명령어로 융합할 수 있습니다. RISC-V 마이크로 아키텍처는 인덱스 로드, 로드 쌍 및 저장 쌍 명령어와 같은 일부 코드 시퀀스에 대해 이 작업을 자동으로 수행하여 실행 속도를 크게 개선합니다. 더 좋은 점은 FE310은 2개의 호환 가능한 16비트 압축 명령어를 융합할 수 있을 때 'C' 확장을 지원하므로 코드와 실행 속도의 장점을 모두 제공할 수 있다는 것입니다.

Arm이 이후에 압축 명령어와 마찬가지로 매크로 연산 융합을 아키텍처에 추가한 반면, RISC-V는 처음부터 매크로 연산 융합으로 설계되었습니다. 코드 압축의 장점과 매크로 연산 융합이 시작될 때를 제대로 이해하는 가장 좋은 방법은 SparkFun DEV-15799와 같은 평가 기판을 사용하여 이러한 동작을 관찰하는 것입니다. 디버거에서 코드를 검사하여 FE310 마이크로 아키텍처가 각 명령어를 가져오고 실행하는 방법을 확인할 수 있습니다. 이를 통해 어셈블리 언어의 동작을 더욱 잘 이해할 수 있으므로 코드 압축과 매크로 연산 융합을 지원하는 C 컴파일러를 사용하여 효율적인 코드를 작성할 수 있습니다.

결론

RISC-V ISA는 47개의 기본 명령어만 있는 진정한 의미의 축소 명령어 집합이라고 자부합니다. 이 기능은 곱셈과 나눗셈 명령어를 추가하는 'M' 곱셈 확장과 같은 표준화된 확장 기능을 통해 향상될 수 있습니다. RISC-V 아키텍처에 내재된 매크로 연산 융합은 연속 곱셈 같은 호환 명령어의 코드 실행 속도를 높일 수 있는 반면 'C' 압축 확장은 코드 크기를 줄입니다. 압축 명령어와 매크로 연산 융합은 다른 아키텍처에 비해 성능에서 상당한 이점을 보입니다.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum