RISC-V Atomic 확장을 통해 비트 조작 성능을 향상시키는 방법

업계에서 RISC-V 아키텍처를 채택하는 비율이 빠르게 늘고 있으며, 그 영향력이 커지고 있는 데는 그럴 만한 이유가 있습니다.

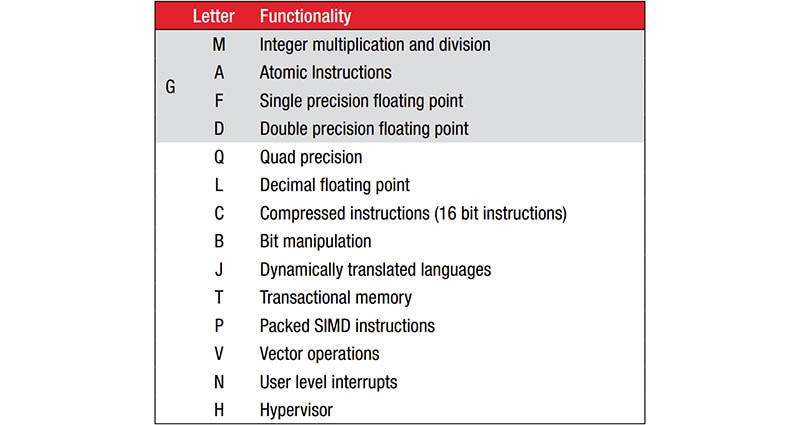

코어 아키텍처 및 진정한 축소형 명령어 집합 아키텍처(ISA) 이외에도, 일련의 표준화된 확장을 통해 개선되었습니다(그림 1). 예를 들어, 여기에 표시된 확장 목록에 따르면 단일 정밀 부동 소수점 및 축약형 명령어도 지원하는 32비트 RISC-V 코어(RV 32)가 RV32FC로 지정됩니다.

그림 1: RISC-V ISA는 코어 이름 뒤에 문자 접미사로 표시되는 일련의 표준화된 명령어 확장을 통해 개선되었습니다. (이미지 출처: RISC-V.org)

그림 1: RISC-V ISA는 코어 이름 뒤에 문자 접미사로 표시되는 일련의 표준화된 명령어 확장을 통해 개선되었습니다. (이미지 출처: RISC-V.org)

많은 인공 지능(AI) 및 머신러닝(ML) 응용 제품과 고급 내장형 시스템에 가장 필요한 네 가지 확장은 정수 곱셈과 나눗셈(M), 아토믹 명령어(A), 단일 정밀 부동 소수점(F) 및 이중 정밀 부동 소수점(D)입니다. 그러나 코어를 RV32MAFD로 지정하는 대신, 이 모두가 RV32G와 같이 모두 접미사 G로 통일됩니다.

다양한 확장 및 일반적인 RISC-V에 대해 더 자세히 알아보려면 DigiKey EDU 사이트의 RISC-V 전자책을 참조하세요.

저는 프로세서에 대한 초기 경험이 딥 임베디드 시스템 관련이었기 때문에, 데이터 메모리에 대한 아키텍처의 읽기-수정-쓰기 비트 조작 지원을 자세히 살펴보곤 합니다. 이러한 응용 제품의 경우 주변 장치 레지스터 및 세마포르에서의 비트 설정 및 지우기가 매우 일반적입니다. 기본 비트 조작 명령이 없으면 코어는 데이터 메모리 위치의 내용을 코어 레지스터에 복사하고, OR, AND 또는 XOR 명령을 사용하여 비트를 각각 설정, 지우기 또는 토글한 다음, 그 결과를 데이터 메모리 위치에 다시 저장해야 합니다. 이러한 작업은 시간이 추가로 소요될 뿐만 아니라 어떤 내장형 컨트롤 응용 제품의 경우에서는 코드 블로트가 20%까지 발생하기도 합니다.

어떤 응용 제품에서는 이러한 코드 블로트 및 성능의 저하가 큰 문제가 아닐 수 있습니다. 그러나 이 세 가지 명령이 처리되는 동안 인터럽트로 인해 작업 중 프로그램 제어가 불가능해질 수 있으며, 더 큰 문제는 다중 프로세서 시스템에서는 동일한 메모리 위치에서 다른 코어가 읽을 수도 있다는 점입니다. 이러한 이벤트가 데이터 메모리를 손상시키지 않도록 인터럽트를 비활성화하거나 메모리를 잠그려면 추가 명령어와 복잡성이 요구되는데, 이는 성능 문제를 발생시킬 수 있습니다.

Arm은 간단한 비트 연산에 해당하는 비트 밴딩을 구현하여 이러한 문제를 해결하고자 했습니다. 하지만 저는 RISC-V가 구현한 방법이 더 우수하고 유연한 솔루션이라고 생각합니다.

Atomic 확장이 우수한 방법인 이유

RISC-V A(Atomic) 확장은 LR/SC 연산(이 문서에서는 다루지 않음) 및 데이터 메모리에 간단한 비트 조작을 제공하는 이진/비트 명령어의 두 가지 연산을 지원합니다. RISC-V B 비트 조작 확장은 일련의 복잡한 비트 제어 명령을 지원하지만, Atomic 확장은 다중 프로세서 시스템만을 대상으로 하는 것은 아닙니다. 필요한 비트 조작 요구가 더 단순한 더욱 작은 내장형 시스템에서도 유용합니다. 그러한 시스템의 예로 Seeed Technology의 114991684 이중 코어, 64비트, RISC-V 모듈이 있습니다. 함께 작동해야 하는 두 개의 RV64GC 코어가 있으며, 공유 데이터 SRAM에서 잘 작동합니다.

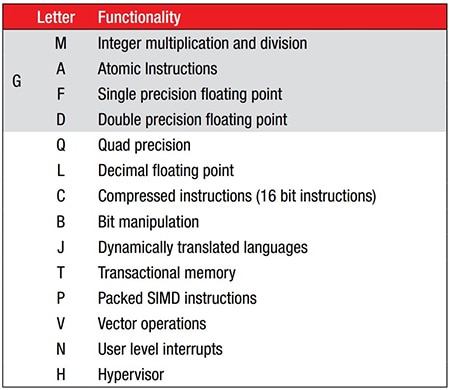

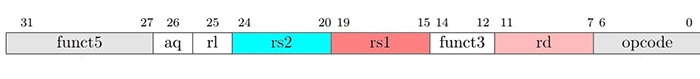

RISC-V A 확장 Atomic 메모리 연산(AMO)의 형식이 그림 2에 표시됩니다.

그림 2: RISC-V AMO 명령어 형식은 단 하나의 명령어로 데이터 메모리에서 아토믹 이진 연산을 지원합니다. (이미지 출처: RISC-V.org(Bill Giovino 수정))

그림 2: RISC-V AMO 명령어 형식은 단 하나의 명령어로 데이터 메모리에서 아토믹 이진 연산을 지원합니다. (이미지 출처: RISC-V.org(Bill Giovino 수정))

AMO는 강력한 읽기-수정-쓰기 명령어로, 단 하나의 명령어로 rs1에 지정된 데이터 메모리에서 직접 다양한 이진 연산을 지원합니다. 그림 2를 살펴보면, 이러한 연산을 통해 rs1에 있는 데이터 메모리 주소 위치의 내용이 로드되고 해당 값이 레지스터 rd에 저장됩니다. 그런 다음 rs2의 값으로 rd의 값에 대해 이진 연산을 수행하고, 해당 값을 rd와 rs1의 데이터 메모리 주소 위치에 다시 저장합니다.

OR(비트 설정), AND(비트 지우기) 및 XOR(비트 토글)의 비트 연산이 지원됩니다. 이를 통해 데이터 메모리에서 직접 하나 이상의 비트의 아토믹 비트 조작이 가능해집니다. 또한 이는 두 개의 RV64GC 코어가 동시에 동일한 메모리 주소를 사용하는 경우의 메모리 충돌을 방지합니다. 소형 내장형 응용 제품에서 메모리에 주변 장치 레지스터를 구성할 때와, 세마포르 작업을 단순화할 때 매우 유용합니다.

RISC-V AMO는 정수 최대값, 정수 최소값 및 스왑 연산도 지원합니다. 데이터 메모리에서 카운터를 직접 증가시키는 것을 포함하여 직접 이진 추가를 허용하는 이진 ADD도 지원됩니다.

RV64 코어는 32비트 및 64비트 연산을 모두 지원합니다. RV64를 통한 비트 조작의 경우, 작업이rd에 있는 32비트 데이터를 부호 확장하므로 64비트 데이터만 연산하는 것이 중요합니다.

결론

RISC-V ISA는 Arm ISA에 도전장을 던지는 최초의 진정한 경쟁자입니다. ISA 확장은 비용 효율적으로 응용 제품의 성능을 향상시킬 수 있는 연산을 통해 코어를 향상시키는 표준화된 방법을 제공합니다. 저는 Atomic 확장을 선택할 수 있다는 점이 특히 매우 마음에 듭니다.

멀티 프로세서 시스템에서 매우 유용하고 필요가 큰 Atomic 확장은 또한 데이터 메모리에 직접 비트 조작을 제공할 수 있는 효율적인 방법이기도 합니다. 코드 크기를 줄이고 성능을 향상시킴으로써 기존의 많은 아키텍처에 비해 상당한 이점을 제공합니다.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum