JK 플립 플롭 작동 방식

오리지널 Digi-Keyer를 사용하는 실용적 사례

소개

플립 플롭은 단일 비트의 이진 데이터를 두 개의 안정적인 상태로 저장하는 데 사용되는 집적 회로입니다. 플립 플롭은 카운터, 레지스터, 주파수 분할기 등과 여기에 예시로 사용된 순차 논리 회로(비안정 다중 진동기라고도 함)에서 널리 사용됩니다.

설정 및 리셋 입력, 지우기, 사전 설정, 클록 입력, 보완 논리 출력과 같은 공통 기능을 지원하는 다양한 유형의 플립 플롭을 선택할 수 있습니다. 이러한 유형은 클록 입력의 상승 또는 하강 에지 전이에 의해 작동됩니다. 일반적인 유형에는 SR 플립 플롭, D 플립 플롭 또는 T 플립 플롭이 있습니다. JK 플립 플롭은 많은 다른 유형을 에뮬레이트하도록 구성될 수 있다는 점에서 '범용'이라고도 합니다.

JK 플립 플롭 기능

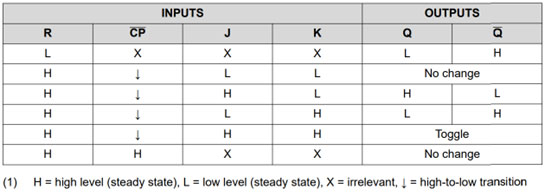

플립 플롭으로 작업할 경우 다중 입력 옵션 및 클록 전이에 따라 출력 특성을 결정하기 위해 장치 규격서의 진리표를 항상 가까이 두어야 합니다. 예를 들어 Texas Instrument CD74HCT73E는 공통된 특성과 읽기 쉬운 진리표를 포함하는 일반적인 이중 JK 플립 플롭입니다.

기억해야 할 두 가지 기본적인 사실이 있습니다. 즉, Q(bar) 또는 notQ 출력은 항상 Q 출력을 보완하며 클록 입력이 High에서 Low로 전이될 때 출력을 결정하는 JK 입력 구성이 4개에 불과합니다. 가능한 JK 구성은 그림 1을 참조하십시오. 토글이란 J와 K가 모두 High이고 클록이 High에서 Low로 전이될 때 Q 및 notQ 출력의 현재 상태가 뒤집힌다는 것을 의미합니다(진리표의 조건 4).

그림 1. 일반적인 JK 플립 플롭 규격서 진리표.

그림 1. 일반적인 JK 플립 플롭 규격서 진리표.

언급된 기본 사실에서는 리셋(R)이 Low로 유지될 때 플립 플롭에 초기 상태를 제공하는 리셋 입력을 고려하지 않습니다. 규격서에서 '관련 없음'이란 용어는 리셋이 Low일 때 클록 및 JK 입력과 관련하여 사용됩니다. 이러한 입력 변경은 리셋이 High로 유지되고 클록 전이가 수신될 때까지 출력에 영향을 주지 않습니다.

고려할 사항: 플립 플롭을 처음으로 켤 때 출력이 알려진 상태로 자동으로 설정되지 않습니다. 우세한 출력 상태를 예측할 수 있는 방법이 없으므로, 리셋 입력을 사용하면 전원을 켠 후 출력을 알려진 상태로 초기화할 수 있습니다.

순차 논리 회로 예: 모스 문자 생성기

3개의 DIT로 구성되는 DAH

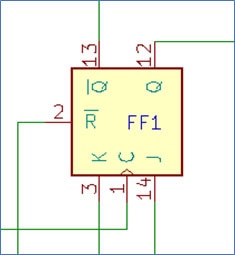

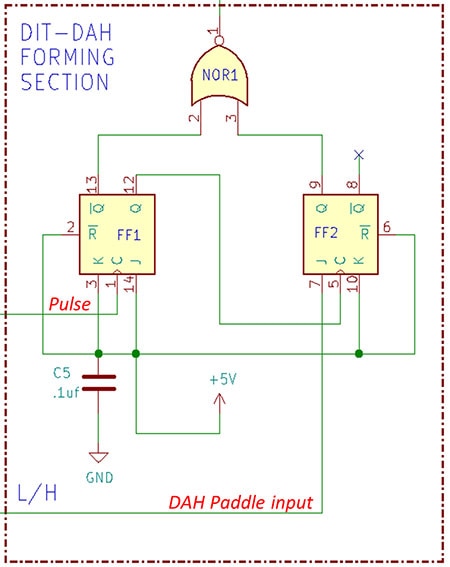

Digi-Keyer 모스 문자 생성기에는 특정 작업을 수행하는 다양한 부품이 있습니다. 플립 플롭이 수행하는 역할을 입증하기 위해 플립 플롭에는 FF1 및 FF2라는 관련 소자가 포함되어 있습니다. Digi-Keyer DIT-DAH 문자 형성 섹션의 회로도는 그림 2를 참조하십시오.

그림 2. Digi-Keyer 플립 플롭 문자 형성 회로

그림 2. Digi-Keyer 플립 플롭 문자 형성 회로

문자(DIT 및 DAH(DOT 및 DASHES라고도 함)) 생성에 대해 알아보기 전에 NOR1 논리 게이트의 기능을 살펴보겠습니다. NOR1은 문자 출력 회로의 첫 번째 단계일 뿐만 아니라, 타이밍 회로에서 NOR1 출력이 Low인 동안 FF1에 규칙적인 펄스를 제공하도록 지원합니다. NOR1 출력이 High인 경우 현재 타이밍 주기가 끝나면 펄스가 중단됩니다.

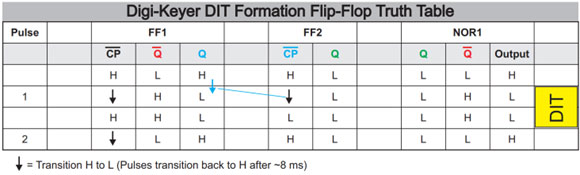

DIT 패들 스위치를 누르면 타이밍 회로에서 FF1의 C 입력으로 초기의 High-Low 전이 펄스가 트리거됩니다. JK 입력이 모두 High로 유지되므로 출력 핀 Q 및 notQ가 토글됩니다. NotQ가 NOR1로 전환되면 Low 신호가 타이밍 회로에 다시 출력되어 DIT가 처리 중임을 나타냅니다. 타이밍 기능이 완료되면 다른 펄스가 FF1으로 전송되어 다시 정상 상태로 전환됩니다. DIT 형성 중에 FF1의 Q 출력이 FF2의 C 입력으로 전환되지만, DAH 패들을 누르지 않았으므로(FF2의 J 입력이 Low임) FF2의 출력이 그림 1에 있는 진리표의 조건 3을 따릅니다. 그림 3에서는 단일 DIT 생성을 위한 결과적 순차 논리 진리표를 소개합니다.

그림 3. 순차 논리 DIT 형성 진리표.

그림 3. 순차 논리 DIT 형성 진리표.

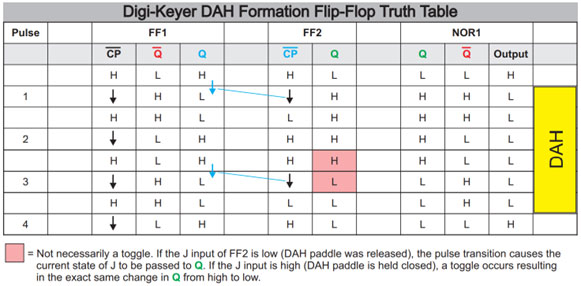

또한 DAH 패들을 누르면 FF1을 토글하는 타이밍 회로의 초기 펄스가 트리거되어 FF2의 J 입력이 High로 설정되며 이로 인해 FF2 출력도 토글됩니다. 또한 FF2의 Q 출력이 NOR1 출력을 Low로 트리거하므로 타이밍 펄스가 지속됩니다. NOR1의 출력은 FF1과 FF2가 모두 정상 상태로 복귀될 때까지 다시 High로 변경되지 않습니다. 따라서 세 DIT 주기가 필요합니다. 그림 4에서는 단일 DAH 생성을 위한 순차 논리 진리표를 소개합니다.

그림 4. 순차 논리 DAH 형성 진리표.

그림 4. 순차 논리 DAH 형성 진리표.

플립 플롭이 정상 상태로 복귀하는 데 걸리는 시간은 High-Low 전이 간격에 따라 달라집니다. 이 예에서 1 펄스 주기의 Low 타임은 8ms로 고정되지만 High 타임은 타이밍 회로망에서 15ms ~ 150ms 사이로 조정할 수 있습니다. 가장 느린 설정에서 DIT 문자의 길이는 약 158ms이고 DAH는 약 474ms입니다. FF1 및 FF2를 정상 상태로 되돌리는 최종 High-Low 전이는 8ms 후에 다시 High로 전환되어 두 패들 중 하나 또는 모두가 닫힌 상태(High)로 유지될 경우 문자 사이에 고정된 공간을 생성합니다.

다른 고려할 사항: 앞서 언급한 대로 회로를 켤 때 FF1과 FF2는 임의 논리 상태가 될 수 있습니다. NOR1 출력에서 상태가 Low인 경우 FF1 및 FF2가 정상 상태에 도달할 때까지 타이밍 회로에서 펄스를 전송하기 시작합니다. 따라서 플립 플롭은 리셋 입력을 사용하지 않고 전원을 켠 후 자동으로 정상 상태로 초기화됩니다.

요약

플립 플롭 논리를 단계별로 따르는 것이 어려울 수 있습니다. 따라서 그림 3 및 그림 4와 같은 진리표를 생성하면 백그라운드에서 진행되는 작업을 시각화하는 데 도움이 됩니다. 이 예에서는 마이크로 컨트롤러 또는 고정 상시 실행 클록을 사용하지 않고 다단계 순차 논리를 수행했습니다. 출력 변경에 영향을 주려면 의도적인 입력 변경이 필요하다는 점에서 플립 플롭 출력은 저장된 데이터입니다. 또한 데이터는 휘발성입니다. 따라서 전력을 제거하면 데이터가 손실됩니다. 모스 문자 생성기의 목적은 데이터를 생성하는 것이 아닙니다. 플립 플롭은 이전 상태를 기억하여 클록 펄스의 High-Low 전이 중 다음 상태를 결정하기 위해 사용됩니다.

관련 자료:

How Does the Digi-Keyer Work(Digi-Keyer 작동 방식)

Digi-Keyer를 구축하고 그 작동 방법에 대해 알아보시겠습니까? DigiKey는 다음 리포지토리에서 완전한 계획, 재료 명세서, 프로그래밍 코드, PCB 파일 등을 제공합니다.

https://media.digikey.com/pdf/Project%20Repository/Digikeyer.zip

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum