회로 안정성을 보장하기 위해 보데 플롯을 활용하는 방법

1930년대에 Hendrik Wade Bode는 회로의 안정성을 유일한 목표로 하여 직관적인 이득/위상 접근법을 만들었습니다. 오늘날 이 접근법은 회로 또는 증폭기의 이득, 위상, 피드백 시스템을 주파수를 통해 직관적인 그래프로 나타낸 보데 플롯이라고 불립니다.

유용성과 중요성을 고려하여 보데 안정성 분석 기술을 적용함으로써 개방 루프 증폭기와 회로 피드백 인자 크기를 데시벨(dB)과 위상 응답(도)으로 살펴보겠습니다. 본 블로그에서는 이러한 개념을 살펴보고 주요 목표가 주파수 안정성일 때 '불안정한' 회로를 설계하지 않는 방법을 제안합니다.

이 기술을 연습하기 위해 온라인 DigiKey Innovation Handbook(DigiKey 혁신 핸드북)의 관련 자료에서 인쇄 가능한 버전의 보데 플롯 그래프를 다운로드할 수 있습니다.

단극 보데 플롯

단극 회로의 구성에서 DC VIN 신호가 VOUT으로 직접 전달될 수 있는 한편, 더 높은 입력 주파수에서 VOUT은 0데시벨(dB)과 같습니다. 보데 플롯 구조는 간단합니다. y축 단위는 대수 주파수이고 선형 x축은 이득(데시벨) 또는 위상(도)입니다. 보데 플롯을 설계할 때 적용할 수 있는 공식이 상당히 많지만, 빠른 솔루션 접근법을 곧바로 살펴보겠습니다.

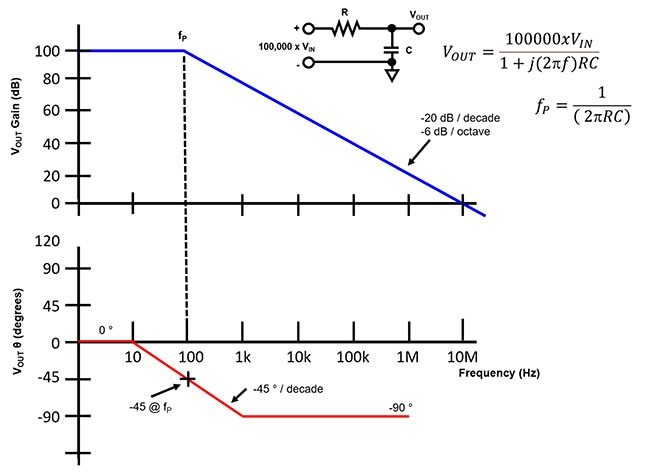

몇 가지 규칙을 알고 있는 상태에서 직선 자 도구만 있으면 그래프를 그릴 수 있을 정도로 보데 플롯은 간단합니다(그림 1).

그림 1: 크기와 위상 변이를 나타내는 단극 보데 플롯은 직선을 사용하여 회로의 주파수와 위상 응답을 보여줍니다. (이미지 출처: Bonnie Baker)

그림 1: 크기와 위상 변이를 나타내는 단극 보데 플롯은 직선을 사용하여 회로의 주파수와 위상 응답을 보여줍니다. (이미지 출처: Bonnie Baker)

그림 1의 두 플롯은 단극 저항기/커패시터 쌍의 이득 및 위상 대비 주파수를 나타냅니다. 상단과 하단 플롯의 x축 주파수 범위는 1헤르츠(Hz)에서 10메가헤르츠(MHz)입니다. 상단 플롯의 y축 범위는 0데시벨(dB)에서 100dB이며 1Hz의 신호 값은 100dB입니다. 이 값은 100,000 x VIN의 이득 인자와 일치합니다. 파란색 곡선은 단극이 fP 또는 100Hz인 이득 응답이며, 여기서 R은 159킬로옴(kΩ)이고 C는 10나노패럿(nF)입니다.

주파수가 극 주파수(fP)를 넘어 증가함에 따라 파란색 곡선은 -20dB/10배수 단위 또는 -6dB/2배수 단위의 비율로 떨어집니다. 이 감쇠율은 기억해야 할 첫 번째 보데 플롯 경험 규칙입니다. 즉, 회로의 모든 극은 극 주파수에서 시작하여 -20dB/10배수 단위의 비율로 떨어집니다. 따라서 두 극이 동일한 주파수 범위에서 VOUT을 감쇠하는 경우 감쇠율은 -40dB/10배수 단위입니다.

그림 1 아래쪽 플롯은 이 단극 회로의 위상을 나타냅니다. 1Hz에서 R/C 네트워크의 위상은 0도(°)입니다. fP보다 10배수 전(또는 이 경우 10Hz)에서 단극 위상은 -90° 목표를 향해 -45°/10배수 단위씩 떨어지기 시작합니다.

극의 위상 응답에는 몇 가지 규칙이 적용됩니다. 극 회로에 대한 두 번째 보데 플롯 경험 규칙은 위상이 fP에서 -45°와 같다는 것입니다. 세 번째와 네 번째 보데 플롯 규칙은 감쇠 및 완료 위상 지점을 나타냅니다. 단극 위상은 극 주파수(fP)보다 10배수 단위 전에 떨어지기 시작하며, fP보다 10배수 단위 후에 -90°에서 마침내 안정됩니다.

단일 영점 보데 플롯

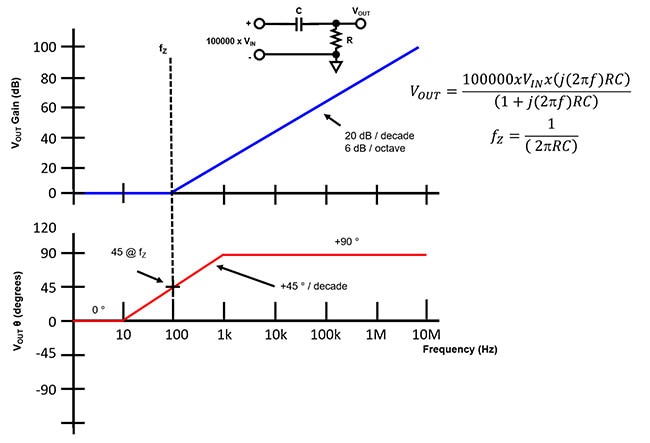

단일 영점 보데 플롯은 단일 극 보데 플롯의 반대 규칙을 반영합니다. DC VIN 전압을 막고 더 높은 주파수가 커패시터를 통과할 수 있도록 R과 C가 동일한 값으로 위치가 바뀝니다(그림 2).

그림 2: 크기와 위상 변이를 나타내는 단일 영점 보데 플롯입니다. (이미지 출처: Bonnie Baker)

그림 2: 크기와 위상 변이를 나타내는 단일 영점 보데 플롯입니다. (이미지 출처: Bonnie Baker)

주파수가 fZ를 넘어 증가하면 파란색 곡선이 +20dB/10배수 단위씩 증가합니다. 그림 2 아래쪽 플롯은 이 단일 영점 회로의 위상을 나타냅니다. fZ보다 10배수 전에 단일 영점 위상은 +90° 목표를 향해 +45°/10배수 단위의 비율로 증가하기 시작합니다. 영점 회로 위상은 fZ에서 +45°와 같습니다.

그림 1의 값을 요약하면 극 위치는 fP이며, fP 이후의 이득 크기는 -20dB/10배수 단위의 기울기를 가집니다. 위상은 fP를 통해 -45°/10배수 단위의 기울기를 가지며, 위상은 0.1x fP에서 감쇠를 시작하고 10 x fP에서 -90°로 안정됩니다. 그림 2의 값을 요약하면 영점 위치는 fZ이며, fZ 이후의 이득 크기는 +20dB/10배수 단위의 기울기를 갖습니다. 위상은 fZ를 통해 +45°/10배수 단위의 기울기를 가지며, 위상은 0.1 x fZ에서 감쇠를 시작하고 10 x fZ에서 +90°로 안정됩니다.

증폭기 개방 루프 보데 플롯

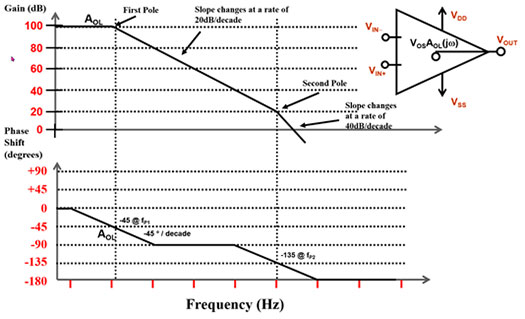

표준 연산 증폭기(op amp) 제품의 주파수 작동은 헤르츠 미만에서 0dB 차단 주파수까지의 전달 함수에서 다극과 영점을 가질 수 있습니다. 증폭기 보데 플롯이라고 예외는 없습니다. 규칙을 따르세요(그림 3).

그림 3: 크기와 위상 변이를 나타내는 연산 증폭기의 가능한 보데 플롯입니다. (이미지 출처: Bonnie Baker)

그림 3: 크기와 위상 변이를 나타내는 연산 증폭기의 가능한 보데 플롯입니다. (이미지 출처: Bonnie Baker)

그림 3은 전달 함수에 두 극(f1과 f2)이 있는 연산 증폭기 예시를 보여줍니다. 두 극을 사용할 경우 이득은 매번 -20dB/10배수 단위씩 떨어지며, 위상은 총 -180도까지 떨어집니다.

지금까지는 보데 플롯을 구성하는 방법에 대해 알아보았습니다. 이제 혼합된 피드백 시스템이 있는 실제 사례를 살펴보겠습니다.

폐쇄 루프 증폭기 시스템 안정성

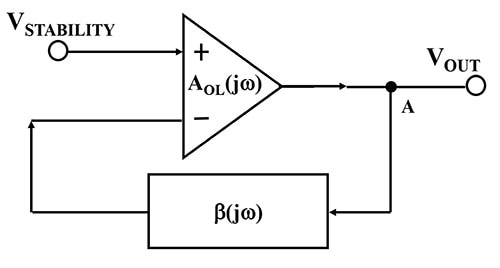

연산 증폭기 회로를 살피다 보면 항상 피드백 네트워크가 따라다닌다는 점을 발견하게 됩니다. 기본 연산 증폭기 피드백 네트워크에는 이득 순방향 소자(AOL(jω))와 피드백 소자(β(jω))가 있습니다.

그림 4: 피드포워드 소자(AOL(jω))와 피드백 소자(β(jω))가 있는 기본 연산 증폭기 피드백 네트워크입니다. (이미지 출처: Bonnie Baker)

그림 4: 피드포워드 소자(AOL(jω))와 피드백 소자(β(jω))가 있는 기본 연산 증폭기 피드백 네트워크입니다. (이미지 출처: Bonnie Baker)

그림 4에서 연산 증폭기(AOL)의 개방 루프 이득은 상대적으로 크며, 피드백 인자는 상대적으로 작습니다. 이 구성은 출력을 반전 단자로 다시 보내 음의 피드백 조건을 생성하며, 여기서 이 피드백이 출력을 제어하게 됩니다. 연산 증폭기 회로의 안정성을 판단하기 위해 β 또는 1/β의 역수를 사용하겠습니다.

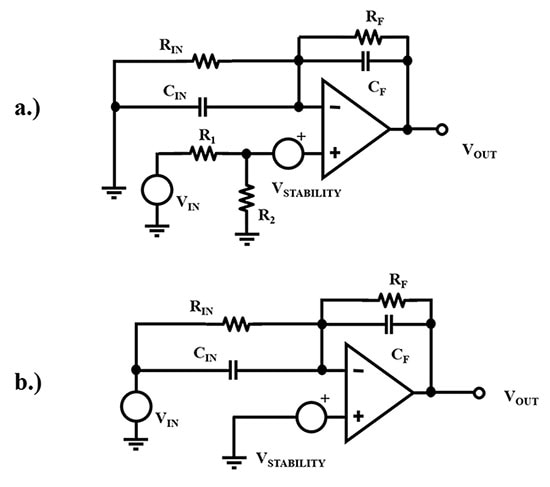

1/β을 계산하는 가장 쉬운 방법은 연산 증폭기의 비반전 입력에 VSTABILITY라는 소스를 배치하는 것입니다. 이 계산 전략은 회로의 안정성을 판단하는 훌륭한 방법을 제공합니다(그림 5).

그림 5: 비반전 연산 증폭기 회로 a.)와 반전 연산 증폭기 회로 b.) 둘 다 비반전 입력에 가상의 VSTABILITY 전압 소스가 있어 회로의 1/β 인자 또는 잡음 이득을 정확하게 계산할 수 있습니다. (이미지 출처: Bonnie Baker)

그림 5: 비반전 연산 증폭기 회로 a.)와 반전 연산 증폭기 회로 b.) 둘 다 비반전 입력에 가상의 VSTABILITY 전압 소스가 있어 회로의 1/β 인자 또는 잡음 이득을 정확하게 계산할 수 있습니다. (이미지 출처: Bonnie Baker)

그림 5의 회로를 살펴보면 비반전 단자에서 출력까지 피드백 회로가 동일하다는 것을 알 수 있습니다. VSTABILITY 전압 소스의 위치를 통해 회로의 1/β 인자 또는 잡음 이득을 정확하게 계산할 수 있습니다.

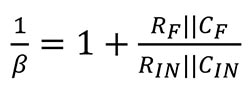

1/β 안정성 분석은 VSTABILTIY를 사용합니다. 연산 증폭기 개방 루프 이득이 무한하다고 가정할 경우 두 회로의 전달 함수는 다음과 같습니다.

방정식 1

방정식 1

방정식 2

방정식 2

방정식 3

방정식 3

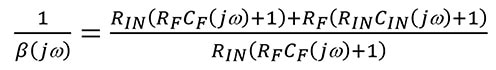

방정식 3의 주파수 구성요소 jω가 0일 때 다음과 같습니다.

방정식 4

방정식 4

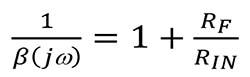

jω가 방정식 3에서 무한대에 가까워질 때 다음과 같습니다.

방정식 5

방정식 5

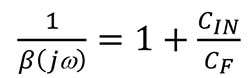

1/β의 영점 주파수(fZ)와 극 주파수(fP)는 다음과 같습니다.

방정식 6

방정식 6

방정식 7

방정식 7

위 규칙을 지키는 1/β 안정성 분석 곡선의 보데 플롯은 그림 6에 나와 있습니다.

그림 6: 그림 5 a.)와 b.)에 대한 1/β 주파수 응답은 동일합니다. 영점은 더 낮은 주파수에서 발생하고 극은 더 높은 주파수에서 발생합니다. (이미지 출처: Bonnie Baker)

그림 6: 그림 5 a.)와 b.)에 대한 1/β 주파수 응답은 동일합니다. 영점은 더 낮은 주파수에서 발생하고 극은 더 높은 주파수에서 발생합니다. (이미지 출처: Bonnie Baker)

그림 6은 연산 증폭기 회로의 1/β 또는 잡음 이득의 주파수와 위상 응답을 나타냅니다. 이 그림은 방정식 4~7을 그래프 형식으로 요약한 것입니다. 방정식 4와 5는 DC 이득과 ¥ 이득을 포함하여 정의하며, 방정식 6과 7은 회로의 영점과 극을 포함하여 식별합니다. 그림 3과 6은 시스템의 전달 함수 및 극과 영점의 위치를 정의하여 연산 증폭기 회로의 안정성을 설정하는 첫 번째 단계를 제공합니다. 마지막 단계는 그림 3과 6을 한 그래프로 중첩하는 것입니다.

시스템 안정성 판단

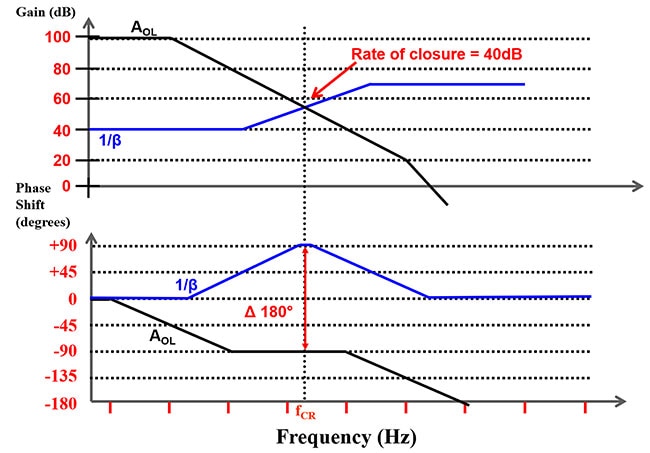

개방 루프와 폐쇄 루프 이득의 교차 또는 근접률은 회로의 위상 변이를 정의합니다. 일반적으로 30dB 이하의 근접률은 안정적인 회로를 나타냅니다. 30dB보다 큰 근접률일 경우 회로 상태가 불안정해집니다(그림 7).

그림 7: 중첩된 연산 증폭기의 AOL 이득 및 위상 응답과 1/β 이득 및 위상 응답입니다. (이미지 출처: Bonnie Baker)

그림 7: 중첩된 연산 증폭기의 AOL 이득 및 위상 응답과 1/β 이득 및 위상 응답입니다. (이미지 출처: Bonnie Baker)

그림 7에서 AOL과 1/β 이득 곡선 사이의 근접률은 40dB과 같습니다. 40dB 근접률은 135°보다 큰 위상 변이를 나타내며, 이는 불안정한 회로를 의미합니다. 이 구성에서 180°의 근접률은 발진 회로를 생성합니다.

위 문제에 대한 해결책이 많이 있습니다. 저항값 또는 정전 용량 값은 극 주파수와 영점 주파수를 이동하여 변경할 수 있습니다. 또 다른 대안은 다른 연산 증폭기를 선택하는 것입니다(그림 8).

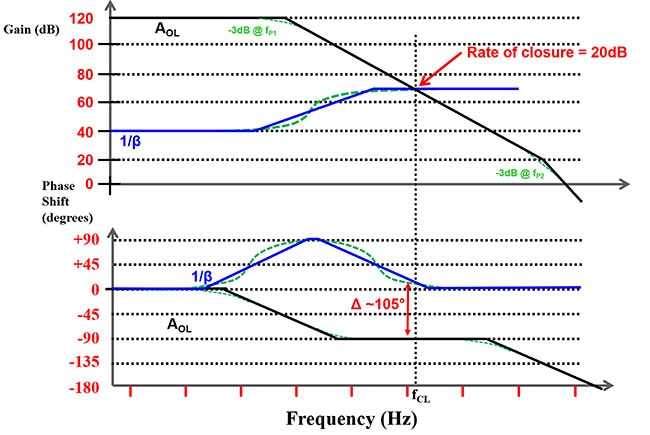

그림 8: 영점 주파수와 극 주파수를 변경하지 않고 그림 7의 연산 증폭기보다 높은 대역폭의 연산 증폭기를 사용합니다. (이미지 출처: Bonnie Baker)

그림 8: 영점 주파수와 극 주파수를 변경하지 않고 그림 7의 연산 증폭기보다 높은 대역폭의 연산 증폭기를 사용합니다. (이미지 출처: Bonnie Baker)

그림 8에서 연산 증폭기 대역폭은 1/β 네트워크를 변경하지 않고도 두 10배수 단위 정도 더 높습니다. 녹색 점선은 실제 계산을 반영하며 보다 현실적인 보데 플롯을 제공합니다. 증폭기 대역폭이 증가하면 근접률이 40dB에서 20dB로 변합니다. 그 결과 위상 변이는 이제 약 105°가 되어 안정적인 회로를 나타냅니다.

그림 8의 녹색 점선은 실제 응답을 포함함으로써 연필과 자로 그린 보데 플롯보다 정확한 결과를 제공합니다.

회로의 이득과 위상 측정

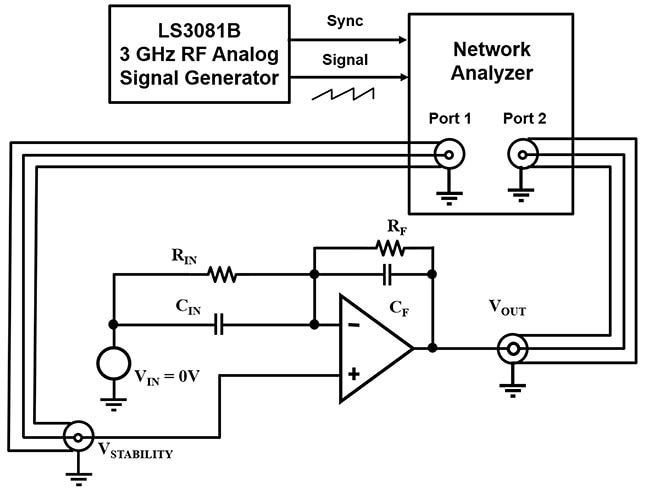

증폭기 회로의 이득과 위상을 측정하려면 네트워크 분석기와 함께 입력 신호를 제공하는 함수 생성기가 필요합니다(그림 9). 대표적으로 Tabor Electronics LS3081B 3GHz RF 아날로그 스윕 함수 생성기가 있습니다.

그림 9: 그림 5 b.)에 있는 반전 증폭기 회로의 이득과 위상 측정 구성입니다. (이미지 출처: Bonnie Baker)

그림 9: 그림 5 b.)에 있는 반전 증폭기 회로의 이득과 위상 측정 구성입니다. (이미지 출처: Bonnie Baker)

그림 9에서 함수 생성기의 입력 신호는 포트 1에서 VSTABILITY 노드로 적용됩니다. 신호는 증폭기 회로를 통해 회로 출력(VOUT)으로 전파되며, 여기서 네트워크 분석기는 포트 2의 신호를 캡처하여 함수 생성기의 포트 1 신호와 비교합니다.

결론

안정적인 연산 증폭기 회로를 설계할 때 보데 플롯은 키트에 포함할 만한 매우 유용한 도구입니다. 보데 플롯의 유용성은 증폭기 개방 루프 이득과 피드백 네트워크 사이의 근접률이 회로의 안정성을 빠르게 정의하는 다극 회로와 다중 영점 회로를 살펴볼 때 분명해집니다.

1차 극과 영점 회로의 위상 대비 이득을 추정하기 위해 그래프용지에 직선 자를 사용하는 간단한 방법을 보여주는 본 블로그는 보데 플롯 사용을 마스터하는 데 도움이 될 수 있지만, 가장 좋은 학습 방법은 연습입니다. 다시 말씀드리지만, 온라인 DigiKey Innovation Handbook(DigiKey 혁신 핸드북)의 관련 자료에서 인쇄 가능한 버전의 보데 플롯 그래프를 다운로드하여 시작할 수 있습니다.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum