아날로그 기본 사항 - 5부: SAR ADC의 까다로운 입력 구동 문제 해결

DigiKey 북미 편집자 제공

2020-10-28

편집자 주: 아날로그-디지털 컨버터(ADC)는 아날로그 환경을 디지털 환경에 연결하므로 실제 환경에 연결되는 모든 전자 시스템의 기본 부품입니다. 또한 시스템의 성능을 결정하는 주요 요소입니다. 이 시리즈에서는 ADC의 기본 사항, 다양한 유형 및 응용 분야를 살펴봅니다. 아날로그 기본 사항에 관한 이 시리즈의 1부에서는 SAR ADC를 설명했고, 2부에서는 델타 시그마 컨버터에 대해 논의했으며, 3부에서는 파이프라인 ADC를 살펴보았습니다. 4부에서는 델타 시그마 ADC가 어떻게 매우 낮은 잡음 결과를 도출하는지 알아봅니다. 5부에서는 SAR ADC의 까다로운 입력 구동 문제를 살펴봅니다.

많은 데이터 취득, 산업 제어 및 계측 응용 분야는, 연속 근사화 레지스터(SAR) 컨버터가 매우 적합한 경우 초고속 아날로그-디지털 컨버터(ADC)를 필요로 합니다. 그러나 성공적인 변환 결과를 보장하기 위해서는 SAR 컨버터 주변의 외부 회로망의 역할도 확인하는 것이 중요합니다. SAR 컨버터에 있어 특별한 주의가 필요한 중요한 단자는 아날로그 신호 입력입니다. 이러한 입력 핀을 방치하면 안정성 문제와 용량성 전하 '킥백'이 발생하여 변환 오류 및 긴 신호 취득 시간을 초래할 수 있습니다.

SAR 컨버터 응용 제품을 위한 정밀한 입력 신호 제어 솔루션은 연산 증폭기(op-amp)의 구동에 있습니다. 적절한 출력 저항기 및 커패시터 값으로 지원되는 이러한 장치는 고해상도, 16비트 및 20비트 SAR 컨버터 시스템을 위한 고정밀의 강력한 솔루션 기반입니다.

이 기사에서는 안정적이고 정밀한 SAR ADC 변환과 관련한 문제를 간략하게 살펴봅니다. 그런 다음 SAR ADC를 구동하기 위한 적절한 연산 증폭기를 소개하고 필요한 입력 구동기 회로를 구현하는 방법을 보여줍니다. 예제에서는 Analog Devices의 솔루션을 사용합니다.

SAR ADC 입력 회로망

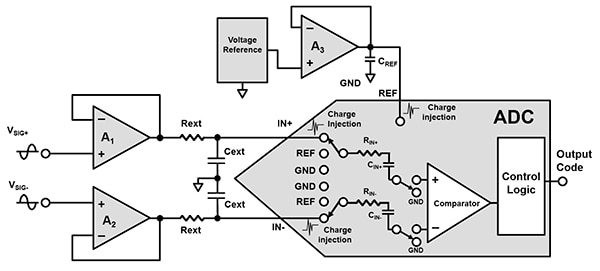

SAR ADC 구동기 회로에는 신호 발생기에서 ADC를 분리하는 연산 증폭기(A1 및 A2)가 있습니다(그림 1). 이 회로에서 Rext는 ADC 용량성 부하(CIN+ 및 CIN-) 및 Cext에서 증폭기의 출력 단계를 '분리'하여 증폭기를 안정적으로 유지합니다. Cext 및 CREF는 IN+, IN- 및 REF 입력 단자로부터 스위칭 전하 주입을 흡수하는 거의 완벽한 입력 소스를 ADC에 제공합니다. 입력 단자(IN+, IN-)는 컨버터의 취득 시간 동안 입력 신호(VSIG+, VSIG-)의 전압을 추적하여 ADC의 입력 샘플링 커패시터 CIN+ 및 CIN-에 전하를 제공합니다.

그림 1: 이 회로에서 Rext는 연산 증폭기 출력 단계에서 Cext를 '분리'합니다. Cext 및 CREF는 샘플링 기간 동안 차동 SAR ADC를 위한 전하 저장소를 제공합니다. (이미지 출처: DigiKey)

그림 1: 이 회로에서 Rext는 연산 증폭기 출력 단계에서 Cext를 '분리'합니다. Cext 및 CREF는 샘플링 기간 동안 차동 SAR ADC를 위한 전하 저장소를 제공합니다. (이미지 출처: DigiKey)

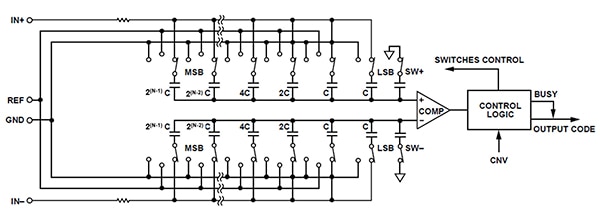

예를 들어 Analog Devices의 AD7915(16비트) 및 AD4021(20비트) SAR ADC를 사용하는 ADC의 내부를 살펴보면, 전하 재분배 디지털-아날로그 컨버터(DAC)가 사용되는 것을 알 수 있습니다. 정전 용량 DAC에는 2개의 동일한 이진 가중치 커패시터 어레이가 있습니다. 이러한 어레이는 비반전 및 반전 비교기 입력에 연결됩니다(그림 2).

그림 2: SAR ADC의 단순화된 AD7915 및 AD4021 기반 회로도입니다. 여기서 N은 컨버터 비트 수입니다. (이미지 출처: Analog Devices의 원본 자료를 DigiKey에서 수정함)

그림 2: SAR ADC의 단순화된 AD7915 및 AD4021 기반 회로도입니다. 여기서 N은 컨버터 비트 수입니다. (이미지 출처: Analog Devices의 원본 자료를 DigiKey에서 수정함)

취득 단계에서 입력(IN+ 및 IN-)은 정전 용량 어레이로 전환됩니다. 또한 SW+ 및 SW-가 닫히고 최하위 비트(LSB) 커패시터를 접지(GND)에 연결합니다. 이 상태에서 커패시터 어레이는 샘플링 커패시터가 되어 IN+ 및 IN- 아날로그 신호를 취득합니다. 취득 단계가 완료되면 제어 논리(오른쪽)에 대한 CNV 입력이 높아져 변환 단계가 시작됩니다.

변환 단계는 SW+ 및 SW-를 개방하고 두 커패시터 어레이를 GND로 전환하는 것으로 시작됩니다. 이 구성에서 캡처된 IN+ 및 IN- 차동 전압으로 인해 비교기가 불균형 상태가 됩니다. 전하 재분배 DAC는 GND와 REF 사이에서 커패시터 어레이의 각 소자를 최상위 비트(MSB)에서 LSB로 체계적으로 전환합니다. 비교기 입력은 이진 가중치 전압 단계(VREF/2N-1, VREF/2N-2… VREF/4, VREF/2)에 따라 다릅니다. 제어 논리는 MSB에서 LSB로 스위치를 토글하여 비교기를 균형 상태로 되돌립니다. 이 과정이 완료되면 ADC는 취득 단계로 돌아가고 제어 논리는 ADC 출력 코드를 생성합니다.

입력 전하 주입, 회로 안정성 및 AD7915 ADC 구동

변환 과정에서 가장 중요한 부분은 정확한 입력 신호 전압을 취득하는 것입니다. ADC 데이터 변환 과정은 구동 증폭기가 입력 커패시터 CIN+ 및 CIN-를 정확히 충전하는 경우 원활히 실행되며 ADC 취득 시간이 끝날 때까지 안정성을 유지합니다. 설계자의 문제는 구동 증폭기를 관리할 때 ADC의 입력 단자가 정전 용량(CIN+, CIN-)뿐 아니라 스위칭 노이즈 또는 "킥백" 전하 주입을 도입한다는 것입니다.

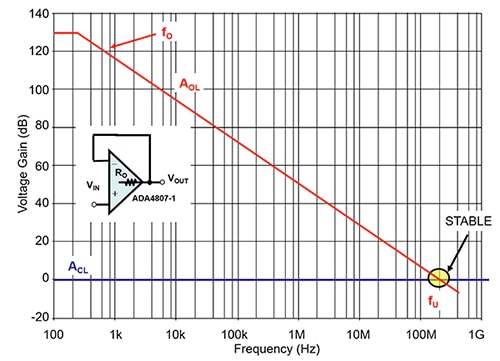

증폭기 회로 보데 플롯은 회로의 안정성을 빠르게 예측합니다. 보데 플롯 도구는 증폭기의 개방 루프 및 시스템 폐루프 이득 전달 함수의 크기를 근사화합니다(그림 3).

그림 3: 그림 1에 표시된 증폭기의 개방 및 폐루프 전달 함수(증폭기 부하로 Rext와 Cext 및 다음 SAR ADC 없음). (이미지 출처: DigiKey)

그림 3: 그림 1에 표시된 증폭기의 개방 및 폐루프 전달 함수(증폭기 부하로 Rext와 Cext 및 다음 SAR ADC 없음). (이미지 출처: DigiKey)

y축은 증폭기 회로의 증폭기 개방 루프 이득(AOL)과 폐루프 이득(ACL)을 정량화합니다. 증폭기의 AOL 곡선은 130dB에서 시작하고 폐루프 이득 ACL은 0dB과 같습니다. x축의 단위는 100Hz에서 1GHz까지의 개방 및 폐루프 이득 주파수를 대수적으로 정량화합니다.

그림 3에서 약 220Hz(fO)에서 증폭기의 DC 개방 루프 이득은 130dB부터 -20dB/decade의 속도로 점점 감소됩니다. 주파수가 증가함에 따라 이 감쇠율은 약 180MHz에서 0dB을 넘어서도 계속됩니다. 이 곡선은 단극 시스템을 나타내므로 교차 주파수 fU는 단위 이득 안정적 증폭기의 이득 대역폭 곱(GBWP)과 같습니다. 이 플롯은 AOL 및 ACL 폐쇄율이 20dB/decade이므로 안정적인 시스템임을 나타내고 있습니다.

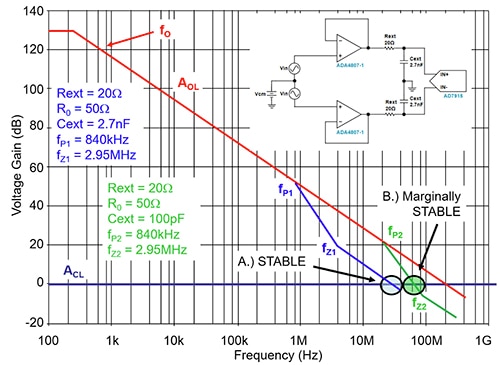

Rext 및 Cext와 SAR ADC를 추가하면 시스템 제로 및 폴을 생성하여 증폭기 회로가 수정됩니다(그림 4). 이 시스템은 Analog Devices의 16비트, 초당 1메가샘플(MSPS) AD7915 차동 PulSAR ADC 및 180MHz, 레일 투 레일 입출력 ADA4807-1 증폭기로 구성됩니다. 증폭기와 ADC를 결합하려면 30피코패러드(pF)(통상) ADC 입력 용량성 부하로 인해 Rext가 필요합니다. 또한 이 회로에서는 Cext가 전하 버킷 역할을 하여 ADC 입력에서 충분한 전하를 제공해야 입력 전압과 정확히 일치됩니다.

그림 4: 두 개의 개별 Rext/Cext 쌍으로 AD7915 SAR ADC를 구동하는 두 개의 ADA4807 연산 증폭기에 대한 보데 플롯 응답이 표시됩니다. fP1 및 fZ1 코너 주파수는 증폭기의 개방 루프 이득을 수정하여 안정적인 시스템 응답을 생성합니다. fP2 및 fZ2 코너 주파수는 증폭기의 개방 루프 이득을 수정하여 약간 안정적인 응답을 생성합니다. (이미지 출처: DigiKey)

그림 4: 두 개의 개별 Rext/Cext 쌍으로 AD7915 SAR ADC를 구동하는 두 개의 ADA4807 연산 증폭기에 대한 보데 플롯 응답이 표시됩니다. fP1 및 fZ1 코너 주파수는 증폭기의 개방 루프 이득을 수정하여 안정적인 시스템 응답을 생성합니다. fP2 및 fZ2 코너 주파수는 증폭기의 개방 루프 이득을 수정하여 약간 안정적인 응답을 생성합니다. (이미지 출처: DigiKey)

그림 4의 회로는 초기 취득이 발생할 때 ADC의 용량성 부하와 ADC의 스위칭 전하 주입으로 인해 진동이 있을 수 있습니다. Rext/Cext 증폭기 출력 구성 요소에 의해 생성된 추가 극 및 제로는 안정적인 시스템을 보장하므로 개방 및 폐루프 이득 곡선 교차가 20dB/decade 이상이고 위상 마진이 45° 미만이 됩니다. fP2 및 fZ2를 사용하는 이 구성은 불안정한 회로를 생성합니다.

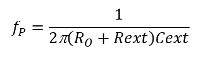

불안정성을 방지하려면, 회로에서 Rext 및 Cext를 사용해 증폭기의 개방 루프 이득 곡선을 평가할 때 설계자가 증폭기의 개방 루프 출력 저항 및 RO에 미치는 영향을 포함시켜야 합니다. RO(50옴(W)), Rext 및 Cext의 조합은 1극(fP, 방정식 1)과 1개의 0(fZ, 방정식 2)을 대입하여 개방 루프 응답 곡선을 수정합니다. RO, Rext 및 Cext 값은 fP의 코너 주파수를 결정합니다. Rext 및 Cext 값은 제로 코너 주파수 fZ를 결정합니다.

방정식 1

방정식 1

방정식 2

방정식 2

fP 및 fZ 계산은 다음과 같습니다

fP1 = 842kHz

fZ1 = 2.95MHz

값: RO = 50W

Rext = 20W

Cext = 2.7나노패럿(nF)

fP2 = 22.7MHz

fZ2 = 79.5MHz

값: RO = 50W

Rext = 20W

Cext = 0.1nF

위에 표시된 fP1 및 fZ1 값은 AD7915 및 ADA4807-1을 위한 안정적인 시스템을 제공합니다.

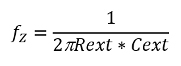

Easy Drive AD4021 SAR ADC 구동

AD7915에 대한 대안으로 AD4021 20비트 1MSPS Easy Drive SAR 컨버터가 있습니다. AD4021 장치 제품군은 입력 킥백 및 입력 전류를 0.5μA/MSPS로 크게 줄입니다. Easy Drive는 전력 소비를 감소시키며 신호 체인의 복잡성을 줄입니다.

AD4021의 아날로그 입력에는 일반 전환식 커패시터 SAR 입력 비선형 전하 킥백을 줄이는 회로망이 있습니다. 킥백 감소와 긴 취득 단계를 통해 더 낮은 대역폭과 더 낮은 전력 구동 증폭기를 사용할 수 있습니다(그림 5).

그림 5: AD4021의 입력 회로망 및 취득 타이밍은 킥백 스위칭 전류를 줄이고 구동 증폭기의 엄격한 요구 사항을 완화합니다. (이미지 출처: Analog Devices)

그림 5: AD4021의 입력 회로망 및 취득 타이밍은 킥백 스위칭 전류를 줄이고 구동 증폭기의 엄격한 요구 사항을 완화합니다. (이미지 출처: Analog Devices)

또한 킥백 감소와 더 긴 취득 시간의 조합으로 인해 입력 저항기 커패시터(RC) 필터 및 그에 상응하는 더 작은 Cext 커패시터에서 더 큰 Rext 저항 값을 허용합니다. 더 작은 Cext 증폭기 부하의 이러한 조합은 안정성을 향상시키고 전력 손실을 낮춥니다.

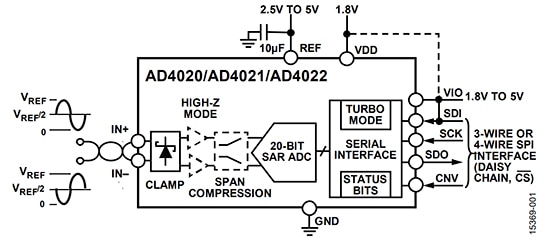

단일 5V 공급 장치를 사용하는 AD4021에 권장되는 연결 구성도는 유사한 회로 구성도를 갖추고 있는 것으로 보이지만, 증폭기 요구 사항이 완화되며 Rext/Cext(R 및 C) 값이 더 작습니다(그림 6).

그림 6: 이전에 논의한 AD7915 구동에 비해 증폭기 요구 사항이 더 완화되고 더 큰 Rext 값을 가진 단일 5V 공급 장치로 구동되는 일반적인 AD4021 및 ADA4807-1 응용 제품 구성도. (이미지 출처: Analog Devices)

그림 6: 이전에 논의한 AD7915 구동에 비해 증폭기 요구 사항이 더 완화되고 더 큰 Rext 값을 가진 단일 5V 공급 장치로 구동되는 일반적인 AD4021 및 ADA4807-1 응용 제품 구성도. (이미지 출처: Analog Devices)

그림 6에서 SAR 기반 AD4021도 전하 재분배 샘플링 DAC를 사용합니다. ADC에는 온보드 변환 클록과 직렬 클록이 있습니다. 결과적으로 변환 과정에는 동기식 클록(SCK) 입력이 필요하지 않습니다. 이 클록 구성을 사용하면 취득 시간을 늘릴 수 있으므로 입력 신호가 최종 값으로 안정화되는 데 더 많은 시간을 제공함으로써 정확도가 향상됩니다.

AD7915 및 AD4021용 구동 증폭기의 주요 고려 사항은 잡음입니다. 증폭기/Rext/Cext 조합은 AD7915의 경우 전체 단계에서 16비트 수준(0.0015%, 15ppm)으로, AD4021의 경우 20비트 수준(0.00001%, 1ppm)으로 안정화되어야 합니다.

AD7915 및 AD4021의 신호 대 잡음(SNR) 성능을 보존하려면 구동 증폭기 잡음이 ADC 잡음의 1/3 미만이어야 합니다. AD4021 잡음은 60mVrms이므로 증폭기/Rext/Cext 조합이 20mVrms 미만이어야 합니다. AD4021 잡음은 31.5mVrms이므로 증폭기/Rext/Cext 조합이 10.5mVrms 미만이어야 합니다.

Analog Devices의 정밀 ADC 구동기 도구는 설계자가 올바른 Rext 및 Cext 값을 빠르게 계산할 수 있도록 지원합니다. 이 도구는 선택된 구동기와 ADC를 사용하여 회로의 정착 시간, 잡음 및 왜곡 동작을 모델링합니다.

결론

SAR ADC는 초고속 데이터 획득, 산업 제어 및 계측 응용 분야에서 가장 본질적인 요소입니다. 그러나 이러한 장치의 외부 입력 회로망(구동 증폭기 및 입력 필터)에는 잠재적인 스위칭 전하 주입 및 증폭기 안정성 문제를 수용하기 위한 특별한 고려사항이 요구됩니다.

AD7916 및 AD4021과 같은 대부분의 SAR 컨버터를 위한 정밀 입력 신호 제어 솔루션은 연산 증폭기 구동기(이 경우 ADA4807-1)에 있습니다. 위에서 설명한 대로, 적절한 출력 저항 및 커패시터 값으로 지원되는 이러한 장치는 고정밀, 견고성, 고해상도, 16비트 또는 20비트 SAR 컨버터 시스템 구축을 위한 견고한 기반을 형성합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.