아날로그 기본 사항 - 4부: 낮은 잡음을 위한 델타 시그마 ADC 최적화

DigiKey 북미 편집자 제공

2020-08-05

편집자 주: 아날로그 디지털 컨버터(ADC)는 아날로그 환경을 디지털 환경에 연결하므로 실제 환경에 연결되는 모든 전자 시스템의 기본 부품입니다. 또한 시스템의 성능을 결정하는 주요 요소입니다. 이 시리즈에서는 ADC의 기본 사항, 다양한 유형 및 응용 분야를 살펴봅니다. 아날로그 기본 사항에 관한 이 시리즈의 1부에서는 SAR ADC를 설명했고, 2부에서는 델타 시그마 컨버터에 대해 논의했으며, 3부에서는 파이프라인 ADC를 살펴보았습니다. 이제 4부에서는 델타 시그마 ADC로 초저잡음 결과를 생성할 수 있는 방법을 보여줍니다. 5부에서는 SAR ADC에 대해 어려운 입력 구동 문제를 살펴봅니다.

델타 시그마(ΔƩ) 집적 회로 토폴로지는 공정 제어, 정밀 온도 측정 및 계량 저울 응용 제품을 위한 고분해능 고집적 저전력 솔루션을 렌더링하여 아날로그 디지털 컨버터(ADC)에 계속해서 표시됩니다.

의아하게도 이 컨버터 유형은 5V 시스템의 2V(VRMS) 잡음에 해당하는 7.78dB의 이론적 신호 대 잡음비(SNR)로 1비트 변환을 시작합니다. 여기서 ADC는 5V 시스템의 244nV rms 잡음에 해당하는 146dB의 이론적 SNR을 제공하는 진정한 24비트 델타 시그마 컨버터로 성장할 수 있습니다.

1비트에서 24비트로의 이 급격한 분해능 상승에서는 오버샘플링 알고리즘, 잡음 형상 변조기 및 디지털 필터를 사용하여 양자화 잡음을 줄이고 SNR을 높입니다. 증폭기 입력 스테이지를 사용하는 대신 12비트 또는 16비트 연속 근사화 레지스터(SAR) ADC에 공급하여 ΔƩ 컨버터와 관련 잡음의 복잡성을 방지할 수 있는 방법이 있습니다. 이 설계 경로는 작동하지만, pc 기판에 더 많은 집적 회로가 필요하고 BOM이 증가합니다.

잡음 문제를 해결하는 데 효과적인 방법이 있습니다. 즉, 초저잡음 ΔƩ ADC로 정면으로 부딪쳐서 해결하는 것입니다.

이 기사에서는 저잡음 대상 응용 분야를 간략하게 설명하고 ΔƩ ADC가 이 요구 사항을 해결하기 위해 내부적으로 어떻게 설계되었는지를 보여줍니다. 그런 다음 각각 24비트 정밀도와 32비트 정밀도를 강조하는 Texas Instruments의 두 개 ΔƩ ADC를 소개하고 이 두 ADC에서 강력한 디지털 필터링을 활용하는 방법을 보여줍니다.

ΔƩ ADC 적합 분야

아날로그의 관점에서 엔지니어는 온도, 압력, 로드 셀 및 광학 센서의 출력을 다양한 정확도로 측정해야 합니다. 기본적으로 증폭기는 대부분의 경우 DC에 근접한 이 작은 아날로그 발생을 정량화할 수 있도록 엔지니어의 역량을 강화합니다. 점진적인 디지털화로 관점과 역량이 변화되고, 센서 신호를 저장 및 수정할 수 있는 능력이 개선되었습니다.

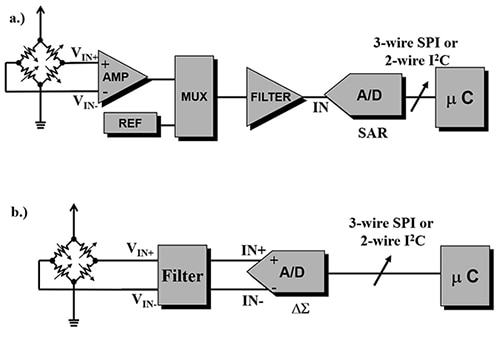

디지털 캡처와 관련한 일반적인 센서 신호 경로는 센서에서 시작하여 이득, 다중화, 필터 스테이지를 거쳐 ADC로 진행됩니다(그림 1a).

그림 1: 센서 신호를 디지털화하는 두 기술에서는 SAR ADC 또는 ΔƩ ADC를 사용합니다. 고분해능 회로에서 SAR ADC는 증폭 및 5차 능동 필터가 필요하고, ΔƩ ADC는 프런트 엔드 아날로그 1차 수동 필터가 필요합니다. (이미지 출처: A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

그림 1: 센서 신호를 디지털화하는 두 기술에서는 SAR ADC 또는 ΔƩ ADC를 사용합니다. 고분해능 회로에서 SAR ADC는 증폭 및 5차 능동 필터가 필요하고, ΔƩ ADC는 프런트 엔드 아날로그 1차 수동 필터가 필요합니다. (이미지 출처: A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

그림 1a의 컨버터는 12비트에서 18비트로 변환 가능하고 최대 10MSPS 변환 속도로 실행할 수 있는 SAR ADC입니다. 16비트 컨버터는 216개 또는 65,536개의 세그먼트를 제공합니다. 5V 시스템에서 최하위 비트(LSB)는 98dB의 이론적 SNR에서 5V/216298 또는 76.3mV입니다. SAR 컨버터보다 먼저 아날로그 이득을 실행하여 더 높은 세분성을 실현할 수 있습니다.

ΔƩ 신호 체인(그림 1b)은 단일 컨버터를 탑재한 신호 체인의 분해능을 개선하고 BOM을 줄입니다. ΔƩ ADC는 16비트를 32비트로 변환할 수 있습니다. 이 신호 체인에서 24비트 ΔƩ ADC는 224 또는 16,777,216개의 세그먼트를 제공합니다. 따라서 5V 시스템에서 LSB는 146dB의 이론적 SNR에서 5V/224 또는 298nV입니다. 이 분해능 수준에서 센서의 용량에 근접한 컨버터 세분성을 제공합니다.

내부 디지털 필터의 경우 필터링 계산을 구현하는 데 시간이 필요하기 때문에 24비트 ΔƩ ADC는 더 느립니다. 이 컨버터의 통상 출력 데이터 전송률 범위는 수 Hz에서 1MSPS까지입니다. 이제 아날로그 필터는 복잡한 3개 연산 증폭기, 5차 아날로그 필터 대신 경제적인 1차 저항기 커패시터(RC) 필터를 사용합니다.

이 두 접근 방식의 잡음 차이는 명확합니다. ΔƩ ADC의 저잡음이 SAR ADC의 저잡음보다 우수합니다(표 1).

*참고: SNR = 6.02N + 1.76, 여기서 N은 비트 수입니다.

|

표 1: 16비트 SAR ADC 및 24비트 ΔƩ ADC의 전체 범위 입력 전압이 5V일 때 ADC 세그먼트, LSB 및 이론적 SNR (데이터 출처: DigiKey)

ΔƩ ADC는 속도 사양은 중요하지 않고 정확도가 가장 중요한 온도, 압력, 로드 셀과 같은 센서 응용 분야를 위한 우수한 솔루션을 제공합니다. 이 ADC는 아날로그 잡음 감소 기술 대신 디지털을 사용하여 작은 전압 값으로 변환할 수 있습니다.

ΔƩ ADC 내부

ΔƩ ADC의 내부는 80% 디지털화되었습니다. 일반적으로 이 컨버터는 입력 신호를 수신한 다음 해당 아날로그 신호를 디지털로 즉시 변환합니다. 그런 다음 해당 디지털 신호를 디지털 필터 스테이지로의 후속 변조기 변환과 결합합니다. 여기서 누적된 1비트 신호가 여러 개의 비트로 변경됩니다. 그런 다음 디지털 출력 스테이지를 통해 최종 다중 비트 변환을 대기 중인 마이크로 컨트롤러에 직렬로 전송합니다.

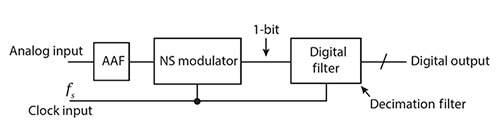

아날로그 신호는 먼저 외부 1차 안티앨리어싱 필터(AAF)를 통과합니다. 그러면 잡음 형상(NS) 변조기에서 아날로그 신호를 수신하고 컨버터의 클록 속도로 1비트 스트림을 생성하여 디지털 필터로 보냅니다(그림 2).

그림 2: 일반 ΔƩ에서는 1차 AAF를 통해 아날로그 신호를 수신하고 NS 변조기를 사용하여 1비트 스트림을 생성한 후 마이크로 컨트롤러에 대한 디지털 출력에서 다중 비트 결과를 생성합니다. (이미지 출처: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

그림 2: 일반 ΔƩ에서는 1차 AAF를 통해 아날로그 신호를 수신하고 NS 변조기를 사용하여 1비트 스트림을 생성한 후 마이크로 컨트롤러에 대한 디지털 출력에서 다중 비트 결과를 생성합니다. (이미지 출처: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

디지털 필터는 1비트 스트림에서 여러 코드를 클로킹하고 디지털 필터의 전체 다중 비트 결과를 생성합니다. 다중 비트 결과는 디지털 출력을 통해 직렬로 전송됩니다.

ΔƩ 변조기

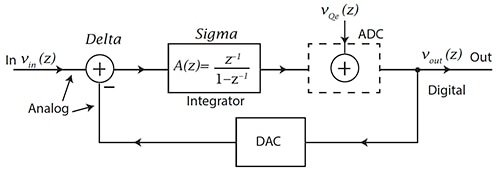

적분기/피드백 루프 수에 따라 ΔƩ 변조기의 차수가 결정됩니다. 1차 ΔƩ ADC 변조기에는 단일 적분기 및 피드백 루프가 있습니다(그림 3).

그림 3: 아날로그 적분기가 하나이고 피드백 루프에 1비트 ADC 및 DAC가 있는 1차 변조기 VQe(z)는 양자화 ADC 잡음입니다. (이미지 출처: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

그림 3: 아날로그 적분기가 하나이고 피드백 루프에 1비트 ADC 및 DAC가 있는 1차 변조기 VQe(z)는 양자화 ADC 잡음입니다. (이미지 출처: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

그림 3에서 아날로그 신호(VIN(z))가 변조기의 델타(Δ) 부분으로 수신됩니다. 그런 다음 아날로그 신호는 적분기 스테이지 또는 시그마(Ʃ) 스테이지를 통과하여 fS의 샘플링 속도(그림 2에 따라)로 1비트 ADC(비교기)로 이동합니다. 이 클로킹된 디지털 신호는 이제 1비트 디지털 아날로그 컨버터(DAC)에 다시 공급되고 Δ 스테이지에서 VOUT(z)로 전달됩니다. 1비트 DAC는 아날로그 입력 신호 VIN(z)에서 뺄 아날로그 전압을 제공합니다. 이 1차 변조기의 전달 함수는 다음과 같습니다.

![]() 방정식 1

방정식 1

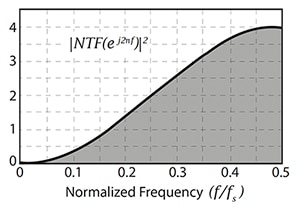

적분기와 피드백 루프로 인해 변조기는 변조기의 디지털 출력 데이터 스트림에 대해 잡음 형상 알고리즘을 구현합니다(그림 4).

그림 4: ΔƩ 변조기 출력의 잡음 형상 함수에서 잡음 전달 함수(NTF)는 1-z-1이고, 0.5 정규화 주파수는 FS/2입니다. (이미지 출처: Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

그림 4: ΔƩ 변조기 출력의 잡음 형상 함수에서 잡음 전달 함수(NTF)는 1-z-1이고, 0.5 정규화 주파수는 FS/2입니다. (이미지 출처: Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

그림 4에서 잡음 형상 특성은 변환 1비트 양자화 잡음을 줄이기 위한 첫 번째 단계입니다. 잡음이 더 높은 주파수로 전달되면 저역 통과 디지털 필터가 잡음 감소 공정을 완료합니다.

고차원 변조기에는 추가 적분기와 피드백 루프가 포함되어 있습니다. 예를 들어 3차 변조기에는 3개의 적분기와 3개의 피드백 루프가 있습니다. DC 주변 잡음을 줄이고 형상 잡음을 높이면 변조기 차수에 따라 잡음 형상 함수가 변경됩니다.

고차원 변조기의 경우 실리콘 하드웨어를 추가하면 성능은 향상되지만 안정성과 신호 범위가 감소합니다.

ΔƩ 디지털 필터

ΔƩ ADC는 오버샘플링(OS)을 사용하여 작동합니다. 오버샘플링은 방정식 2에 따라 ADC 출력 데이터 전송률(FD)에 대한 변조기의 샘플링 속도 비율(FS)입니다.

![]() 방정식 2

방정식 2

오버샘플링은 저역 통과 디지털 필터를 통해 잡음 형상 데이터의 디지털 대역폭을 제한하여 ΔƩ ADC 잡음을 개선합니다.

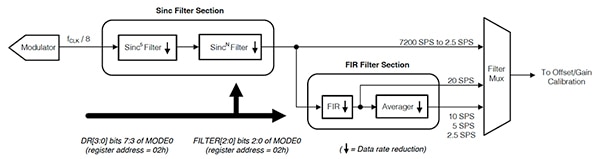

ΔƩ ADC에서 일반적으로 사용되는 두 디지털 필터는 sin(pf)/pf(sinc) 및 선형 위상 유한 임펄스 응답(FIR) 필터입니다. Texas Instruments ADS1235, 24비트 ΔƩ ADC와 ADS1262 및 ADS1263 32비트 ΔƩ ADC(ADS1263은 백그라운드 측정을 위한 보조 24비트 ΔƩ ADC를 통합함)의 디지털 필터 구현에서는 sinc 필터를 단독으로 사용하거나 sinc 필터와 FIR 필터를 순서대로 결합하여 사용할 수 있습니다(그림 5).

그림 5: ADS1235 24비트 ΔƩ ADC는 sinc 필터를 단독으로 사용하거나 sinc 필터와 FIR 필터를 순서대로 결합하여 사용합니다. (이미지 출처: Texas Instruments)

그림 5: ADS1235 24비트 ΔƩ ADC는 sinc 필터를 단독으로 사용하거나 sinc 필터와 FIR 필터를 순서대로 결합하여 사용합니다. (이미지 출처: Texas Instruments)

그림 5에서 sinc(“Sinc”로 표시됨) 필터는 저역 통과 디지털 필터입니다. sinc 필터의 출력(w(n))은 방정식 3을 사용하여 계산합니다.

![]() 방정식 3

방정식 3

z 도메인 전달 함수는 다음과 같습니다.

방정식 4

방정식 4

주파수 응답은 다음과 같습니다.

![]() 방정식 5

방정식 5

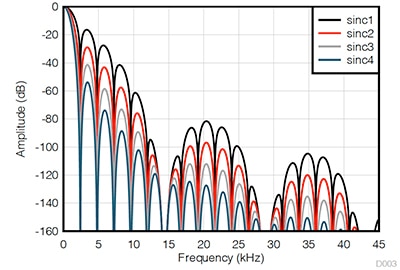

그림 5에서 SincN은 N개의 동일한 sinc 필터(직렬)입니다. sinc 필터의 그래픽 진폭과 주파수 응답을 비교한 형상은 빗 모양입니다(그림 6).

그림 6: ADS1262/63에서는 다양한 sinc 디지털 필터가 2400SPS 속도로 빗 모양의 주파수 응답을 생성합니다. 여기서 sinc2는 2개의 동일한 SINC 필터(직렬)에 해당하고 sinc3는 세 개의 동일한 sinc 필터(직렬)에 해당합니다. (이미지 출처: Texas Instruments)

그림 6: ADS1262/63에서는 다양한 sinc 디지털 필터가 2400SPS 속도로 빗 모양의 주파수 응답을 생성합니다. 여기서 sinc2는 2개의 동일한 SINC 필터(직렬)에 해당하고 sinc3는 세 개의 동일한 sinc 필터(직렬)에 해당합니다. (이미지 출처: Texas Instruments)

그림 6에서 피크와 null은 sinc 필터 응답의 특성입니다. 주파수 응답 null은 f(Hz) = N ·FD일 때 발생합니다. 여기서 N = 1, 2, 3, ... 입니다. null 주파수에서 필터의 이득은 0입니다.

Sinc 필터(직렬)는 감쇠를 높이므로 대기 시간이 증가합니다. 예를 들어 외부 클록 속도가 7.3728MHz인 특정 sinc 필터 계산에서 출력 데이터 전송률이 14400SPS일 경우 두 번째 sinc 필터의 출력 데이터 전송률은 7200SPS입니다.

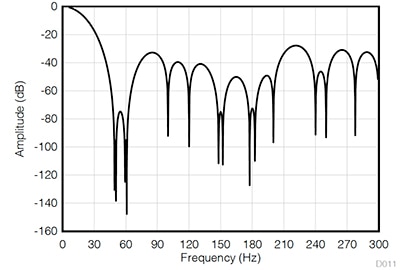

저역 통과 FIR 필터는 계수 기반 필터입니다. 이 필터는 2.5SPS ~ 20SPS 데이터 전송률에서 50Hz 및 60Hz의 동시 감쇠와 고조파를 생성합니다. FIR 필터 데이터 전송률의 변환 대기 시간은 단일 주기에 해당합니다. FIR 필터는 sinc 필터에서 사전 필터링된 데이터를 수신하고 데이터를 데시메이션하여 10SPS의 출력 데이터 전송률을 생성합니다(그림 7).

그림 7: ADS1262/63에서 FIR 필터는 50Hz 및 60Hz 신호를 감쇠하여 회선 주파수 전파 방해를 줄이고 해당 주파수에 가깝게 배치된 응답 null 계열을 제공합니다. null은 50Hz 및 60Hz 고조파에서 반복됩니다. (이미지 출처: Texas Instruments)

그림 7: ADS1262/63에서 FIR 필터는 50Hz 및 60Hz 신호를 감쇠하여 회선 주파수 전파 방해를 줄이고 해당 주파수에 가깝게 배치된 응답 null 계열을 제공합니다. null은 50Hz 및 60Hz 고조파에서 반복됩니다. (이미지 출처: Texas Instruments)

FIR 필터는 50Hz 및 60Hz 신호를 감쇠하여 회선 주파수 전파 방해를 줄이고 해당 주파수에 가깝게 배치된 응답 null 계열을 제공합니다. 응답 null은 50Hz 및 60Hz 고조파에서 반복됩니다.

정밀 저잡음 ΔƩ ADC

저잡음 ΔƩ ADC의 좋은 예로는 앞서 언급한 Texas Instruments ADS1235 차동 입력 24비트 컨버터가 있습니다.

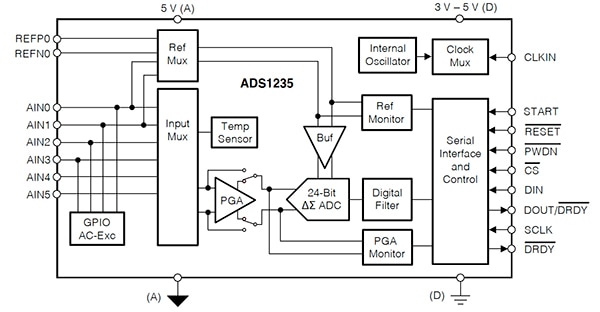

ADS1235는 이득이 1, 64 및 128인 통합된 프로그래밍 가능 이득 증폭기(PGA)D와 3개의 차동 입력 또는 5개의 단일 엔드 입력을 포함하는 정밀 7200SPS ΔƩ ADC입니다. 또한 이 소자에는 PGA 범위 초과 모니터링 및 레퍼런스 모니터링과 같은 진단 기능이 포함되어 있습니다. ADC는 계량 저울, 스트레인 게이지, 저항성 압력 센서를 비롯한 고정밀 장비를 위해 높은 정확도의 제로 드리프트 변환 데이터를 제공합니다(그림 8).

그림 8: 6채널 아날로그 입력과 GPIO 입력 멀티플렉서를 포함하는 ADS1235 24비트 ΔƩ ADC 제품 구성도 (이미지 출처: Texas Instruments)

그림 8: 6채널 아날로그 입력과 GPIO 입력 멀티플렉서를 포함하는 ADS1235 24비트 ΔƩ ADC 제품 구성도 (이미지 출처: Texas Instruments)

ADS1235의 경우 잡음 성능에 영향을 주는 중요한 요소로는 데이터 전송률, PGA 이득, 촙 모드가 있습니다. 데이터 전송률이 느리면 디지털 필터의 코너 주파수가 유입되어 잡음이 감소합니다. 또한 촙 모드에서 수행되는 2포인트 데이터 평균으로 인해 정상 작동에 비해 잡음이 √2 만큼 감소합니다.

저주파, 2.5SPS 데이터 전송률 및 1V/V PGA 이득에서 5V 시스템의 sinc3 디지털 출력에 대한 컨버터 잡음은 0.15mVRMS(0.3mV 피크 간(PP))이고, 유효 분해능과 잡음 없는 분해능은 24비트입니다. 이 소자의 이론적 SNR과 실제 SNR은 146dB입니다. 사실, 이러한 조건에서 안정적인 4차 변조기와 sinc1 ~ sinc4 필터는 24비트의 유효 분해능과 잡음 없는 분해능을 생성합니다.

ADS1235는 2.5SPS 데이터 전송률에서 거의 완벽한 24비트 변환을 실현했습니다. Texas Instruments ADS1262/63은 이 제품군의 차세대 ΔƩ ADC입니다. 이러한 소자의 주요 차이점은 ADS1262/63이 저잡음 회로망을 개선하고 확장된 32비트 출력 데이터 레지스터를 제공한다는 것입니다.

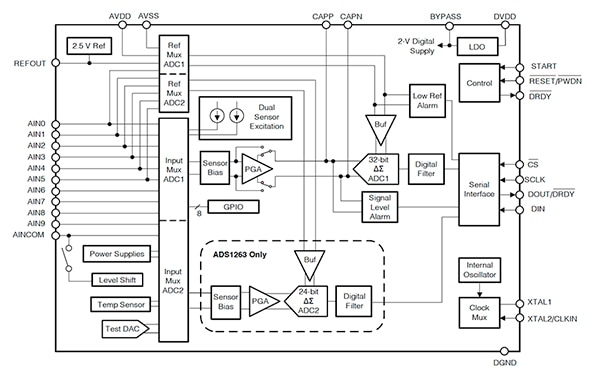

ADS1262/63은 이득이 1, 2, 4, 8, 16, 32인 향상된 저잡음 CMOS PGA를 제공합니다. 유연한 아날로그 프런트 엔드(AFE)는 직접 RTD 측정에 적합한 2개의 센서 여기 전류원을 통합합니다(그림 9).

그림 9: 6채널 아날로그 입력 멀티플렉서를 포함하는 ADS1262 및 ADS1263 32비트 ΔƩ ADC 제품 구성도 ADS1263에는 두 번째 온칩 24비트 ΔƩ ADC가 있습니다. (이미지 출처: Texas Instruments)

그림 9: 6채널 아날로그 입력 멀티플렉서를 포함하는 ADS1262 및 ADS1263 32비트 ΔƩ ADC 제품 구성도 ADS1263에는 두 번째 온칩 24비트 ΔƩ ADC가 있습니다. (이미지 출처: Texas Instruments)

ADS1235와 마찬가지로 PGA 이득, 데이터 전송률, 디지털 필터 모드 및 촙 모드는 ADS1262/63의 잡음 성능에 영향을 미치는 중요한 요소입니다. 32비트 분해능에서 ADS1262/63은 실제로 저잡음 깊이 성능을 보여줍니다.

우선, 안정적인 4차 변조기와 sinc1 ~ sinc4 필터는 32비트의 유효 분해능과 24비트의 잡음 없는 분해능 생성을 촉진합니다. 저주파, 2.5SPS 데이터 전송률 및 1V/V(바이패스) PGA 이득을 구성하여 5V 시스템에서 sinc3 디지털 출력의 컨버터 잡음은 0.08mVRMS(0.307mVPP)입니다. 이 소자는 26.9비트 유효 분해능 및 25비트 잡음 없는 분해능보다 뛰어납니다. 이 32비트 시스템의 이론적 SNR은 387dB이고 실제 SNR은 164dB입니다.

24비트 컨버터와 32비트 컨버터의 잡음 차이는 명확합니다. 32비트 ΔƩ ADC의 저잡음 성능이 24비트 ΔƩ ADC의 저잡음 성능보다 우수합니다(표 2).

*참고: SNR = 6.02 N + 1.76, 여기서 N은 비트 수입니다.

|

표 2: 전체 범위 입력 전압이 5V일 때 ADC rms 잡음, 피크 간 잡음 및 SNR 비교 (데이터 출처: DigiKey)

결론

ΔƩ ADC는 기능을 지속적으로 추가하면서 저잡음 한도를 계속해서 밀어붙이고 있습니다. 이 기사에서는 이 디지털 저잡음 ADC가 온도, 압력 및 로드 셀 응용 분야에 실제로 어떻게 매핑되는지를 보여줍니다. 정밀 24비트 ΔƩ ADC 및 32비트 ΔƩ ADC에 대한 기본 논의에서는 초정밀 특성을 실현하기 위한 경로를 요약합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.