AI/ML 이미징에 Efinix FPGA를 사용하는 이유와 방법 - 2부: 이미지 캡처 및 처리

DigiKey 유럽 편집자 제공

2023-05-05

편집자 주: FPGA에 대한 새로운 접근 방식은 기계 학습(ML) 및 인공 지능(AI)의 요구 사항을 해결하기 위해 제어가 더 세분화되고 유연성이 훨씬 개선되었습니다. 2부로 구성된 이 시리즈 중 1부에서는 Efinix의 아키텍처 중 하나를 소개하고 개발 기판을 사용하여 이 아키텍처로 시작하는 방법을 소개합니다. 2부에서는 개발 기판을 카메라와 같은 외부 장치 및 주변 장치에 연결하는 방법과 FPGA를 활용하여 이미지 처리 병목 현상을 개선하는 방법을 설명합니다.

FPGA는 산업 제어 및 안전에서부터 로봇 공학, 항공 우주, 자동차에 이르기까지 여러 응용 분야에서 중요한 역할을 담당합니다. 프로그래밍 가능한 논리 코어의 유연한 특성과 광범위한 인터페이스 기능으로 인해, 머신 러닝(ML)을 배포할 수 있는 이미지 처리 분야에서 FPGA의 사용 사례가 증가하고 있습니다. FPGA는 병렬 논리 구조 덕분에 여러 고속 카메라 인터페이스가 있는 솔루션을 구현하는 데 이상적입니다. 또한 FPGA는 논리에서 전용 처리 파이프라인 사용을 가능하게 하여 CPU 또는 GPU 기반 솔루션과 관련된 공유 리소스 병목 현상을 제거합니다.

Efinix의 Titanium FPGA에 대한 이 두 번째 기사에서는 FPGA의 Ti180 M484 개발 기판과 함께 제공되는 참고 이미지 처리 응용 분야를 살펴봅니다. 이번 목표는 설계의 구성 요소를 이해하고 FPGA 기술이 병목 현상을 제거하거나 개발자에게 다른 이점을 제공하는 부문을 식별하는 것입니다.

Ti180 M484 기반 참조 설계

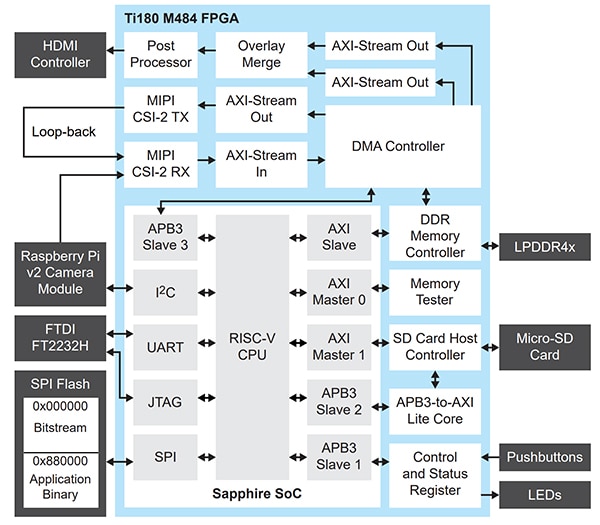

개념적으로 참조 설계(그림 1)는 여러 모바일 산업 프로세서 인터페이스(MIPI) 카메라에서 이미지를 수신하고, LPDDR4x에서 프레임 버퍼링을 수행한 다음 고화질 멀티미디어 인터페이스(HDMI) 디스플레이에 이미지를 출력합니다. 기판에서는 FPGA 메자닌 카드(FMC) 1개와 Samtec QSE 인터페이스 4개를 사용하여 카메라 입력과 HDMI 출력을 제공합니다.

그림 1: 개념적으로 Ti180 M484 참조 설계는 여러 MIPI 카메라에서 이미지를 수신하고, LPDDR4x에서 프레임 버퍼링을 수행한 다음 HDMI 디스플레이에 이미지를 출력합니다. (이미지 출처: Efinix)

그림 1: 개념적으로 Ti180 M484 참조 설계는 여러 MIPI 카메라에서 이미지를 수신하고, LPDDR4x에서 프레임 버퍼링을 수행한 다음 HDMI 디스플레이에 이미지를 출력합니다. (이미지 출처: Efinix)

FMC QSE 확장 카드를 HDMI 도터 카드와 함께 사용하여 출력 비디오 경로를 제공하고, 3개 QSE 커넥터를 사용하여 DFRobot SEN0494 MIPI 카메라와 연결합니다. MIPI 카메라를 여러 개 사용할 수 없는 경우 단일 카메라 채널을 루프백하여 단일 카메라로 추가 카메라를 시뮬레이션할 수 있습니다.

상위 레벨에서 이 응용 제품은 간단해 보일 수도 있습니다. 하지만 여러 고화질(HD) MIPI 스트림을 높은 프레임 속도로 수신하는 것은 어려운 일입니다. 여기서 FPGA 기술을 사용하면 설계자가 여러 MIPI 스트림을 병렬로 활용할 수 있기 때문에 유용합니다.

참조 설계 아키텍처에서는 FPGA를 통해 병렬 처리 구조와 순차적 처리 구조를 모두 활용합니다. 병렬 구조는 이미지 처리 파이프라인을 구현하는 데 사용되고, RISC-V 프로세서는 FPGA 대조표(LUT)에 사용되는 순차적 처리를 제공합니다.

대부분의 FPGA 기반 이미지 처리 시스템에서 이미지 처리 파이프라인을 입력 스트림과 출력 스트림의 두 요소로 분할할 수 있습니다. 입력 스트림은 카메라/센서 인터페이스에 연결되고, 처리 기능은 센서의 출력에 적용됩니다. 이러한 기능은 베이어 변환, 자동 화이트 밸런스 및 기타 개선 사항을 포함할 수 있습니다. 출력 스트림에서는 이미지가 표시되도록 준비됩니다. 여기에는 색 공간 변경(예: RGB에서 YUV로 변경)과 원하는 출력 형식에 대한 사후 처리(예: HDMI)가 포함됩니다.

입력 이미지 처리 체인이 센서 픽셀 클록 속도로 작동하는 경우도 있습니다. 이 경우 출력 디스플레이 주파수로 처리되는 출력 체인과 타이밍이 다릅니다.

프레임 버퍼는 입력을 출력 처리 파이프라인에 연결하는 데 사용되며, 주로 LPDDR4x와 같은 외부 고성능 메모리에 저장됩니다. 이 프레임 버퍼는 입력 파이프라인과 출력 파이프라인 사이에서 감결합되므로, 적절한 클록 주파수에서 직접 메모리 액세스를 통해 프레임 버퍼에 액세스할 수 있습니다.

Ti180 참조 설계에서는 위에 요약된 개념과 비슷한 접근 방식을 사용합니다. 입력 이미지 처리 파이프라인에서는 Titanium FPGA의 MIPI 물리층(MIPI D-PHY) 지원 입/출력(I/O)을 기반으로 하는 MIPI 카메라 직렬 인터페이스2(CSI-2) 수신기 지적 재산(IP) 코어를 구현합니다. MIPI는 저속 통신과 고속 통신 이외에 동일한 차동 회로에서 단일 종단 신호와 차동 신호를 모두 사용하므로 까다로운 인터페이스입니다. MIPI D-PHY를 FPGA I/O 내에 통합하면 회로 카드 설계의 복잡성과 부품 명세서(BOM)가 감소됩니다.

그런 다음 카메라에서 수신된 이미지 스트림을 사용하여 참조 설계에서 MIPI CSI-2 RX의 출력을 고급 확장 인터페이스(AXI) 스트림으로 변환합니다. AXI 스트림은 마스터에서 슬레이브로 데이터 스트림을 제공하는 단뱡향 고속 인터페이스입니다. 마스터와 슬레이브 간에 전송할 핸드셰이킹 신호가 측대파 신호와 함께 제공됩니다(tvalid 및 tready). 이러한 측대파 신호는 이미지 타이밍 정보(예: 프레임 시작, 라인 끝)를 전달하는 데 사용될 수 있습니다.

AXI 스트림은 이미지 처리 응용 분야에 적합하며 Efinix에서 다양한 이미치 처리 IP를 제공한 후 응용 분야에 필요할 때 처리 체인에 쉽게 통합할 수 있도록 해줍니다.

수신된 후 MIPI CSI-2 이미지 데이터 및 타이밍 신호는 AXI 스트림으로 변환되어 직접 메모리 액세스(DMA) 모듈에 입력되며, LPDDR4x에 이미지 프레임을 쓰고 프레임 버퍼 역할을 합니다.

이 DMA 모듈은 Sapphire SoC(단일 칩 시스템) 내의 FPGA에서 RISC-V 코어의 제어 하에 작동합니다. 이 SoC는 DMA 쓰기 중지 및 시작과 같은 제어를 제공하며 LPDDR4x에 이미지 데이터를 올바르게 기록하는 데 필요한 정보를 DMA 쓰기 채널에 제공합니다. 여기에는 이미지 위치에 대한 정보와 함께 이미지의 폭과 높이(단위: 바이트)가 포함됩니다.

참조 설계의 출력 채널에서는 RISC-V SoC의 제어에 따라 LPDDR4x 프레임 버퍼에서 이미지 정보를 읽습니다. 이 데이터는 DMA IP에서 AXI 스트림으로 출력된 후 센서에서 제공하는 RAW 형식에서 RGB 형식으로 변환되며(그림 2), Analog Devices의 기판 실장 ADV7511 HDMI 송신기를 통해 출력할 수 있도록 준비됩니다.

그림 2: 샘플 이미지는 참조 설계에서 출력됩니다. (이미지 출처: Adam Taylor)

그림 2: 샘플 이미지는 참조 설계에서 출력됩니다. (이미지 출처: Adam Taylor)

또한 Sapphire SoC RISC-V에서 DMA를 사용하여 프레임 버퍼에 저장된 이미지에 액세스하고, 통계 및 이미지 정보를 추상화할 수 있습니다. 또한 Sapphire SoC에서는 LPDDR4x에 오버레이를 기록하여 출력 비디오 스트림과 병합할 수 있습니다.

최신 CMOS 이미지 센서(CIS)는 다양한 작동 모드를 지원하며 온칩 처리와 다양한 출력 형식 및 클로킹 체계를 제공하도록 구성될 수 있습니다. 이 구성은 일반적으로 I²C 인터페이스를 통해 제공됩니다. Efinix 참조 설계에서 MIPI 카메라와의 이 I²C 통신은 Sapphire SoC RISC-V 프로세서에 의해 제공됩니다.

RISC-V 프로세서를 Titanium FPGA 내에 통합하면 설계 위험을 높이는 복잡한 FPGA 상태 시스템과 BOM에 추가되는 외부 프로세서를 모두 구현할 필요가 없으므로 최종 솔루션의 전체 크기가 감소됩니다.

또한 프로세서를 통합할 경우 추가 IP를 통해 MicroSD 카드와 통신할 수도 있습니다. 이는 나중에 분석할 수 있도록 이미지를 저장해야 하는 실제 응용 분야를 지원할 수 있습니다.

전반적으로 Ti180 참조 설계 아키텍처는 개발자가 시스템 통합을 통해 BOM 비용을 절감할 수 있는 콤팩트한 저비용 고성능 솔루션을 지원하도록 최적화되었습니다.

참조 설계의 주요 이점 중 하나는 맞춤형 하드웨어에서 응용 제품 개발을 빠르게 시작하여 개발자가 설계의 중요 요소를 활용하고 필요한 맞춤 설정을 적용하여 빌드할 수 있도록 지원한다는 것입니다. 여기에는 Efinix의 TinyML 흐름을 사용하여 FPGA에서 작동하는 시각 기반 TinyML 응용 제품을 구현하는 기능이 포함됩니다. 여기서는 FPGA 논리의 병렬 특성과 RISC-V 프로세서에 사용자 지정 지침을 쉽게 추가하는 기능을 모두 활용하여 FPGA 논리 내에서 가속기를 생성할 수 있습니다.

구현

1부에서 설명한 대로 Efinix 아키텍처는 교환 가능한 논리 및 라우팅(XLR) 셀을 사용하여 라우팅과 논리 기능을 모두 제공할 수 있다는 점에서 독특합니다. 참조 설계와 같은 비디오 시스템은 논리와 라우팅이 많은 혼합 시스템입니다. 즉, 이미지 처리 기능을 구현하려면 확장 논리가 필요하고, 필요한 주파수에서 IP 셀을 연결하려면 확장 라우팅이 필요합니다.

참조 설계에서는 장치 내에서 XLR 셀의 약 42%를 사용하고 에지 ML과 같은 맞춤형 응용 제품을 비롯한 추가 기능을 위해 충분한 공간을 비워둡니다.

또한 640개 DSP 블록 중 4개와 메모리 블록의 40%만 사용하여 RAM 블록과 디지털 신호 처리(DSP) 블록을 매우 효율적으로 사용합니다(그림 3).

|

그림 3: Efinix 아키텍처의 리소스 할당에서는 XLR 셀의 42%만 사용되고 추가 프로세스를 위해 충분한 공간이 활용됩니다. (이미지 출처: Adam Taylor)

장치 IO에서 LPDDR4x용 DDR 인터페이스는 이미지 프레임 버퍼와 Sapphire SoC에 응용 제품 메모리를 제공하는 데 사용됩니다. 모든 장치 전용 MIPI 리소스는 위상 고정 루프의 50%와 함께 활용됩니다(그림 4).

|

그림 4: 사용된 인터페이스 및 I/O 리소스 스냅샷 (이미지 출처: Adam Taylor)

범용 I/O(GPIO)는 NOR FLASH, USB UART, SD 카드를 비롯하여 Sapphire SoC에 연결되는 다양한 인터페이스와 함께 I²C 통신을 제공하는 데 사용됩니다. HSIO는 ADC7511 HDMI 송신기에 고속 비디오 출력을 제공하는 데 사용됩니다.

FPGA를 사용하여 설계할 때 중요한 요소 중 하나는 FPGA 내에서 설계를 구현하여 장착하고, FPGA 내에서 논리 설계를 적용하고 라우팅할 때 필요한 타이밍 성능을 실현할 수 있다는 것입니다.

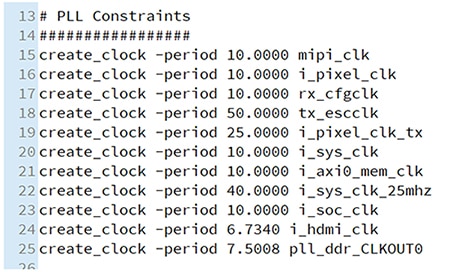

단일 클록 도메인 FPGA 설계의 시대는 오래 전에 끝났습니다. Ti180 참조 설계에는 고주파에서 실행되는 다양한 클록이 있습니다. 최종 타이밍 표에는 시스템 내부 클록에 대해 실현되는 최대 주파수가 표시됩니다. HDMI 출력 클록에 대한 최대 클록 주파수가 148.5MHz인 제약 조건(그림 5)에서도 요청된 타이밍 성능을 확인할 수 있습니다.

그림 5: 참조 설계의 클록 제약 조건 (이미지 출처: Adam Taylor)

그림 5: 참조 설계의 클록 제약 조건 (이미지 출처: Adam Taylor)

제약 조건에 대한 타이밍 구현에서는 가능한 라우팅 지연을 줄여서 설계 성능을 높임으로써 Titanium FPGA XLR 구조의 잠재력을 보여줍니다(그림 6).

|

그림 6: 제약 조건에 대한 타이밍 구현에서는 가능한 라우팅 지연을 줄여서 설계 성능을 높임으로써 Titanium FPGA XLR 구조의 잠재력을 보여줍니다. (이미지 출처: Adam Taylor)

결론

Ti180 M484 참조 설계에서는 특히 Efinix FPGA 및 Ti180의 기능을 명확하게 보여줍니다. 설계에서는 다양한 고유 I/O 구조를 활용하여 여러 수신 MIPI 스트림을 지원하는 복잡한 이미지 처리 경로를 구현합니다. 이 이미지 처리 시스템은 응용 제품에 필요한 순차적 처리 요소를 구현하는 소프트 코어 Sapphire SoC의 제어 하에 작동합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.