AI/ML 이미징에 Efinix FPGA를 사용하는 이유와 방법 — 1부: 시작하기

DigiKey 유럽 편집자 제공

2023-04-20

편집자 주: FPGA에 대한 새로운 접근 방식은 기계 학습(ML) 및 인공 지능(AI)의 요구 사항을 해결하기 위해 제어가 더 세분화되고 유연성이 훨씬 늘어났습니다. 2부로 구성된 이 시리즈의 1부에서는 Efinix의 아키텍처 중 하나를 소개하고 개발 기판을 사용하여 이 아키텍처로 시작하는 방법을 소개합니다. 2부에서는 개발 기판을 카메라와 같은 외부 장치 및 주변 장치에 연결하는 방법을 설명합니다.

FPGA는 산업 제어 및 안전에서부터 로봇 공학, 항공 우주, 자동차에 이르기까지 여러 응용 분야에서 중요한 역할을 담당합니다. 프로그래밍 가능한 논리 코어의 유연한 특성과 광범위한 인터페이스 기능으로 인해 늘어나는 FPGA의 사용 사례 중 하나는 ML 추론이 배포될 때의 이미지 처리에 있습니다. FPGA는 여러 고속 카메라 인터페이스가 있는 솔루션을 구현하기에 이상적입니다. 또한 FPGA는 논리에서 전용 처리 파이프라인 구현을 가능하게 하여 CPU 또는 GPU 기반 솔루션과 관련된 병목현상을 제거합니다.

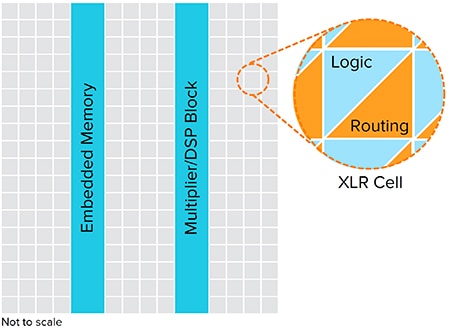

그러나 여러 개발자의 응용 분야에는 조합 논리 블록(CLB)이 있는 기존 FPGA 아키텍처가 제공할 수 있는 것 이상으로 더 많은 ML/AI 기능과 더 세분화된 제어 또는 라우팅 및 논리가 필요합니다. FPGA 아키텍처에 대한 최신 접근 방식은 이러한 문제를 해결합니다. 예를 들어 Efinix의 Quantum 아키텍처는 교환 가능한 논리 및 라우팅(XLR) 블록을 사용합니다.

이 기사에서는 AI/ML 기능을 강조하고 실제 구현을 소개하면서 Efinix FPGA 아키텍처의 주요 특징 및 특성을 설명합니다. 그런 다음 개발자가 다음 AI/ML 이미징 디자인을 빠르게 시작하기 위해 사용할 수 있는 개발 기판과 관련 도구를 살펴봅니다.

Efinix FPGA 장치

Efinix 현재 두 가지 장치를 제공합니다. Efinix는 처음에 Trion 제품군을 도입했습니다. 이 제품군은 4K에서 120K 논리 소자에 이르는 논리 밀도를 제공하고 SMIC 40LL 공정을 사용하여 제조됩니다. 최신 장치 라인인 Titanium 제품군은 35K에서 1M 논리 소자에 이르는 논리 밀도를 제공하며 많이 사용되는 TSMC 16nm 노드에서 제조됩니다.

두 제품 모두 FPGA 세계에서는 고유한 Quantum 아키텍처를 기반으로 합니다. 표준 FPGA 아키텍처는 가장 간단한 레벨에서 대조표(LUT)와 플립플롭이 포함된 CLB를 기반으로 합니다. CLB는 라우팅을 통해 상호 연결되는 논리 방정식을 구현하고 Efinix의 Quantum 아키텍처는 XLR 블록을 사용하여 고유 논리와 라우팅 블록에서 멀어집니다.

XLR 블록의 고유한 특징은 이 블록이 LUT, 레지스터 및 가산기, 또는 라우팅 행렬이 있는 논리 셀로 구성될 수 있다는 점입니다. 이 접근 방식은 라우팅을 유연하게 하는 세분화된 아키텍처를 제공하여 원하는 성능을 달성하기 위해 논리가 많거나 라우팅이 많은 구현을 가능하게 합니다.

그림 1: XLR 블록의 고유한 특징은 이 블록이 LUT, 레지스터 및 가산기, 또는 라우팅 행렬이 있는 논리 셀로 구성될 수 있다는 점입니다. (이미지 출처: Efinix)

그림 1: XLR 블록의 고유한 특징은 이 블록이 LUT, 레지스터 및 가산기, 또는 라우팅 행렬이 있는 논리 셀로 구성될 수 있다는 점입니다. (이미지 출처: Efinix)

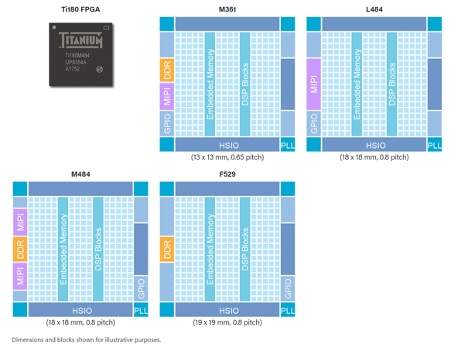

최신 제품군인 Titanium 소자는 개발자에게 최고급 기능을 제공합니다(그림 2). 이러한 Titanium 소자는 XLR 코어와 함께 선택한 장치에 따라 16Gbps 또는 25.8Gbps에서 작동하는 멀티 기가비트 직렬 링크를 제공합니다. 이러한 멀티 기가비트 링크는 칩 내외부에 고속으로 데이터를 전송하는 데 중요합니다.

그림 2: Titanium FPGA Ti180은 버스 폭, I/O, 메모리 요구 사항에 따라 다양한 옵션으로 제공됩니다. (이미지 출처: Efinix)

그림 2: Titanium FPGA Ti180은 버스 폭, I/O, 메모리 요구 사항에 따라 다양한 옵션으로 제공됩니다. (이미지 출처: Efinix)

Titanium 소자는 또한 범용 I/O(GPIO)로 그룹 지어질 수 있고 3.3V, 2.5V, 1.8V에서 저전압 CMOS(LVCMOS)와 같은 단일 종단 I/O 표준을 지원할 수 있는 광범위한 입/출력(I/O) 인터페이스 기능을 제공합니다.

고속 및 차동 인터페이스의 경우 Titanium 소자는 1.2V, 1.5V에서 LVCMOS, SSTL 및 HSTL과 같은 단일 종단 I/O 표준을 지원하는 고속 I/O(HSIO)를 제공합니다. HSIO가 지원하는 차동 I/O 표준에는 저전압 차동 신호(LVDS), 차동 SSTL, HSTL이 있습니다.

또한 현대의 FPGA에는 긴밀히 연결된 고대역폭 메모리가 필요합니다. 이 메모리는 이미지 처리 응용 분야를 위한 이미지 프레임과 신호 처리를 위한 샘플 데이터를 저장하는 데 사용되며 FPGA 내에서 구현된 프로세서를 위한 운영 체제 및 소프트웨어를 실행하는 데에도 사용됩니다. Titanium 소자의 범위는 동적 데이터 전송률4(DDR4) 및 저전력 DDR4(x)(LPDDR4(x))와 연결할 수 있습니다. 선별된 정확한 Titanium 소자에 따라 버스 폭 지원은 x32(J) 또는 x16(M)인 반면 일부 소자에는 LPDDR4 지원(L)이 없습니다.

Titanium FPGA는 SRAM 기반이며 마스터/슬레이브 직렬 주변 소자 상호 연결(SPI) 또는 JTAG가 수행하는 장치 구성이 있는 구성 메모리가 필요합니다. 이 구성 방법의 보안을 보장하기 위해 Titanium FPGA는 비트스트림 인증을 제공하는 AES GCM 및 RSA-4096과 함께 비트스트림 AES GCM 암호화를 사용합니다. 악의적인 사용자가 동작에 액세스하고 조작할 수 있는 에지에 FPGA가 배치되므로 이와 같은 강력한 보안이 필요합니다.

개발 기판 소개

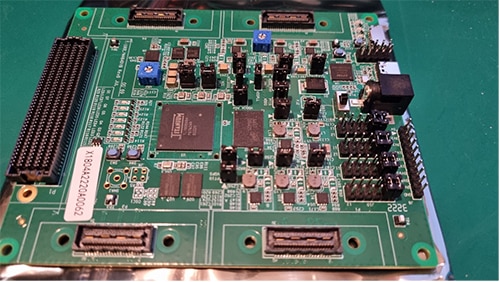

개발 기판은 장치 및 시제품 기능을 탐색하는 데 사용할 수 있으므로 FPGA 평가 프로세스의 중요한 요소를 형성합니다. 따라서 전반적인 위험을 줄이는 데 도움이 됩니다. Titanium FPGA를 평가하고 시제품 제작 응용 분야를 시작하는 데 사용할 수 있는 첫 번째 개발 기판은 Ti180 M484(그림 3)입니다. 기판에는 1개의 FPGA 메자닌 카드(FMC) 커넥터와 4개의 Samtec QSE 커넥터가 있습니다.

그림 3: Titanium FPGA와 함께 Ti180 M484 개발 키트에는 1개의 FMC 커넥터와 4개의 Samtec QSE 커넥터가 있습니다. (이미지 출처: Adam Taylor)

그림 3: Titanium FPGA와 함께 Ti180 M484 개발 키트에는 1개의 FMC 커넥터와 4개의 Samtec QSE 커넥터가 있습니다. (이미지 출처: Adam Taylor)

이 개발 기판에 사용된 Ti180 FPGA는 172K XLR 셀, 32개의 글로벌 클록, 640개의 디지털 신호 처리(DSP) 소자, 내장형 RAM 13Mbit를 제공합니다. DSP 소자는 고정 소수점 18 x 19 곱셈과 48비트 곱셈을 구현할 수 있습니다. 이 DSP는 또한 듀얼 구성 또는 쿼드 구성에서 실행하는 단일 명령, 다중 데이터(SIMD) 연산에 최적화될 수 있습니다. DSP 소자는 부동 소수점 연산을 수행하도록 구성될 수도 있습니다.

대부분의 개발 기판과 같이 Ti180 개발 기판에는 간단한 LED와 버튼이 있습니다. 하지만 이 개발 기판의 진정한 역량은 그 인터페이스 기능에 있습니다. Ti180 개발 기판에는 다양한 주변 소자를 연결할 수 있는 핀 수가 적은 FMC 커넥터가 있습니다. 이 커넥터는 널리 사용되는 표준이므로 고속 아날로그 디지털 컨버터(ADC), 디지털 아날로그 컨버터(DAC), 네트워킹, 메모리/스토리지 솔루션의 인터페이스를 가능하게 하는 많은 FMC 카드가 있습니다.

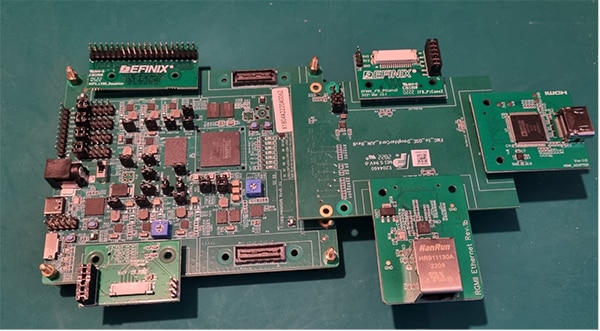

FMC 연결 외에도 기판에는 개발자가 확장 카드를 추가할 수 있는 4개의 Samtec QSE 커넥터가 있습니다. 이러한 QSE 커넥터는 MIPI 입력 및 출력을 제공하는 데 사용되며 각 QSE 커넥터가 MIPI 입력 또는 출력을 제공합니다.

그림 4: Ti180 M484 개발 키트는 QSE와 FMC 커넥터를 기반으로 하는 다목적 확장 옵션과 함께 표시됩니다. (이미지 출처: Adam Taylor)

그림 4: Ti180 M484 개발 키트는 QSE와 FMC 커넥터를 기반으로 하는 다목적 확장 옵션과 함께 표시됩니다. (이미지 출처: Adam Taylor)

Ti180 기판에는 또한 이미지 또는 신호 처리 응용 분야에 필요한 고성능 메모리를 지원하는 256Mbit의 LPDDR4가 있습니다. 또한 이 개발 기판에는 25MHz, 33.33MHz, 50MHz, 74.25MHz의 다양한 클로킹 옵션이 있으며 이 클로킹 옵션은 장치 위상 고정 루프(PLL)와 함께 사용되어 다양한 내부 주파수를 생성할 수 있습니다.

개발 시 기판에 실시간으로 다시 프로그래밍하고 디버깅하는 기능은 중요하며 USB-C 인터페이스를 통해 온보드로 제공되는 JTAG 연결이 필요합니다. 또한 구성 솔루션을 시연하는 데 사용할 수 있는 256Mbit NOR 플래시 장치의 두 가지 형태에서 비휘발성 메모리로 제공됩니다.

이 기판은 상자에 포함된 12V 범용 전력 어댑터로 구동됩니다. 또한 HDMI, 이더넷, MIPI 및 LVDS용 QSE 기반 확장 카드와 함께 FMC QSE 브레이크 아웃이 포함되어 있습니다. Ti180 이미지 처리 기능을 시연하기 위해 1개의 듀얼 RPI 도터 카드와 2개의 IMX477 카메라 카드도 제공됩니다.

소프트웨어 환경

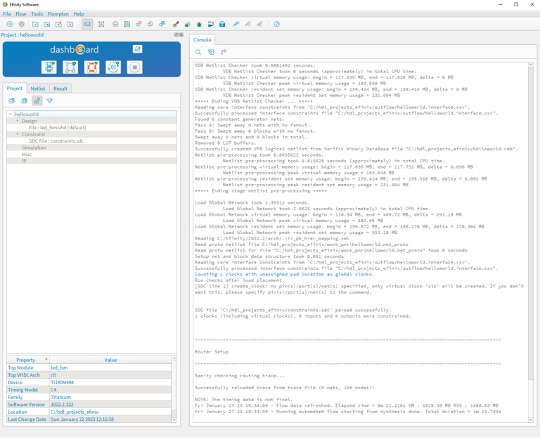

Ti180 개발 기판을 대상으로 하는 구현 설계는 Efinix 소프트웨어 Efinity를 사용합니다. 이 소프트웨어를 사용하면 합성, 배치 및 경로를 통해 비트 스트림을 생성할 수 있습니다. 또한 개발자에게 지적 재산(IP) 블록, 타이밍 분석, 온칩 디버깅을 제공합니다.

Efinity 소프트웨어에 액세스하려면 개발 기판이 필요합니다. 그러나 다른 벤더와는 달리 이 도구에는 추가 라이선스를 요구하는 다른 버전이 없습니다.

Efinity 내에서 선택한 장치를 대상으로 하는 새 프로젝트가 만들어집니다. 그런 다음 RTL 파일이 이 프로젝트에 추가되고 타이밍과 I/O 설계를 위해 제약 조건을 만들 수 있습니다. Efinity 내에서 개발자들은 또한 HSIO, GPIO 및 특수 I/O를 활용하여 I/O 설계를 구현할 수도 있습니다.

그림 5: Efinity 내에서 선택한 장치를 대상으로 하는 새 프로젝트가 만들어집니다. (이미지 출처: Adam Taylor)

그림 5: Efinity 내에서 선택한 장치를 대상으로 하는 새 프로젝트가 만들어집니다. (이미지 출처: Adam Taylor)

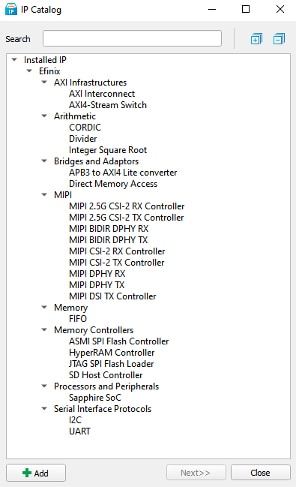

FPGA 설계에서 중요한 요소는 특히 AXI 상호 연결, 메모리 컨트롤러, 소프트코어 프로세서와 같은 복잡한 IP의 경우 IP를 활용하는 것입니다. Efinity는 개발자에게 설계 공정을 가속화하기 위해 사용할 수 있는 다양한 IP 블록을 제공합니다.

그림 6: Efinity는 개발자에게 설계 공정을 가속화하기 위해 사용할 수 있는 IP 카탈로그를 제공합니다. (이미지 출처: Adam Taylor)

그림 6: Efinity는 개발자에게 설계 공정을 가속화하기 위해 사용할 수 있는 IP 카탈로그를 제공합니다. (이미지 출처: Adam Taylor)

FPGA가 병렬 처리 구조를 구현하는 데 탁월하지만 많은 FPGA 설계에는 소프트코어 프로세서가 포함되어 있습니다. 이를 통해 네트워크 통신과 같은 순차적 처리를 구현할 수 있습니다. Efinix 장치에 소프트코어 프로세서를 배치할 수 있도록 Efinity는 Sapphire SoC(시스템온칩) 구성 도구를 제공합니다. Sapphire를 사용하여 개발자는 내장형 Linux 운영 체제를 실행할 수 있는 기능과 함께 여러 프로세서에서 캐시와 캐시 일관성 모두를 갖춘 멀티 프로세서 시스템을 정의할 수 있습니다. 개발자는 Sapphire 내에서 1개 ~ 4개의 소프트코어 프로세서를 선택할 수 있습니다.

구현된 소프트코어 프로세서는 RISC-V 명령어 세트 아키텍처를 기반으로 하는 VexRiscV 소프트 CPU입니다. VexRiscV 프로세서는 파이프라이닝을 위한 확장 기능이 있는 32비트 구현이며 구성 가능한 기능 세트를 제공하여 Efinix 장치에서 구현하기에 이상적입니다. 선택 사항인 구성에는 배율기, 원자 명령어, 부동 소수점 확장, 압축 명령어가 포함됩니다. SoC 시스템 구성에 따라 성능 범위는 0.86DMIPS/MHz ~ 1.05DMIPS/MHz입니다.

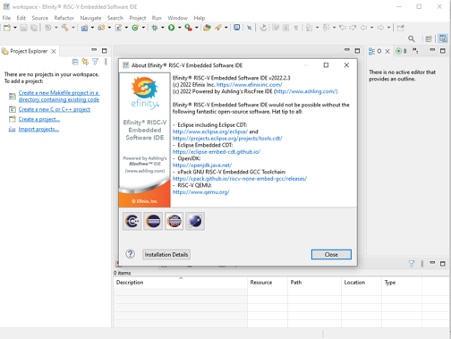

하드웨어 환경이 설계되고 Efinix 장치에 구현되면 Ashling RiscFree IDE를 사용하여 응용 소프트웨어를 개발할 수 있습니다. Ashling RiscFree는 배포하기 전에 애플리케이션을 미세 조정하기 위해 대상에 대한 디버그와 함께 응용 소프트웨어의 생성과 컴파일을 가능하게 하는 Eclipse 기반 IDE입니다.

그림 7: Ashling RiscFree는 대상에 대한 디버그와 함께 응용 소프트웨어의 생성과 컴파일을 가능하게 하는 Eclipse 기반 IDE입니다. (이미지 출처: Adam Taylor)

그림 7: Ashling RiscFree는 대상에 대한 디버그와 함께 응용 소프트웨어의 생성과 컴파일을 가능하게 하는 Eclipse 기반 IDE입니다. (이미지 출처: Adam Taylor)

내장형 Linux 솔루션이 개발 중인 경우 1단계 부트로더, OpenSBI, U-Boot 및 Buildroot를 사용하는 Linux를 비롯한 필요한 모든 부트 아티팩트가 제공됩니다. 또는 실시간 솔루션이 필요한 경우 개발자는 FreeRTOS를 사용할 수 있습니다.

AI 구현

Efinix의 AI 구현은 RISC-V 소프트코어 작업을 기반으로 합니다. 이는 RISC-V 프로세서의 맞춤형 명령어 기능을 활용하여 TensorFlow Lite 솔루션을 가속화할 수 있습니다. RISC-V 프로세서를 사용하면 사용자는 AI 추론을 따라 사전 처리 또는 사후 처리의 일환으로 사용할 수 있는 맞춤형 명령어를 생성하여 더 응답성이 뛰어나고 결정적인 솔루션을 만들 수 있습니다.

AI 구현으로 시작하려면 첫 번째 단계는 Efinix Model Zoo를 탐색해야 합니다. 이는 해당 최종 기술에 최적화된 AI/ML 모델의 라이브러리입니다. Efinix 장치로 작업하는 개발자의 경우 Model Zoo에 액세스할 수 있으며 Jupyter Notebooks 또는 Google Colab을 사용하여 네트워크를 학습할 수 있습니다. 네트워크를 학습하면 TensorFlow Lite 컨버터를 사용하여 부동 소수점 모델에서 양자화된 모델로 전환할 수 있습니다.

TensorFlow Lite 형식이 되면 RISC-V 솔루션에 배포 가능한 솔루션을 만드는 데 Efinix의 tinyML 가속기를 사용할 수 있습니다. tinyML 생성기를 사용하여 개발자는 가속기 구현을 맞춤 설정하고 프로젝트 파일을 생성할 수 있습니다. 이러한 방식으로 배포할 경우 가속 범위는 선택한 아키텍처와 맞춤화에 따라 4x ~ 200x 사이가 될 수 있습니다.

결론

Efinix 장치는 고유 XLR 아키텍처 덕분에 개발자에게 유연성을 부여합니다. 도구 체인을 통해 RTL 설계 구현뿐 아니라 소프트코어 RISC-V 프로세서를 배포하는 복잡한 SoC 솔루션을 구현할 수 있습니다. ML 추론 배포를 가능하게 하는 AI/ML 솔루션은 소프트코어 SoC 위에 구축됩니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.