다중 코어 프로세서를 사용하여 다양한 기능 및 안전 요구 사항 충족

DigiKey 북미 편집자 제공

2020-10-01

자동차, 산업, 로봇 공학, 건물 관리 및 기타 중요 내장형 시스템 응용 분야에서는 인간 기계 간 인터페이스(HMI)를 위한 다중 화면 그래픽 디스플레이를 사용하여 저전력 실시간 모니터링부터 상위 수준의 멀티미디어 응용 분야까지 다양한 워크로드를 처리해야 합니다. 광범위한 기능적 요구 사항을 충족하면서 엄격한 안전 표준을 준수하고, 비용과 실장 면적을 줄이며, 전력/성능 균형을 최적화할 수 있어야 합니다.

때때로 상충되는 이러한 요구 사항을 충족하기 위해 개발자는 그래픽, 보안 및 안전 분야의 특정 요구 사항을 지원하는 데 필요한 장치를 추가하여 설계 및 제조를 보강하거나 기능을 줄이는 방식으로 타협해야 합니다. 실제로 개발자는 광범위한 주요 내장형 시스템 응용 분야에서 이러한 요구 사항을 충족하고 폭넓은 제품을 지원할 수 있는 하나의 솔루션이 필요합니다.

이 기사에서는 주요 내장형 시스템 설계의 진화 과정을 간략하게 설명합니다. 그런 다음 기판 기능과 안전 인증 가능 기능에 대해 빠르게 늘어나는 요구 사항을 지원하기 위해 NXP Semiconductors에서 특별히 고안된 다중 코어 응용 프로세서를 사용하여 개발자의 현안 과제를 해결할 수 있는 방법을 살펴봅니다.

내장형 시스템 설계 고려 사항의 진화

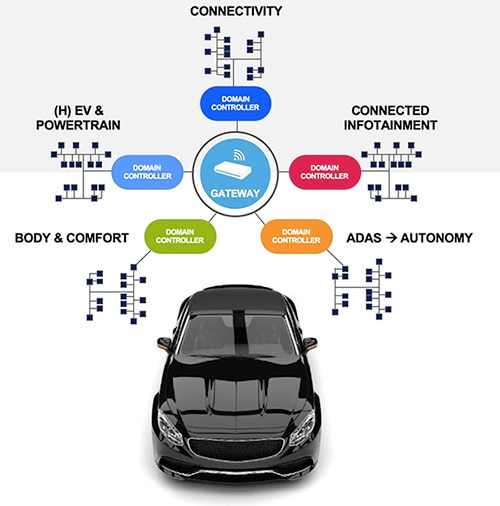

광범위한 기능을 제공하는 장치에 대한 수요로 인해 제한된 시스템 기능을 지원하는 내장형 시스템의 전통적인 역할이 거의 대체되었습니다. 예를 들어 산업 응용 분야의 경우 스마트 도구 및 장비에 향상된 HMI 기능이 필요해지면서 기존 산업의 실시간 요구 사항을 충족하면서 최적화된 그래픽을 제공할 수 있는 프로세서가 요구됩니다. 마찬가지로 기능적 도메인 클러스터와 게이트웨이로 구성되는 계층적 아키텍처를 지향하는 자동차 응용 분야의 추세로 이러한 요구 사항을 완전히 충족할 수 있는 프로세서가 필요합니다(그림 1).

그림 1: 계층적 자동차 시스템 아키텍처를 지향하는 추세에 따라 더 통합되고 확장 가능한 프로세서 솔루션이 필요해졌습니다. (이미지 출처: NXP Semiconductors)

그림 1: 계층적 자동차 시스템 아키텍처를 지향하는 추세에 따라 더 통합되고 확장 가능한 프로세서 솔루션이 필요해졌습니다. (이미지 출처: NXP Semiconductors)

각 기능 도메인 내에서 더 정교한 기능에 대한 수요가 증가하면서 성능 및 통합 기능에 대한 임계값이 높아지고 있습니다. 예를 들어 헤즈업 디스플레이의 등장으로 운전자에게 중요 그래픽 정보를 지속적으로 제공할 수 있는 솔루션이 필요해졌습니다. 이러한 차세대 디스플레이와 함께 향상된 운전자 경고 기능에 대한 수요가 증가하면서 졸음을 감지할 수 있는 고급 인식 소프트웨어의 고성능 실행과 카메라 인터페이스에 대한 요구 사항이 증가하고 있습니다.

응용 분야의 지속적인 발전으로 고집적 확장 가능 솔루션이 필요해지면서 설계 실장 면적, 비용 및 복잡도를 최소화하면서 점점 더 다양한 요구 사항을 충족해야 합니다. NXP의 i.MX 8 응용 프로세서 제품군을 사용하는 개발자는 광범위한 응용 분야의 요구 사항을 지원하는 데 필요한 다양한 기능 및 성능과 호환되는 프로세서 플랫폼을 활용할 수 있습니다. i.MX 8 제품군 내에서 NXP i.MX 8X 계열은 미드레인지 자동차 및 산업 응용 분야에 필요한 안전 인증 가능 프로세서에 대한 새로운 요구를 해결합니다.

다양한 워크로드를 관리하는 다중 코어 아키텍처

개발자가 자동차 및 산업 응용 분야에서 장치를 구현할 때 직면하는 어려움 중 하나로 가파르게 증가하는 요구 사항이 있습니다. 개발자가 실시간 또는 상위 수준 응용 처리 워크로드를 처리해야 하는 경우 지능형 서브 시스템과 다양한 유형의 컴퓨팅이 필요합니다. 개발자는 기능적 안전 요구 사항을 지원하면서 안정적인 실시간 응답과 고성능 응용 제품 실행을 제공할 수 있는 솔루션을 점점 더 필요로 합니다.

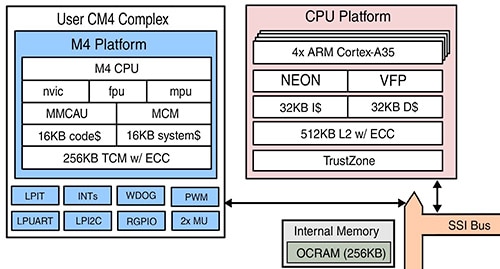

실시간 기능, 고성능 처리 및 저전력 소비를 제공하도록 설계된 NXP i.MX 8X 계열 프로세서는 정교한 다중 코어 중앙 처리 장치(CPU) 아키텍처를 최대한 활용하여 다양한 컴퓨팅 워크로드를 관리합니다(그림 2).

그림 2: NXP i.MX 8X 계열은 Arm Cortex-M4(CM4) 내장형 프로세서와 여러 Arm Cortex-A35 응용 프로세서로 구성된 다중 코어 아키텍처를 사용하여 혼합된 소프트웨어 워크로드를 지원합니다. (이미지 출처: NXP Semiconductors)

그림 2: NXP i.MX 8X 계열은 Arm Cortex-M4(CM4) 내장형 프로세서와 여러 Arm Cortex-A35 응용 프로세서로 구성된 다중 코어 아키텍처를 사용하여 혼합된 소프트웨어 워크로드를 지원합니다. (이미지 출처: NXP Semiconductors)

범용 실시간 처리 작업을 위해 i.MX 8X 장치에는 부동 소수점 처리 장치(FPU), 메모리 보호 장치(MPU), 메모리 매핑 암호화 가속 장치(MMCAU) 및 기타 제어 모듈(MCM)을 탑재한 Arm Cortex-M4(CM4) 프로세서가 포함되어 있습니다. 센서, 액추에이터와 같은 외부 주변 장치를 지원하기 위해 이 사용자 CM4 복합체는 중첩 벡터형 인터럽트 컨트롤러(NVIC)를 포괄적인 인터페이스 및 모듈 세트(저전력 정기 인터럽트 타이머(LPIT), 펄스 폭 변조(PWM), 자동차 및 산업 응용 분야에 일반적으로 필요한 기타 기능 포함)와 결합합니다. 오류 수정 코드(ECC) 기능을 지원하는 캐시 메모리 및 견고하게 결합된 메모리(TCM) 쌍을 활용하여 외부 메모리 액세스를 최소화하고, 실행을 가속화하고, 메모리 오류를 처리할 수 있습니다.

응용 분야의 워크로드를 빠르게 실행하기 위해 CPU 플랫폼은 전력 효율적인 여러 Arm Cortex-A35 응용 프로세서(AP)로 구성됩니다. 예를 들어 8DualXPlus 프로세서(예: MIMX8UX6AVLFZAC)에는 두 개의 AP가 있고 8QuadXPlus 프로세서(예: MIMX8QX6AVLFZAC)에는 네 개의 AP가 있습니다. 전용 명령(I$) 및 데이터(D$) 캐시와 함께 CPU 플랫폼에는 ECC가 탑재된 공유 512Kb 레벨 2(L2) 캐시가 있습니다.

아키텍처의 Arm Cortex-A35 코어는 32비트 하위 호환성과 64비트 성능을 모두 지원하여 소프트웨어 호환성과 성능 확장성을 모두 제공합니다. 신호 처리, 머신 러닝과 같은 컴퓨팅 집약적인 알고리즘을 빠르게 실행하기 위해 Arm Cortex-A35 프로세서는 벡터 부동 소수점(VFP) 처리 및 Arm의 Neon 단일 명령어 다중 데이터(SIMD) 아키텍처 확장을 제공합니다. 이미지 처리, 컴퓨터 비전 및 머신 러닝을 위한 소프트웨어 실행을 가속화하기 위해 Arm Compute Library는 Arm 프로세서 및 그래픽 처리 장치(GPU) 아키텍처에 최적화된 기능을 제공하고, 오픈 소스 Ne10 C 라이브러리는 컴퓨팅 집약적인 작업을 위한 Arm에 최적화된 기능을 제공합니다.

기본 CPU를 오프로드하는 전용 엔진

사용자 CM4 복합체, Arm Cortex-A35 다중 코어 CPU 플랫폼 이외에 이 아키텍처는 멀티미디어 응용 분야를 위한 추가적인 전용 엔진을 제공합니다. 오디오 및 음성 코덱 처리를 위한 디지털 신호 처리(DSP)와 함께 이 아키텍처는 GPU와 비디오 처리 장치(VPU)를 통합합니다. 장치의 GPU는 표준 그래픽 라이브러리를 지원하며, 16개의 실행 장치와 고성능 2D 비트 블릿 엔진이 탑재된 4개의 개별 4성분 부동 소수점 벡터(vec4)를 사용하여 작업을 가속화합니다. VPU는 주요 비디오 형식을 처리하며, 디코딩을 최대 4Kp30(점진적 30Hz)로 가속화하고 인코딩을 최대 1080p30으로 가속화합니다. 따라서 칩의 전용 디스플레이 컨트롤러 블록은 최대 3개의 독립 디스플레이에 대한 그래픽 출력을 구동할 수 있습니다.

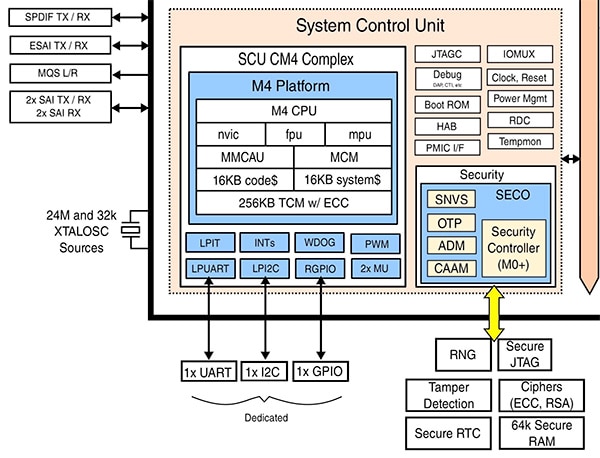

또한 성능을 최대화하기 위해 i.MX 8X 아키텍처는 시스템 관리 및 보안 서비스를 실행하는 데 일반적으로 포함되는 추가 처리 부하에서 기본 CPU 플랫폼이 벗어나도록 고안된 추가 프로세서 코어를 통합합니다. 시스템 관리를 위해 아키텍처의 시스템 제어 장치(SCU)는 사용자 CM4 복합체와 일치하지만 SCU 작업을 전담하고 개발자는 사용할 수 없는 CM4 복합체를 통합합니다(그림 3).

그림 3: NXP i.MX 8X 프로세서에 통합되어 있고 개발자는 사용할 수 없는 SCU는 전용 Arm Cortex-M4(CM4) 서브 시스템을 사용하여 장치의 기본 프로세서에서 시스템 관리 작업을 오프로드합니다. (이미지 출처: NXP Semiconductors)

그림 3: NXP i.MX 8X 프로세서에 통합되어 있고 개발자는 사용할 수 없는 SCU는 전용 Arm Cortex-M4(CM4) 서브 시스템을 사용하여 장치의 기본 프로세서에서 시스템 관리 작업을 오프로드합니다. (이미지 출처: NXP Semiconductors)

전력 관리, 클로킹 및 기타 내부 기능과 함께 SCU는 일반 작업에서 핀 멀티플렉싱 및 입/출력(I/O) 채널 구동 강도를 제어합니다. 실제로 사용자 CM4 복합체와 Arm Cortex-A35 AP는 이러한 하위 수준 하드웨어 기능에 직접 액세스할 수 없습니다. 대신 SCU는 이러한 기능을 추상화하므로, 사용자 CM4 또는 AP에서 실행 중인 소프트웨어에서 펌웨어 응용 프로그래밍 인터페이스(API) 기능을 호출하면 불필요한 전력 도메인 전원 차단과 같은 기능이 수행됩니다. 예를 들어 해당 전력 도메인을 다른 프로세서와 공유 중인 경우 SCU는 전력 차단 요청을 승인하되 다른 프로세서에서 전력 차단 요청을 실행할 때까지 도메인의 전력을 유지합니다.

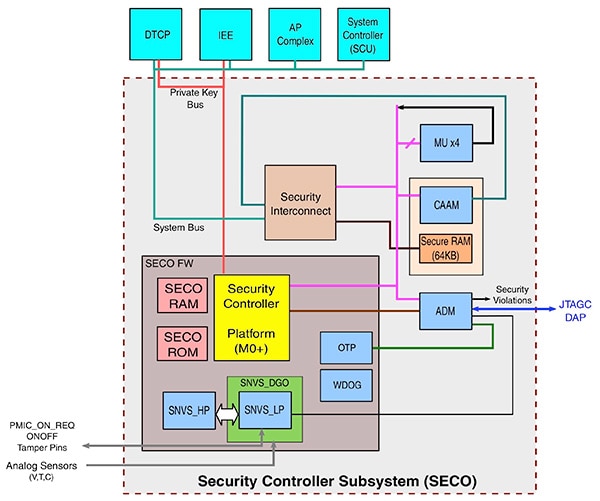

i.MX 8X 장치의 포괄적인 보안 지원을 관리하기 위해 다른 전용 프로세서가 장치의 보안 컨트롤러(SECO) 서브 시스템에서 작동합니다. SECO 서브 시스템 내에서 통합 저전력 Arm Cortex-M0+ 프로세서는 보안 키에 대한 비공개 버스 액세스, 보안 키 스토리지를 위한 일회성 프로그래밍 가능(OTP) 메모리, 추가 비공개 데이터 또는 임시 키를 위한 보안 비휘발성 스토리지(SNVS)를 비롯한 하드웨어 기반 보안 기능을 지원하는 펌웨어를 실행합니다(그림 4).

그림 4: NXP i.MX 8X 보안 컨트롤러(SECO) 서브 시스템 내에서 전용 저전력 Arm Cortex-M0+ 프로세서는 보안 스토리지, 암호화 가속 및 인증된 디버그 액세스를 위해 개인 키 버스와 여러 하드웨어 모듈에 의존하여 보안 작업을 관리합니다. (이미지 출처: NXP Semiconductors)

그림 4: NXP i.MX 8X 보안 컨트롤러(SECO) 서브 시스템 내에서 전용 저전력 Arm Cortex-M0+ 프로세서는 보안 스토리지, 암호화 가속 및 인증된 디버그 액세스를 위해 개인 키 버스와 여러 하드웨어 모듈에 의존하여 보안 작업을 관리합니다. (이미지 출처: NXP Semiconductors)

이러한 핵심 보안 메커니즘뿐 아니라 SECO 서브 시스템은 인증된 디버그 모듈(ADM)을 통해 조정되는 보안 디버그와 조작 감지를 위한 보안 작업을 조정합니다. 안전한 실행을 위해 통합 CAAM(암호화 가속 및 보증 모듈) 하드웨어 보안 모듈은 대칭 및 비대칭 암호화, 해시 함수, 난수 생성기(RNG)를 비롯한 전체 보안 알고리즘 제품군을 지원합니다.

일반 작업에서 SCU, AP, 디지털 전송 콘텐츠 보호(DTCP) 가속기를 비롯한 소자 처리 장치는 SECO 보안 상호 연결을 사용하여 시스템 버스를 통해 CAAM 기능에 액세스합니다. CAAM 직접 메모리 액세스(DMA) 기능을 통해 액세스하는 이외에 SECO의 전용 Cortex-M0+ 프로세서는 시스템 버스에 액세스할 수 없습니다. 대신 보호된 내부 연결을 사용하여 주변 장치, 보안 RAM, 읽기 전용 메모리(ROM) 및 특수 개인 키 버스에 액세스합니다.

DTCP 가속기 사용과 함께 이 개인 키 버스는 i.MX 8X 프로세서에서 즉석 암호화 및 암호 해독을 지원하는 데 중요한 역할을 합니다. 여기서 보안 프로세서는 해당 리소스를 사용하여 장치의 인라인 암호화/암호 해독 엔진(IEE) 모듈에서 요청 프로세서, DMA 컨트롤러 또는 I/O 장치의 개입 없이 암호화된 스토리지에서 읽거나 쓰는 데 필요한 개인 키를 제공합니다.

장치의 Cortex-A35 프로세서에 통합된 Arm의 TrustZone 기술을 기반으로 하여 구축된 SECO 서브 시스템은 보안 부트 공정 중에 SCU에서 작동합니다. 이 공정에서 SCU는 부트 설정을 해석하고, 부트 소스를 구성하고, 부트 이미지를 내부 또는 외부 메모리로 로드합니다. SECO 서브 시스템은 암호화 기능을 사용하여 서명된 펌웨어 이미지를 로드 후 실행되기 이전에 인증합니다.

중요 디스플레이 및 제어 기능 보호

자동차 및 산업 부문과 같은 핵심 응용 분야에서는 다양한 워크로드를 효과적이고 안전하게 처리하는 기능도 중요하지만, 주요 기능을 보호하는 것도 마찬가지로 중요합니다. NXP의 i.MX 8X 제품군은 처리 기능에 이러한 중요 요구 사항을 충족하는 데 필요한 안전 인증 가능 기능을 더했습니다.

프로세서 제품군의 안전 지원은 시스템 신뢰성을 개선하는 FD-SOI(완전 공핍형 실리콘 온 인슐레이터) 공정 기술로 제조를 시작하여 다양한 수준으로 제작됩니다. 시스템 안전은 강력한 보안 기반에 의존하므로 TrustZone 지원 AP, SECO 서브 시스템 및 보안 부트 기능을 조합하여 안전 및 보안에 대한 위협을 제거하는 데 필요한 신뢰할 수 있는 환경을 제공할 수 있습니다.

동시에 사용자 CM4 복합체를 통해 시간 결정적 작업을 독립적으로 처리하고 중요 시스템 작업을 SCU 및 SECO 서브 시스템에 오프로드할 수 있으므로 다양한 공정 부하에도 불구하고 핵심 응용 분야 기능을 사용 가능한 상태로 유지할 수 있습니다. 실제로 NXP는 이 개념을 확장하여 자동차 안전 무결성 수준 B(ASIL B) 지원 하드웨어 디스플레이 장애 조치 경로를 i.MX 8X 장치에 통합하는 자사의 SafeAssure 기술을 통해 핵심 디스플레이를 지원합니다. SafeAssure를 사용하면 장치에서 데이터 무결성 또는 GPU 오류가 감지될 경우 장애 조치 이미지가 자동으로 제공됩니다. 이 장애 조치 이미지는 백그라운드에서 실행되며, 기본 디스플레이가 고장난 동안에도 중요 정보를 가용한 상태로 유지합니다.

안전 응용 분야에 대한 지원이 i.MX 8X 기반 시스템의 메모리 액세스로 확장됩니다. 지원되는 메모리 인터페이스 중에 i.MX 8X 장치는 이중 데이터 전송률 3 저전압(DDR3L) 메모리를 위한 8비트 ECC를 제공합니다. L2 캐시의 ECC와 함께(그림 2 참조) 이 DDR3L ECC 기능은 산업 안전 무결성 수준 3(SIL 3)을 지원합니다. 또한 i.MX 8X 아키텍처는 ECC 지원을 외부 플래시 스토리지 장치로 확장합니다. 여기서 통합 Bose, Ray-Chaudhuri, Hocquenghem(BCH) 인코더 및 디코더 모듈은 이러한 스토리지 장치에서 읽은 데이터 블록 내에서 2개 ~ 20개 단일 비트 오류를 연결할 수 있는 62비트 ECC를 제공합니다.

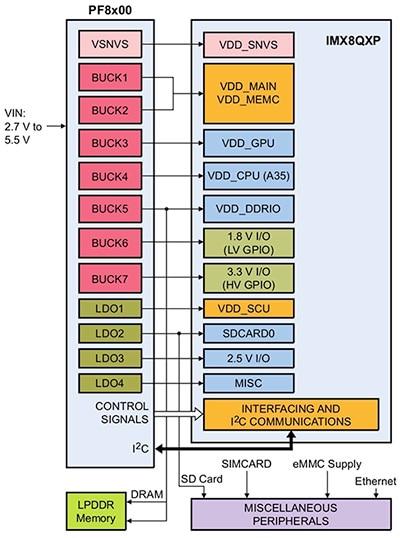

i.MX 8X 기반 응용 제품 가동

동급의 다른 프로세서와 마찬가지로 i.MX 8X 기반 설계를 구현하려면 중요 전력 시퀀스를 비롯하여 전력과 관련된 엄격한 요구 사항을 준수해야 합니다. i.MX 8X 장치를 켜려면 SVNS 서브 시스템부터 SCU, I/O 및 메모리 인터페이스, 나머지 장치까지 네 공급 그룹을 동시에 또는 순차적으로 구동해야 합니다. 개발자는 NXP의 PF8x00 전력 관리 집적 회로(PMIC) 장치를 사용하여 간단히 충족할 수 있습니다. 이 장치는 i.MX 8X 프로세서와 외부 메모리 및 일반 시스템 주변 장치를 지원하는 데 필요한 전체 전압 레일 및 제어 신호를 제공합니다(그림 5).

그림 5: NXP PF8x00 PMIC는 i.MX 8X 프로세서를 구동하는 데 필요한 전체 전압 레일 및 제어 신호를 제공합니다. (이미지 출처: NXP Semiconductors)

그림 5: NXP PF8x00 PMIC는 i.MX 8X 프로세서를 구동하는 데 필요한 전체 전압 레일 및 제어 신호를 제공합니다. (이미지 출처: NXP Semiconductors)

자체 i.MX 8X 기반 설계를 구성할 때 개발자는 8QuadXPlus 프로세서(예: MIMX8QX6AVLFZAC)에서 사용하도록 미리 프로그래밍되어 있는 NXP MC33PF8100CCES PMIC를 사용할 수 있습니다. 다른 PF8x00 변형(예 MC33PF8100A0ES 및 MC33PF8200A0ES)은 i.MX 8X 프로세서를 지원하지만 미리 프로그래밍되어 있지 않습니다.

안전 응용 분야에서 PF8200 계열 장치(예: MC33PF8200A0ES)는 ASIL B 시스템을 지원하도록 설계된 기능을 통합합니다. 전용 밴드갭 레퍼런스가 있는 출력 전압 모니터를 비롯한 여러 내부 모니터와 함께 PF8200 PMIC에는 고장 시 안전 출력(FSOB) 핀이 포함되어 있어 전원을 켜거나 정전 중에도 시스템을 안전하게 유지합니다. 또한 자체 시험 루틴에서 다른 장치 기능을 확인하는 동안 아날로그 내장형 자체 시험(ABIST) 루틴은 모든 전압 모니터를 테스트합니다.

PF8x00 PMIC는 i.MX 8X 기반 시스템의 하드웨어 설계를 간소화할 수 있지만, 개발자에 따라 i.MX 8X 장치 평가를 즉시 시작하고 i.MX 8X 기반 응용 제품의 시제품을 빠르게 제작해야 할 수 있습니다. NXP의 MCIMX8QXP-CPU i.MX 8X MEK(다중 감각 인에이블먼트 키트)는 NXP i.MX 8QuadXPlus 프로세서, NXP F8100 PMIC, 3GB RAM, 32GB 내장형 멀티미디어 컨트롤러(eMMC) 메모리 및 64MB 플래시 메모리를 결합하는 준비된 개발 플랫폼을 제공합니다. 디스플레이, 카메라 및 오디오 인터페이스와 함께 MEK 기판에는 자동차 또는 산업 응용 분야에서 일반적으로 사용되는 센서가 포함되어 있습니다. 추가 연결, 오디오 및 확장 옵션을 위해 개발자는 NXP의 선택적 MCIMX8-8X-BB 베이스 기판을 추가할 수 있습니다.

결론

자동차, 산업, 건물 관리, HMI를 비롯하여 점점 더 많은 응용 분야에서 멀티미디어 그래픽을 통한 기존 실시간 I/O 처리와 새롭게 등장한 응용 제품 레벨 처리를 모두 포함하도록 처리 워크로드를 확장했습니다. 각 워크로드 유형에 대한 설계 옵션이 존재하지만 자동차 및 산업 응용 분야에서 안전 인증 가능 설계 요구 사항을 충족할 수 있는 전력 효율적이며 고성능 솔루션에 대한 높아지는 요구를 충족하는 솔루션은 많지 않습니다.

위에서 살펴본 바와 같이 NXP Semiconductors의 다중 코어 프로세서 제품군을 사용하는 개발자는 다양한 요구 사항을 충족할 수 있는 설계를 보다 효과적으로 구현하고 손쉽게 확장하여 높은 성능에 대한 새로운 요구 사항을 해결할 수 있습니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.