IoT 보안 기본 사항 - 2부: 암호 보호

DigiKey 북미 편집자 제공

2020-06-11

편집자 주: IoT 장치의 확산에도 불구하고 공격이 성공할 경우 회사 데이터와 개인 데이터가 손상될 수 있는 산업용 IoT(IIoT)와 핵심 응용 분야에서 보안 위협은 연결 장치를 채택하는 데 장벽이 되는 만큼, 이러한 장치를 보호하는 것은 지속적인 문제로 남아 있습니다. IoT 응용 제품을 보호하는 것은 까다로울 수 있지만 개발자는 결합되면 복잡해 보이는 여러 보안 메커니즘, 프로토콜 및 정책을 조율해야 합니다. 실제로 IoT 장치 보안은 하드웨어 보안 장치에서 지원되는 상대적으로 간단한 몇 가지 원칙에 기반할 수 있습니다. 체계적인 보안 방법에 따라 문제를 해결할 수 있습니다. 여러 단원으로 구성된 이 시리즈에서는 개발자가 시작 단계부터 모범 사례를 따르도록 도와주는 실용적인 지침을 제공합니다. 1부에서는 보안 설계의 기반이 되는 암호화 알고리즘에 대해 설명합니다. 이번 2부에서는 보안 IoT 설계에서 개인 키, 키 관리 및 보안 스토리지의 역할에 대해 설명합니다. 3부에서는 IoT 장치에 대한 다른 유형의 위협을 완화하기 위해 보안 프로세서를 기반으로 구축된 메커니즘을 살펴봅니다. 4부에서는 고급 프로세서에 보안 메커니즘을 적용하여 IoT 장치의 런타임 환경에서 공격을 완화하는 데 필요한 분리 상태를 보장하는 방법을 확인하고 보여줍니다. 5부에서는 이러한 장치를 IoT 클라우드 리소스에 연결하는 데 사용되는 더 높은 수준의 보안 조치까지 IoT 장치의 보안을 계속해서 살펴봅니다.

하드웨어 기반 암호화 장치는 사물 인터넷(IoT)의 취약성을 완화할 수 있지만, 아무리 강력한 암호화 장치를 사용하더라도 보안 키 및 연결된 데이터를 충분히 보호하지 못한다면 보안이 약화될 수 있습니다. 반도체 제조업체에서는 특수 보안 IC 및 프로세서에 내장된 다양한 메커니즘을 통해 키와 기타 권한 있는 데이터를 보호합니다.

이 기사에서는 암호화에서 키의 중요한 역할을 검토하고 Maxim Integrated, NXP, STMicroelectronics 및 Microchip Technology에서 제공하는 장치에 내장된 다양한 키 보호 메커니즘에 대해 설명합니다.

암호화에서 보안 키의 역할

이 시리즈의 1부에서 설명한 대로 다양한 하드웨어 지원 암호화 알고리즘을 사용하여 고유한 메시지 해시 또는 서명을 생성할 수 있으며, 광범위한 암호화 방식으로 일반 텍스트를 암호 텍스트로 암호화하고 암호 텍스트를 일반 텍스트로 암호 해독할 수 있습니다. 이러한 알고리즘으로 모든 응용 제품의 보안을 강화할 수 있지만, 응용 제품을 보호하는 기능은 근본적으로 암호화 알고리즘에 사용되는 개인 키와 기타 보안 데이터에 대한 보안에 따라 달라집니다.

암호화에서 손상된 암호란 해당 암호를 기반으로 하는 보안 정책, 프로토콜 및 메커니즘에서 손상된 보안을 의미합니다. 오래전 19세기에 암호 해석가인 Auguste Kerckhoffs는 '키가 안전하게 유지되는 한 암호화 시스템은 안전하다'고 말했으며, 이 원칙은 현재 Kerckhoffs의 원리라고 불립니다. 간단히 말해서 "적들도 시스템을 알고 있다(the enemy knows the system)."라고 하며, 이를 정보 이론의 아버지인 Claude Shannon의 이름을 따서 Shannon의 원리라고 합니다.

실제로 개발자는 잘 알려진 알고리즘을 토대로 보안 시스템을 구축하므로, 엄밀히 말해서 반도체 제조업체에서는 하드웨어 가속 보안 장치에서 보안 시스템에서 보안 시스템을 안심하고 사용할 수 있습니다. 하지만 궁극적으로 이러한 시스템을 보호하는 것은 해당 알고리즘에 사용되는 암호입니다.

암호 보호 과제

개념적으로는 암호화에서 암호를 보호하는 것이 간단하지만 실제로는 매우 까다로울 수 있습니다. 높은 수준의 보안 정책을 구현하려면 불가피하게 알고리즘이 서로 다른 여러 보안 프로토콜을 사용해야 합니다. 즉, 이러한 프로토콜 및 알고리즘에서는 프로토콜 자체에서 생성되는 정적 키와 임시 키를 조합해야 합니다. 예를 들어 TLS(Transport Layer Security) 세션에서는 인증 중에 정적 키를 사용하고 보안 메시지 교환 중에 공유 임시 세션 키를 사용합니다.

실제로 U.S. NIST(National Institute of Standards and Technology)에서는 보호되어야 하는 19가지 키와 기타 11가지 관련 정보(예: 타원 곡선 도메인 파라미터, 중간 결과)를 식별합니다. 또한 NIST는 보안을 강화하려면 키 사용과 연관된 정보를 표 1에 명시된 기간 동안 보호할 것을 권장합니다. 이 표에는 전체 NIST 권장 목록에 나열된 키 유형 중 처음 몇 개만 나와 있습니다[1].

표 1: 이 표에는 전체 NIST 권장 목록에서 지정된 기간 동안 보호되어야 하는 키 유형 및 연결된 정보 중 일부만 나열됩니다. (표 출처: Digi-Key Electronics, NIST 자료 사용) |

키 및 연결된 데이터를 보호해야 한다는 것은 개발자가 IoT 응용 제품 내에서 암호를 사용할 때 세심한 주의를 기울여야 한다는 것을 의미합니다. IoT 장치의 경우 각 상태(유휴, 전송 중, 사용 중)의 데이터를 보호해야 하는 중요한 과제가 있습니다. 유휴 상태의 데이터를 보호하려면 보안 스토리지 메커니즘이 필요하고, 전송 중인 데이터를 보호하려면 네트워크 또는 시스템 버스를 통해 전송 중인 동안 암호를 보호할 수 있는 방법이 필요하고, 사용 중인 데이터를 보호하려면 암호화 알고리즘을 실행하는 동안 사용 중 노출을 방지할 수 있는 방법이 필요합니다. 다행히 개발자가 다양한 메커니즘을 사용하여 보안 데이터를 보호할 수 있는 광범위한 보안 장치가 있습니다.

암호화 지원 반도체에서 암호를 보호하는 방법

고급 암호화 지원 반도체 솔루션은 일반적으로 키와 기타 보안 데이터를 저장할 수 있는 일부 유형의 보안된 비휘발성 메모리를 제공하지만, 보안 장치의 두 기본 클래스인 특수 보안 IC와 암호화 지원 프로세서의 전체적인 접근 방식은 본질적으로 큰 차이가 있습니다.

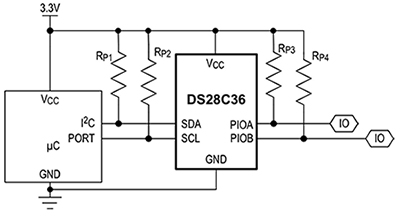

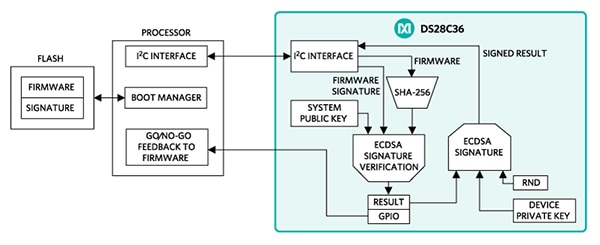

보안 IC는 일반적으로 직렬 버스를 통해 전달되는 호스트 프로세서에서 알고리즘 실행을 오프로드하는 자급형 서브 시스템 역할을 하도록 설계되었습니다. 예를 들어 Maxim Integrated의 DS28C36 보안 인증자는 호스트 프로세서에 인증 성공 또는 실패 신호를 제공하는 데 사용될 수 있는 두 범용 I/O(GPIO)와 I2C 포트를 제공합니다(그림 1).

그림 1: Maxim Integrated DS28C36 보안 인증자와 같은 보안 장치는 내부 키 및 작업 보호 기능을 강화하면서 통합을 간소화하는 전체 서브 시스템을 제공합니다. (이미지 출처: Maxim Integrated)

그림 1: Maxim Integrated DS28C36 보안 인증자와 같은 보안 장치는 내부 키 및 작업 보호 기능을 강화하면서 통합을 간소화하는 전체 서브 시스템을 제공합니다. (이미지 출처: Maxim Integrated)

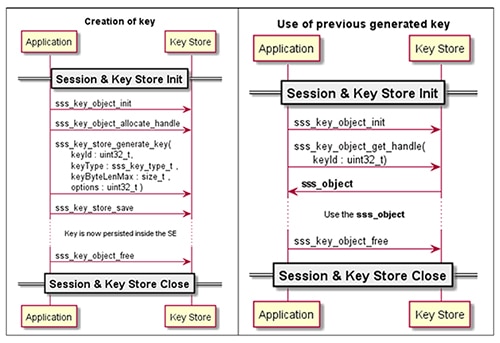

일반적으로 소프트웨어 통합은 간단합니다. 예를 들어 NXP의 Plug & Trust 미들웨어 라이브러리는 SE050 및 A71CH 보안 소자 장치의 하드웨어 기능을 일부 함수 호출로 추상화합니다(그림 2).

그림 2: NXP의 Plug & Trust 미들웨어와 같은 소프트웨어 라이브러리를 활용하면 개발자가 일부 직관적인 함수 호출을 사용하여 키를 생성(왼쪽) 및 액세스(오른쪽)하고 NXP의 SE050 및 A71CH 보안 소자 장치에서 기본 기능을 최대한 활용할 수 있습니다. (이미지 출처: NXP)

그림 2: NXP의 Plug & Trust 미들웨어와 같은 소프트웨어 라이브러리를 활용하면 개발자가 일부 직관적인 함수 호출을 사용하여 키를 생성(왼쪽) 및 액세스(오른쪽)하고 NXP의 SE050 및 A71CH 보안 소자 장치에서 기본 기능을 최대한 활용할 수 있습니다. (이미지 출처: NXP)

새로운 키(그림 2, 왼쪽)를 생성하면 keyId가 반환됩니다. 나중에 키를 사용하기 위해 개발자는 시스템 버스를 통해 실제 키 값을 노출하는 대신 keyId로 키를 나타냅니다(그림 3, 오른쪽). NXP의 Plug & Trust 미들웨어를 사용하여 개발자는 Arduino 호환 NXP Kinetis Freedom K64F 평가 기판을 SE050 개발용 NXP OM-SE050ARD 확장 기판 또는 AC71CH 개발용 NXP OM3710/A71CHARD 기판과 함께 사용하여 보안 응용 제품을 빠르게 구현할 수 있습니다.

Maxim Integrated의 DS28C36, NXP의 SE050, NXP의 AC71CHTK2/TOBC2VJ 및 이 클래스의 다른 장치와 같은 전용 보안 IC는 몇 가지 뚜렷한 이점을 제공합니다. 설계에 보안 기능을 추가하는 상대적으로 간단한 방법을 제공할 뿐 아니라 전용 보안 IC에 기능을 통합하여 보안 데이터 노출과 운영을 제한합니다. 예를 들어 Maxim Integrated DS28C36은 하드웨어 암호화 가속기, 난수 생성기, 8Kb 보안 EEPROM을 기타 기능 블록과 통합합니다. DS28C36은 타원 곡선 디지털 서명 알고리즘(ECDSA) 펌웨어 서명을 인증할 때, 개인 키, 연결된 데이터(그림 1 참조) 및 해당 암호를 사용하는 작동이 장치 내에 국한하여 유지되므로 유휴, 전송 중 및 사용 중인 데이터 보호를 보장합니다(그림 3).

그림 3: Maxim Integrated DS28C36과 같은 보안 장치의 통합 기능은 개인 키와 연결된 데이터가 칩 내에 국한하여 유지되는 것을 의미합니다. (이미지 출처: Maxim Integrated)

그림 3: Maxim Integrated DS28C36과 같은 보안 장치의 통합 기능은 개인 키와 연결된 데이터가 칩 내에 국한하여 유지되는 것을 의미합니다. (이미지 출처: Maxim Integrated)

프로세서 기반 보안 키 보호

모든 IoT 설계에서 전용 보안 IC를 수용할 수 있는 것은 아닙니다. 요구 사항에서는 실장 면적, 부품 명세서(BOM), 비용, 고객 사양 등과 관련한 기타 암호화 방법 또는 설계 제약 조건의 사용을 규정할 수 있습니다. 이러한 설계에서 STMicroelectronics의 STM32WB55 및 Microchip Technology의 ATSAML11과 같은 보안 지원 프로세서는 암호화 알고리즘 하드웨어 가속 엔진 및 보안 데이터 보호 메커니즘 조합을 제공합니다. 이 기사에서는 키 보호를 중심으로 살펴보지만, 이러한 프로세서에서는 이 시리즈의 3부에서 살펴볼 많은 정교한 추가 보안 기능을 제공합니다.

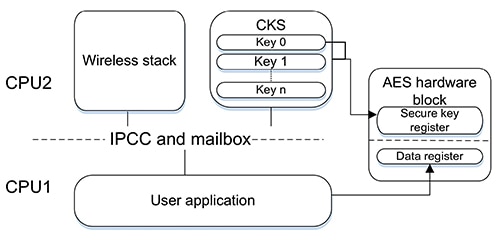

STMicroelectronics의 이중 코어 STM32WB55 무선 장치에서 Arm® Cortex®-M4 CPU(CPU1)는 전용 프로세서 간 통신 컨트롤러(IPCC) 및 세마포 메커니즘(HSEM)을 통해 무선 서브 시스템의 전용 Arm Cortex-M0+ 마이크로 컨트롤러(CPU2)와 통신하여 호스트 프로세서 역할을 합니다. CPU2 서브 시스템 내에서 보안 메모리는 고급 암호화 표준(AES) 하드웨어 가속기에 사용되는 키를 위한 고객 키 스토리지(CKS) 영역을 제공합니다(그림 4).

그림 4: STMicroelectronics의 이중 코어 STM32WB55 프로세서를 사용하면 무선 서브 시스템 코어(CPU2)를 통해서만 키에 액세스할 수 있지만, 호스트 코어(CPU1)에서 실행 중인 신뢰할 수 있는 응용 제품에서 키를 간접적으로 사용할 수 있습니다. (이미지 출처: STMicroelectronics)

그림 4: STMicroelectronics의 이중 코어 STM32WB55 프로세서를 사용하면 무선 서브 시스템 코어(CPU2)를 통해서만 키에 액세스할 수 있지만, 호스트 코어(CPU1)에서 실행 중인 신뢰할 수 있는 응용 제품에서 키를 간접적으로 사용할 수 있습니다. (이미지 출처: STMicroelectronics)

STM32WB55 아키텍처는 디버그 포트를 통한 액세스 또는 호스트 CPU1을 실행 중인 비보안 루틴을 통한 액세스로부터 CKS 키를 보호합니다. 동시에 호스트 CPU1에서 실행 중인 신뢰할 수 있는 응용 제품에서 키 인덱스를 통해 참조하여 AES 암호화에서 특정 CKS 키를 사용할 수 있습니다. AES 하드웨어 블록은 내부 버스를 통해 CKS 영역에서 원하는 키를 수신하여, 키 전송이 CPU2 서브 시스템 내에서 보호된 상태로 유지되도록 합니다.

Arm Cortex-M23-based ATSAML11 프로세서의 경우 Microchip Technology는 Arm TrustZone 기술에 내장된 보안 기능을 사용합니다. TrustZone은 하드웨어 기반 메커니즘을 사용하여 신뢰할 수 있는 리소스와 신뢰할 수 없는 리소스 사이를 분리합니다.

ATSAML11 프로세서에서 Microchip은 TrustZone IDAU(Implementation Defined Attribution Unit)를 사용하여 보안 응용 코드와 비보안 응용 코드를 통해 메모리의 하위 영역에 대한 차동 액세스 제어를 비롯한 보안 정책을 시행합니다. 256바이트 보안 RAM 영역(TrustRAM)에서는 임시 키를 위한 추가 보안 스토리지를 제공합니다.

보안 프로비저닝

전용 보안 IC 및 프로세서는 개발자가 IoT 장치에서 보안 키 및 연결된 데이터를 보호하는 데 필요한 메커니즘을 제공합니다. 하지만 보안 키가 도난에 노출되어 보안 키 또는 인증서를 사용하여 보안 IC 또는 공정을 처음에 로드하거나 프로비저닝하는 데 사용되는 공정이 실패할 경우 보안 취약성이 발생할 수 있습니다. 사이버 범죄자는 그런 도난 키 및 손상된 인증서를 암시장을 통해 빠르게 판매하여 해커가 유효해 보이는 자격 증명으로 보안 네트워크를 침투할 수 있게 합니다.

이 시리즈의 4부에서는 Amazon Web Services, Microsoft Azure, Google Cloud 등을 비롯한 특정 IoT 클라우드 서비스에 대한 키 및 인증서를 사용하여 제조업체에서 사전에 프로비저닝되는 보안 장치 및 개발 키트에 대해 설명합니다. 하지만 프로덕션 배포의 경우 개발자는 자체 맞춤형 키 및 인증서를 사용하는 것을 선호하거나 사용해야 하는 것이 가장 일반적입니다.

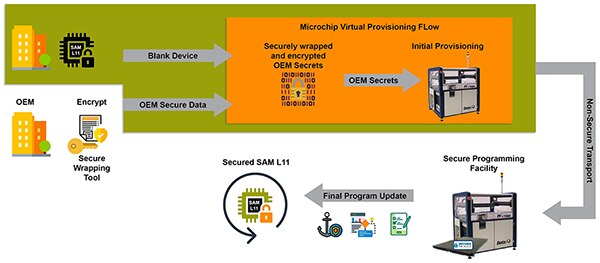

맞춤형 프로비저닝을 지원하기 위해 대부분의 반도체 제조업체에서는 자체 시설에서 또는 프로비저닝 파트너와 협력하여 프로비저닝을 제공합니다. 예를 들어 Microchip은 Trustonic 및 IAR Systems의 Secure Thingz를 비롯한 타사 파트너가 제공하는 프로비저닝 키트에 포함된 보안 랩핑 도구를 사용하여 생성된 맞춤형 암호로 장치를 프로비저닝합니다(그림 5).

그림 5: 주문자 상표 부착(OEM) 개발자는 보안 랩핑 도구를 사용하여 제조 파트너의 보안 프로그래밍 시설에서 나중에 Microchip SAML11과 같은 보안 마이크로 컨트롤러를 프로비저닝하는 데 사용되는 암호를 보호할 수 있습니다. (이미지 출처: Microchip Technology)

그림 5: 주문자 상표 부착(OEM) 개발자는 보안 랩핑 도구를 사용하여 제조 파트너의 보안 프로그래밍 시설에서 나중에 Microchip SAML11과 같은 보안 마이크로 컨트롤러를 프로비저닝하는 데 사용되는 암호를 보호할 수 있습니다. (이미지 출처: Microchip Technology)

생산 준비가 되면 OEM 개발자는 보안 랩핑 도구를 사용하여 Microchip 공장에 키 및 인증서를 암호화된 형식으로 제공합니다. 이러한 키와 인증서는 파트너의 보안 프로그래밍 시설 내에 있는 하드웨어 보안 모듈에서만 암호 해독할 수 있습니다. 이 접근 방식은 비보안 네트워크를 통한 생산 정보 교환 요구 사항을 충족하면서 생산 지원 장치에 안전하게 프로비저닝된 키 및 펌웨어를 제공합니다.

PUF 기술을 통한 자체 프로비저닝

보안 지원 프로세서 및 전용 IC에서 PUF(Physical Unclonable Function) 기술 사용이 증가하면서 훨씬 안전한 프로비저닝 방식이 제공됩니다. 보안 키를 장치에 명시적으로 로드하는 대신 PUF 기술을 활용하면 보안 장치에서 각 장치의 고유한 특성에서 도출된 보안 키를 사용할 수 있습니다.

PUF 기술에서는 제조 변화와 기타 물리적 공정을 사용하여 장치 자체에 고유하고 정상 시스템 작동 중에 반복 가능한 값을 생성합니다. 아래 설명한 대로 결과 값은 각 PUF 지원 장치에 내장된 보안 키를 제공하여 암호화에 대한 고유한 개인 키 역할을 합니다.

자체 프로비저닝을 지원할 뿐 아니라 PUF 기술은 다른 보안 층을 추가합니다. 장치에 침투하여 장치에 고유한 값을 노출하려고 시도하면 값을 생성하는 데 사용되는 특성이 변경되므로 생성되는 값이 변경됩니다.

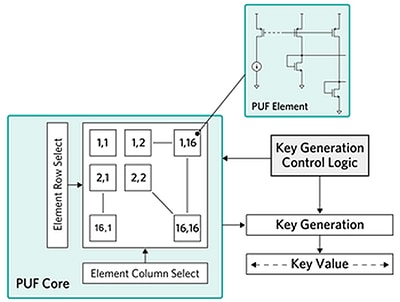

다른 PUF 메커니즘이 존재하지만 기본 접근 방식은 PUF 지원 장치 간에 거의 동일하게 유지됩니다. 예를 들어 MAX32520 보안 마이크로 컨트롤러와 일부 보안 IC에 사용되는 Maxim Integrated의 ChipDNA PUF 기능은 아날로그 PUF 요소 및 제어 논리 어레이를 사용하여 키를 생성합니다(그림 6).

그림 6: Maxim Integrated의 ChipDNA PUF 기술에서는 임의 상태의 PUF 요소 어레이를 온칩 제어 논리에서 일관된 서비스별 키를 생성하는 데 사용합니다. (이미지 출처: Maxim Integrated)

그림 6: Maxim Integrated의 ChipDNA PUF 기술에서는 임의 상태의 PUF 요소 어레이를 온칩 제어 논리에서 일관된 서비스별 키를 생성하는 데 사용합니다. (이미지 출처: Maxim Integrated)

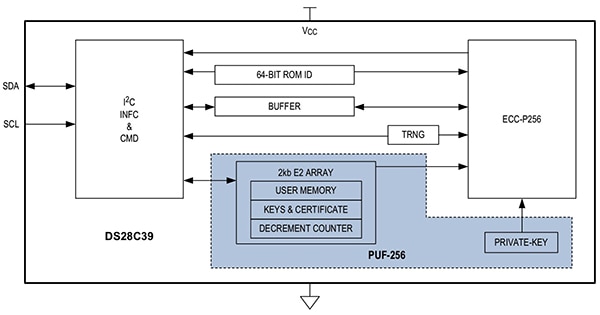

Maxim Integrated의 DS28C39 ECDSA 보안 인증자에서는 ChipDNA PUF 출력이 ECDSA 작동 및 연결된 데이터 보호를 위한 개인 키로 사용됩니다(그림 7).

그림 7: Maxim Integrated의 DS28C39 ECDSA 보안 인증자는 온칩 ChipDNA PUF 회로에서 생성되는 개인 키를 사용합니다. (이미지 출처: Maxim Integrated)

그림 7: Maxim Integrated의 DS28C39 ECDSA 보안 인증자는 온칩 ChipDNA PUF 회로에서 생성되는 개인 키를 사용합니다. (이미지 출처: Maxim Integrated)

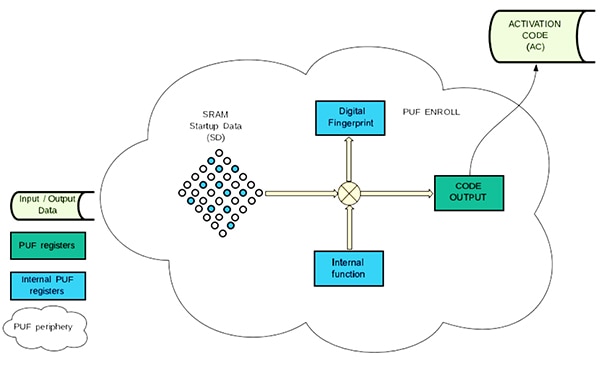

PUF 지원 LPC55S 프로세서 제품군의 경우 NXP는 최초 임의 상태의 SRAM 어레이에서 생성되는 출력을 기반으로 PUF 기술을 사용합니다(그림 8).

그림 8: PUF 구현에서 NXP의 LPC55S 프로세서 제품군은 SRAM의 시작 데이터를 사용하여 디지털 지문 및 연결된 활성화 코드를 생성합니다. 이 코드는 나중에 디지털 지문을 복원하고 개인 키를 암호화하거나 생성하는 데 사용됩니다. (이미지 출처: NXP)

그림 8: PUF 구현에서 NXP의 LPC55S 프로세서 제품군은 SRAM의 시작 데이터를 사용하여 디지털 지문 및 연결된 활성화 코드를 생성합니다. 이 코드는 나중에 디지털 지문을 복원하고 개인 키를 암호화하거나 생성하는 데 사용됩니다. (이미지 출처: NXP)

이러한 장치에서 PUF는 고유한 디지털 지문 및 연결된 활성화 코드를 생성하는 등록 작업부터 사용되며 새 등록 작업이 실행될 때까지 유효한 상태로 유지됩니다. 장치의 보호된 플래시에 저장되는 활성화 코드를 사용하면 장치에서 전원을 켤 때 일관되게 생성되는 SRAM 시작 데이터로부터 디지털 지문을 재구성할 수 있습니다.

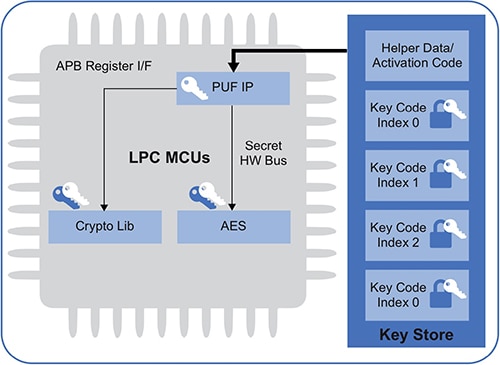

디지털 지문을 적용한 상태로 개발자는 자체 키를 암호화하거나 키를 생성할 수 있습니다. 이 공정에서 장치는 키 코드를 반환합니다. 개발자는 활성화 코드, 키 코드 및 인덱스를 제공하여 장치가 적절한 온칩 키 슬롯에서 원하는 개인 키를 암호 해독한 후 암호화 소프트웨어 라이브러리에 전달하도록 할 수 있습니다. 키 슬롯 0은 내부 버스를 통해 프로세서의 AES 하드웨어 암호화 엔진에 직접 키를 제공하는 특수 키 암호 해독 방법을 제공합니다(그림 9).

키 암호화 및 암호 해독 역할에서 LPC55S의 PUF 디지털 서명은 유휴 상태 또는 전송 중인 보안 데이터의 보호를 강화하는 데 기본적으로 사용되는 키 암호화 키(KEK) 역할을 합니다. KEK를 사용하면 보안 데이터를 보호하는 데 필요한 더 큰 보안 스토리지 및 연결된 내부 메커니즘에 대한 요구 사항을 완화할 수 있습니다.

그림 9: NXP의 LPC55S 프로세서 제품군은 디지털 지문을 KEK로 사용하여 키 저장소에서 보호되고 연결된 활성화 코드, 키 코드 및 인덱스를 사용하여 프로그래밍 방식으로 참조되는 키를 암호 해독합니다. (이미지 출처: NXP)

그림 9: NXP의 LPC55S 프로세서 제품군은 디지털 지문을 KEK로 사용하여 키 저장소에서 보호되고 연결된 활성화 코드, 키 코드 및 인덱스를 사용하여 프로그래밍 방식으로 참조되는 키를 암호 해독합니다. (이미지 출처: NXP)

개발자는 KEK를 사용하여 맞춤형 키 및 연결된 데이터를 암호 해독하고 암호화된 결과를 비보안 비휘발성 메모리에 저장할 수 있습니다. 이 방식을 사용하면 개발자가 보안 스토리지가 제한적인 장치에서도 다양한 유형의 키 및 연결된 데이터를 보호할 수 있습니다. PUF 생성 KEK의 출시로 개발자는 개발 주기 전반에서 응용 제품을 보호할 수 있는 보안 IoT 장치를 구현할 수 있습니다.

결론

전용 보안 IC 및 보안 프로세서와 암호화 가속기의 출시로 개발자의 보안 시스템 구축 역량이 크게 향상되었습니다. 하지만 보안 시스템은 암호화 메커니즘 및 프로토콜과 연관된 개인 키 및 기타 데이터의 보안에 크게 의존합니다. 보안 장치에서는 다양한 메커니즘을 채택하여 유휴, 전송 중 및 사용 중 상태인 보안 데이터를 보호합니다. 이러한 장치를 사용하여 개발자는 다른 설계 요구 사항을 훼손하지 않으면서 더 강력한 보안 IoT 솔루션을 빌드할 수 있습니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.