자체 심문 및 진단 기능을 적용하여 센서 데이터의 무결성 보장

DigiKey 북미 편집자 제공

2019-03-29

센서 및 IoT(사물 인터넷) 기술은 산업, 상업 및 소비자 가전 분야에서 그 존재감을 빠르게 확장하고 있습니다. 이러한 확장과 더불어 관련 센서와 프런트 엔드 인터페이스 회로망으로부터 수집되는 데이터의 무결성을 보장해야 할 필요성이 커지고 있습니다.

데이터 무결성의 잠재적 문제는 단일 인터페이스 IC가 여러 센서를 지원할 경우 더욱 심각해집니다. 단일 IC 문제로 인해 판독값 클러스터가 손상될 수 있기 때문입니다. 결과적으로 이는 감지된 상태에 대한 잘못된 평가로 이어져 부적절하거나 위험한 시스템 작업을 야기할 수 있습니다.

이 기사에서는 센서-프로세서 신호 체인에서 하드 및 소프트(과도) 결함과 센서 판독값 부정확성을 야기하는 다양한 소스를 살펴봅니다. 그런 다음 Analog Devices가 제공하는 고집적 IC를 소개하고 센서, 자체, 디지털 I/O에 대한 진단을 통해 이러한 문제를 극복하는 데 IC가 어떻게 사용될 수 있는지에 대해 설명합니다.

센서-프로세서 신호 경로

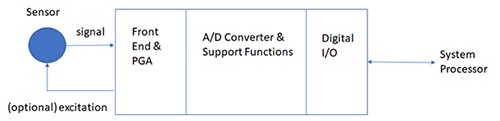

궁극적으로 모든 센서 판독값의 무결성에 영향을 미치는 요인은 그림 1에서 볼 수 있는 신호 체인의 3가지 주요 기능 블록에서 시작됩니다. 기능 블록은 다음과 같습니다.

- 센서 및 리드

- 신호 조절 IC의 아날로그 프런트 엔드. 아날로그 디지털 컨버터(ADC)의 중심임

- 시스템 프로세서에 대한 디지털 I/O

그림 1: 기본 센서-프로세서 신호 경로는 몇몇 기본 기능의 원칙으로 구성되지만 실용적이고 유용한 인터페이스 IC는 수많은 추가 기능과 특징을 제공합니다. (이미지 출처: DigiKey)

다채널 시스템에서 센서는 열전대, 저항 온도 감지기(RTD), 압력 센서 등 여러 유형이 혼합되어 사용되는 경우가 많습니다. 물론 센서는 고장나거나 상호 연결 리드가 열리거나 주변 리드, 전력 레일 또는 접지에 단락될 수 있습니다.

센서 유형에 따라 판독값이 범위를 벗어나면서 전선 리드의 결함이 즉각적으로 드러날 수 있습니다. 이와 대조적으로 몇몇 결함 모드는 부정확하지만 타당해 보이는 신호를 도출하기도 합니다. 또한 RTD 등의 일부 센서에는 외부 자극 전류가 필요하며 이 전류는 유효한 판독값을 위해 설정 범위 내여야 합니다. 이러한 이유로 인해 센서와 아날로그 프런트 엔드 사이의 신호 경로 연속성을 테스트하는 것이 좋으며 가능한 ADC 문제와 상관없는 아날로그 회로망을 이용해 신호가 허용된 최소와 최대 한도 사이에 머물러 있는지 확인하는 것이 좋습니다.

이는 정확한 판독값을 제공할 뿐만 아니라 소스 데이터에 대한 매우 높은 수준의 확신을 갖고 시스템 의사 결정 알고리즘을 실행할 수 있게 하는 판독값도 제공합니다.

하지만 이러한 모든 추가 확인과 균형은 추가 부품, 더 확장된 실장 면적, 추가 설계 시간을 야기합니다.

센서 데이터의 무결성을 보장하는 자체 심문 IC

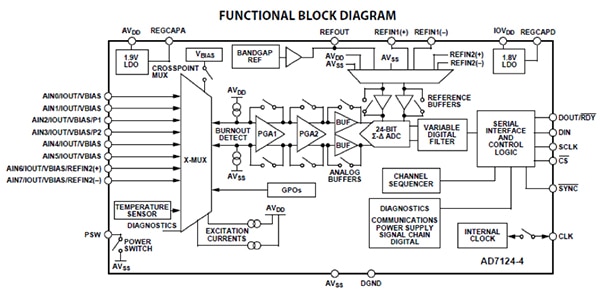

설계 시간과 실장 면적에 최소한의 영향만을 미치면서 높은 무결성 데이터에 대한 필요성을 충족하기 위해 Analog Devices는 기본 신호 조절 및 변환 이상의 성능을 가진 인터페이스이자 센서 중심의 ADC인 AD7124-8BCPZ-RL7을 도입했습니다. 이 인터페이스에는 여러 신호 및 자체 진단 기능이 포함되어 있어 데이터 무결성을 보장합니다.

그림 2: AD7124 센서 중심 ADC 및 인터페이스는 기본 신호 조절 및 변환 이상의 성능으로 여러 신호와 자체 진단 기능을 포함하므로 데이터 무결성을 보장할 수 있습니다. (이미지 출처: Analog Devices)

Ad7124는 4채널 저소음 저전력 24비트 시그마-델타(Σ-Δ) 장치입니다. 최저 샘플링 속도 범위는 수많은 센서 등급과 응용 분야에 적합한 수준인 1샘플/초를 약간 초과한 수준부터 19,200샘플/초까지 아우릅니다. 최저 샘플링 속도에서는 255μA를 소모합니다. 이 장치의 판독값의 정확도는 저소음, 25nV 미만의 rms, 내부 전압 레퍼런스의 낮은 드리프트(10ppm/°C)에 설계 중점을 맞추면서 향상되었습니다.

AD7124 자체는 32리드 LFCSP 및 24리드 TSSOP 패키지로 제공됩니다. 유연한 디지털 I/O는 3선 및 4선 SPI, QSPI, MICROWIRETM, DSP 호환 인터페이스를 지원합니다.

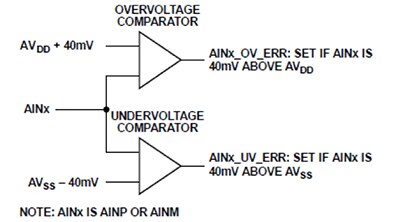

AD7124는 신호 제한 경보와 번아웃 전류 감지라는 두 기술을 이용해 앞에서 언급했던 센서 리드 문제를 해결합니다. 신호 제한 경보는 과전압/저전압 경보 모니터링을 이용해 4쌍의 아날로그 입력 연결의 각각에 대한 절대 전압을 확인합니다(그림 3). 규격서 사양을 충족하기 위해 이 전압은 정의된 범위 내여야 합니다.

그림 3: 신호 제한 경보를 이용한 센서 리드 기본 확인에는 최소/최대 설정이 고정된 하드웨어 기반 비교기가 사용됩니다. (이미지 출처: Analog Devices)

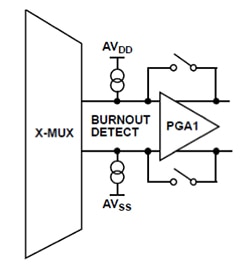

번아웃 전류 감지는 상호 보완적 프로그래밍 가능한 전류 싱크와 소스 한 쌍을 사용합니다. 사전 정의된 전류 쌍을 센서 리드로 소싱 및 싱킹함으로써 AD7124는 무결성을 확인할 수 있습니다(그림 4). 완전히 켜져 있거나 완전히 꺼져 있는 전류는 테스트 시 선택한 아날로그 입력 전선 쌍으로 전환됩니다.

그림 4: 사전 정의된 전류 쌍을 소싱하여 센서 리드로 싱킹함으로써 AD7124는 무결성을 확인할 수 있습니다. (이미지 출처: Analog Devices)

전체 범위 판독값은(또는 거의 전체 범위) 프런트 엔드 센서가 개방 회로임을 의미할 수 있습니다. 측정된 전압이 0V인 경우 이는 트랜스듀서가 단락되었음을 나타내는 것일 수 있습니다. 해당하는 플래그 비트는 오류 레지스터에서 설정되어 오류 발생 및 유형을 나타냅니다.

마지막으로 RTD 또는 스트레인 게이지에서 흔히 그렇듯이, 사용자가 내부 참조를 사용하는 대신 외부적으로 참조를 제공하는 응용 제품의 경우, AD7124가 모든 외부 변환 레퍼런스 전압이 올바른지 확인합니다.

프런트 엔드 및 ADC 확인

외부 센서와 그 리드가 장애의 근원일 가능성이 가장 높긴 하지만 프런트 엔드/변환 IC 자체의 성능을 확인하는 것도 매우 중요합니다. 사양을 벗어나거나 완전히 오작동하는 기능에는 다음이 포함될 수 있습니다.

- 내부 ADC 전압 레퍼런스

- 입력 신호를 증폭해 최고 분해능에 대한 ADC 범위를 일치시키는 프로그래밍 가능한 이득 증폭기(PGA)

- 필요한 센서 여기를 제공하는 저드롭아웃 조정기(LDO)

- IC의 내부 전력 레일

- ADC 자체

신호 체인의 아날로그 섹션을 테스트하기 위해 AD7124는 하드웨어 및 펌웨어 기반 자가 테스트를 호출합니다. 이는 4개의 차등 입력 채널 중 하나에 내부적으로 연결되어 디지털화될 수 있는 20mV 신호를 생성합니다. 여기에서 여러 목적이 있습니다. 이는 입력 채널 멀티플렉서 및 ADC의 기본 작동을 확인하며 PGA 이득 설정을 변경하고 결과 ADC 판독값을 확인해 PGA 평가를 활성화하기도 합니다.

또한 ADC 자체도 문제의 원인일 수 있습니다. Ad7124는 1비트 변조 및 필요한 디지털 필터가 포함된, 잘 확립된 Σ-Δ 컨버터 아키텍처를 사용합니다. ADC 성능에 대한 전체 테스트는 아날로그 및 디지털 기술을 모두 사용합니다.

AD7124에서 변조기 출력에 20개의 연속된 1이나 0이 포함된 경우 이는 변조기가 하나의 레일이나 다른 레일에 대해 포화되었으며 오류 플래그 비트가 설정되었음을 나타냅니다. 이와 유사하게 IC는 스스로 시작한 오프셋 보정 후 ADC 오프셋 계수가 0x7FFFF ~ 0xF80000 사이인지 확인합니다. 이 범위를 벗어난다면 또 다른 오류 플래그 비트가 설정됩니다. 마지막으로 전체 범위 보정 중에 디지털 필터 넘침이 발생하면 또 다른 오류 플래그 비트가 설정됩니다.

내부 및 외부 전원과 레일도 잠재적인 문제의 원인입니다. 여러 센서에는 소량의 여기 전력이 필요하며 이는 아날로그 프런트 엔드 IC 내의 저소음 소형 LDO에 의해 공급되는 경우가 많습니다.

AD7124는 두 가지 방식으로 LOD 출력을 확인합니다. 첫째로, LDO 출력은 내부적으로 ADC에 라우팅되어 그 예상치와 비교될 수 있습니다. 둘째로, ADC로부터 독립된 하드웨어 비교기가 LDO와 IC의 레퍼런스 비교를 지속적으로 모니터링합니다. 사전 설정된 임계치 내에 해당하는 경우 오류 플래그 비트가 설정됩니다. 그 결과, LDO는 초기화 중에 평가될 수 있고 또한 이는 프로세서 리소스를 지속적으로 소비하지 않으면서 지속적으로 진행될 수 있습니다.

확신을 더하기 위해, 공급 모니터링에 사용되는 테스트 회로망은 그 입력을 접지(공칭 0V)에 연결한 다음 디지털 판독값을 확인함으로써 (어느 정도까지는) 확인할 수 있습니다. AD7124는 요구되는 0.1F의 감결합 커패시터가 존재하며 연결되어 있는지 확인함으로써 이 데이터 무결성 보장을 한층 더 강화합니다. AD7124에 내부 스위치를 통해 감결합 커패시터를 물리적으로 분리하도록 지시한 다음 LDO 출력을 확인하는 방식으로 이를 수행합니다. LDO 전압이 떨어지는 경우 감결합 커패시터는 전기적으로 부재합니다. 이 역시 오류 플래그 비트를 설정합니다.

물론 모든 IC에는 최대 온도 등급이 있으며 이를 벗어날 경우 사양을 벗어나거나 완전한 오작동을 유발할 수 있습니다. 따라서 AD7124에는 센서가 내장되어 있어 언제든지 통상 ±0.5°의 정확도로 다이 온도 판독값을 제공합니다.

디지털 오류

지금까지 우리는 아날로그 센서 또는 변환 기능과 관련해 성능과 정확도를 보장하는 것에 대해 살펴보았습니다. 하지만 이러한 수많은 센서가 배포되는 전기적으로 혹독한 산업 환경에는 디지털 전자 기기에 영향을 미치는 잡음, EMI/RFI, 과도가 있습니다. 따라서 내부 디지털 회로망의 성능은 물론, 시스템 프로세서에 대한 인터페이스 링크의 성능을 보장하여 데이터와 모든 읽기/쓰기 작업의 견고성을 보장해야 합니다.

AD7124는 다음 작업과 기능으로 시작되는 다면적인 접근 방식을 통해 이를 달성합니다.

- 마스터 클록의 성능이 확인됩니다. 마스터 클록은 출력 데이터 전송률, 필터 정착 시간, 필터 노치 주파수 설정에 필요합니다. 이는 언제든지 판독할 수 있는 별도의 계수 레지스터로 확인됩니다.

- 각 SPI 읽기 또는 쓰기 작업에 사용되는 SCLK 펄스의 수는 특별한 클록 카운터를 통해 확인됩니다. 이 개수는 8의 배수여야 합니다(모든 SPI 작업은 8/16/32/40/48클록 펄스를 사용함).

- AD7124는 읽기 및 쓰기 작업이 유효한 레지스터 주소만 처리하는지 확인합니다.

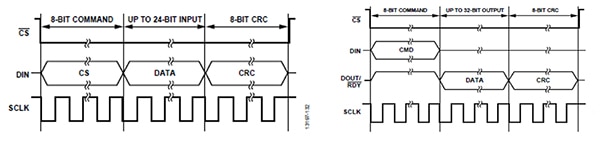

이러한 단계는 내부 작업을 처리하지만 프로세서 인터페이스 및 그 데이터에 대한 무결성을 보장하지는 않습니다. 데이터에 극히 높은 수준의 확신을 제공하기 위해 사용자는 AD7124에 주기적인 중복성 확인(CRC) 다항 체크섬 알고리즘 구현을 지시할 수 있습니다. 체크섬은 레지스터에 유효한 데이터만 기록되도록 보장하며 검증될 레지스터에서 데이터를 읽는 것을 허용합니다(그림 5). 체크섬은 단일 비트 오류도 감지할 수 있는 확실한 기술이지만 이러한 오류를 수정할 수는 없다는 점에 유의하십시오.

그림 5: 다항 기반 CRC 체크섬이 단일 비트 오류 감지를 위해 (왼쪽) SPI 쓰기 및 (오른쪽) SPI 읽기 트랜잭션에 추가됩니다. (이미지 출처: Analog Devices)

활성화되면 이 작업은 데이터 블록에 대한 체크섬을 계산하고 이를 각 읽기 및 쓰기 트랜잭션의 끝에 덧붙입니다. 레지스터 쓰기의 성공을 보장하기 위해 레지스터를 다시 판독하여 데이터에서 계산된 값에 대해 저장된 체크섬을 확인해야 합니다.

전기적으로 혹독한 환경에서는 메모리에도 비트 오류가 발생할 수 있습니다. 온칩 레지스터에서 이러한 오류에 대해 높은 수준의 확인을 수행하기 위해 AD7124는 매번 폭넓은 범위의 작업에 대한 체크섬을 계산합니다.

- 레지스터 쓰기 주기가 있습니다.

- 오프셋/전체 범위 보정이 있습니다.

- 장치가 단일 변환 주기를 수행하며, 변환 완료 후 ADC가 대기 모드로 전환됩니다.

- 그러면 연속 쓰기 모드가 종료됩니다.

향상된 견고성을 위해 내부 읽기 전용 메모리(ROM)도 평가됩니다. 전원을 켜면 모든 레지스터가 ROM에 저장된 기본값으로 초기화됩니다. 전원을 켜면 ROM 내용에 대한 CRC 계산이 수행됩니다. 이러한 계산의 결과가 저장된 CRC 결과와 다른 경우 이는 최소 하나의 단일 비트 오류가 있음을 나타냅니다.

AD7124도 다양한 유형의 센서를 위한 여기를 제공하며 증폭기 및 PGA를 통해 센서 출력 신호의 신호 조정 및 비율 조정도 제공합니다. 이 제품은 가능한 한 최대의 견고성을 제공하기 위해 초기화, 원하는 기능 모드 및 파라미터 설정, 다양한 오류 및 결함을 줄이기 위한 여러 내부 레지스터를 포함합니다.

AD7124 평가 기판을 사용해 AD7124 설계 시작

AD7124는 수많은 설계 가능성과 성능 기능을 포함하는 복잡한 시스템입니다. 단순한 “드롭인 앤 고” 센서 인터페이스 IC가 아닙니다. 학습을 용이하게 하고 설계자가 잠재적 기능에 빠르게 익숙해지도록 하기 위해, Analog Devices도 EVAL-CN0376-SDPZ 평가 기판을 제공하고 있습니다(그림 6).

그림 6: EVAL-CN0376-SDPZ 평가 기판은 설계 속도를 높이고 AD7124의 수많은 기능과 특징을 완전히 발휘할 수 있도록 지원합니다. (이미지 출처: Analog Devices)

평가 기판에는 AD7124를 다양한 실제 센서 및 프로세서와 연결하는 데 필요한 전원 공급 장치와 외부 부품이 포함되어 있습니다. 이는 평가 기판의 데이터를 구성 및 캡처하기 위해 USB 포트를 통해 통신하는 Windows PC 기반 CN-0376 평가 소프트웨어에 의해 지원됩니다.

결론

수많은 중대한 결정이 시스템 프로세서에 내장된 고급 알고리즘에 의해 내려지고 있으며, 대부분의 경우 이는 인공 지능(AI)에 의해 개선됩니다. 이러한 알고리즘이 작동하고 결론을 도출하고 조치를 취하는 기반이 되는 원시 데이터의 높은 무결성이 그 어느 때보다도 필수적으로 요구됩니다. AD7124와 같은 IC는 리드 및 센서 인터페이스에서 자체 성능 및 기능에 이르는 신호 체인의 모든 링크를 확인하는 데이터가 예상대로 작동하며 손상되지 않았다는 확신을 더해줍니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.