Xilinx ZCU102 평가 키트에서 NVMe SSD 인터페이스 활성화

DigiKey 북미 편집자 제공

2020-05-12

개요

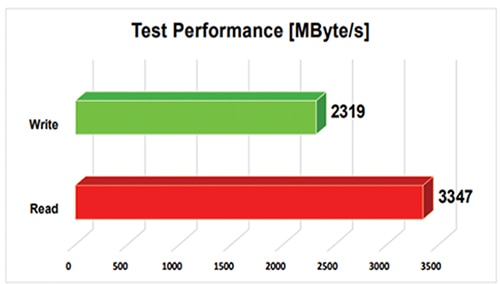

Xilinx® UltraScale™ MPSoC 아키텍처를 기반으로 하는 Zynq® UltraScale+™ MPSoC 제품군은 다양한 기능을 갖춘 64비트 쿼드 코어 또는 이중 코어 ARM 기반 처리 시스템(PS) 및 Xilinx 프로그래밍 가능 논리(PL) UltraScale 아키텍처를 단일 장치에서 통합합니다. 또한 온칩 메모리, 다중 포트 외부 메모리 인터페이스, 풍부한 주변 장치 연결 인터페이스, 특히 NVMe SSD 드라이브와 같은 PCI Express® Gen3 스토리지 장치를 지원하는 GTH 16.3Gbps 트랜시버도 갖추고 있습니다. 이 기사에서는 매우 빠른 속도(쓰기 2,319MB/s 및 읽기 3,347MB/s)를 실현할 수 있는 Design Gateway의 NVMeG3-IP Core를 사용하여 Xilinx의 ZCU102 평가 키트에서 NVMe SSD(Solid State Drive) 인터페이스를 구현하는 솔루션을 보여줍니다.

Zynq® UltraScale+ MPSoC ZCU102 평가 키트 소개

ZCU102는 XCZU9EG-2FFVB1156E MPSoC 장치를 기반으로 하는 빠른 시제품 제작을 위한 범용 평가 기판입니다. 이 기판에는 사용자 맞춤형 설계에 적합한 고속 DDR4 SODIMM 및 부품 메모리 인터페이스, FMC 확장 포트, 다중 Gbps 직렬 트랜시버, 다양한 주변 장치 인터페이스 및 FPGA 논리가 포함되어 있으며, 모든 구성품에서 유연한 시제품 제작 플랫폼을 제공합니다.

그림 1: ZCU102 평가 키트 (이미지 출처: Xilinx Inc.)

그림 1: ZCU102 평가 키트 (이미지 출처: Xilinx Inc.)

ZCU102는 5G 무선, 차세대 고급 운전자 지원 시스템(ADAS), 산업용 사물 인터넷(IIoT) 솔루션과 같은 최신 응용 제품을 제작하는 데 유용한 프로그래밍 가능 논리 기능을 제공합니다.

NVMe SSD 드라이브와 같은 우수한 성능과 높은 안전성을 갖춘 외부 데이터 스토리지가 필요한 응용 제품의 경우 PCI Express® Gen3용 GTH 트랜시버 규정을 준수하는 인터페이스를 활용하는 적합한 솔루션이 필요합니다.

NVMe SSD 스토리지 소개

NVM Express(NVMe)는 호스트 컨트롤러에서 PCI Express를 통해 SSD로 액세스하는 데 사용되는 인터페이스를 정의합니다. NVM Express는 레지스터를 두 개(명령 실행 및 명령 완료)만 사용하여 명령 실행 프로세스와 완료 프로세스를 최적화합니다. 또한 NVMe는 단일 대기열 내에서 최대 64K 명령을 지원하여 병렬 작업을 지원합니다. 64K 명령은 순차 액세스와 임의 액세스 모두에 대해 전송 성능을 개선합니다.

NVMe 드라이브는 초고속 데이터 스토리지 및 컴퓨팅을 위한 길을 열었습니다. 최신 NVMe SSD 드라이브는 PCIe Express® Gen3 기술을 사용하여 40Gb/s 속도의 우수한 최고 성능을 실현할 수 있습니다.

ZCU102에서 NVMe 호스트 컨트롤러 구현

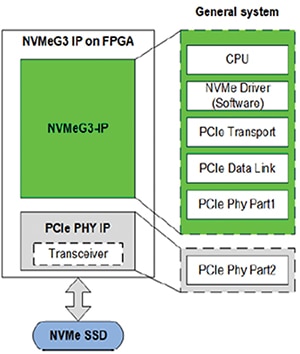

그림 2: NVMe 구현 (이미지 출처: Design Gateway)

그림 2: NVMe 구현 (이미지 출처: Design Gateway)

일반적으로 NVMe 호스트는 PCIe 컨트롤러를 통해 작동되는 호스트 프로세서를 사용하여 구현되며 NVMe SSD에서 데이터를 송/수신하는 데 사용됩니다. NVMe 프로토콜은 장치 드라이버에서 초고속 버스를 통해 연결되는 PCIe 컨트롤러 하드웨어 CPU 주변 장치와 통신하기 위해 구현됩니다. 외부 DDR 메모리는 데이터 버퍼링 및 명령 대기줄에서 PCIe 컨트롤러와 SSD 간에 데이터를 전송하는 데 필요합니다.

PCIe Gen3 통합 블록은 ZCU102의 XCZU9EG-2FFVB1156E FPGA 장치에서 제공되지 않으므로 기존 구현 방법을 사용할 수 없습니다.

Design Gateway는 그림 2에 표시된 대로 NVMeG3-IP Core를 사용하여 PCIe 통합 블록이 제공되지 않는 Zynq® UltraScale+™ MPSoC 장치에 대해 NVMe SSD 인터페이스를 활성화하는 방식으로 솔루션을 제안합니다. ZCU102용 NVMe 인터페이스를 사용하면 우수한 성능을 갖추면서 최소한의 FPGA 리소스를 소비하는 다중 채널 RAID 시스템을 빌드할 수 있습니다. NVMeG3-IP Core 라이선스에는 설계자가 개발 시간을 단축하고 비용을 절감하는 데 도움이 되는 참조 설계의 예가 포함되어 있습니다.

Design Gateway의 NVMeG3-IP 개요

PCIe Gen3 Soft IP(NVMeG3-IP)를 포함하는 NVMe IP Core는 PCIe 통합 블록, CPU 및 외부 메모리 없이 NVMe SSD에 액세스하는 데 적합합니다. NVMeG3-IP에는 PCIe Gen3 Soft IP 및 256Kb 메모리가 포함되어 있습니다. 이 솔루션은 PCIe 통합 블록을 포함하지 않는 저비용 FPGA를 사용하여 초고속 성능을 갖춘 NVMe SSD 스토리지가 필요한 응용 제품에 권장됩니다.

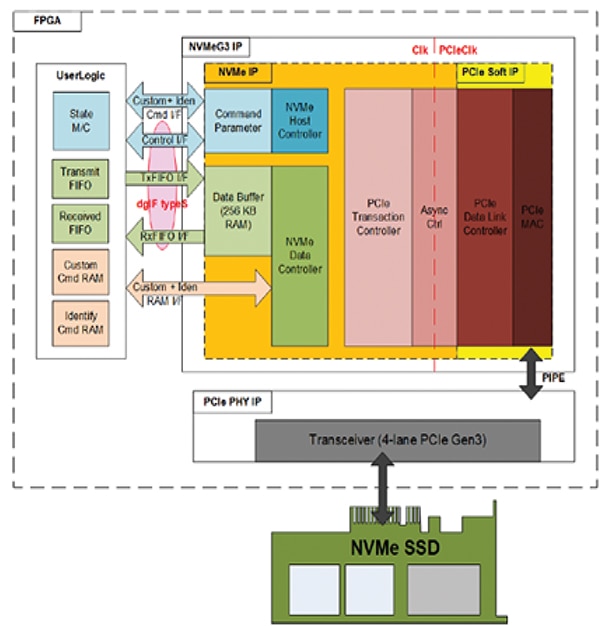

그림 3: NVMeG3-IP 제품 구성도 (이미지 출처: Design Gateway)

그림 3: NVMeG3-IP 제품 구성도 (이미지 출처: Design Gateway)

NVMeG3-IP의 특징

NVMeG3-IP는 아래 강조된 기능을 비롯한 다양한 특징이 있습니다.

- 응용 제품 계층, 트랜잭션 계층, 데이터 링크 계층 및 물리적 계층의 일부를 구현하여 CPU를 사용하지 않고 NVMe SSD 액세스

- 4레인 PCIe Gen3로 구성된 Xilinx PCIe PHY IP로 작동(128비트 버스 인터페이스)

- 256KB RAM 데이터 버퍼 포함

- dgIF typeS를 통한 간단한 사용자 인터페이스

- 6개 명령(Identify, Shutdown, Write, Read, SMART, Flush) 지원(선택적으로 조건부 명령 지원)

- 지원되는 NVMe 장치:

- 기본 클래스 코드: 01h(대용량 스토리지), 하위 클래스 코드: 08h(비휘발성), 프로그래밍 인터페이스: 02h(NVMHCI)

- MPSMIN(Memory Page Size Minimum): 0(4KB)

- MDTS(Maximum Data Transfer Size): 최소 5(128KB) 또는 0(제한 없음)

- LBA 단위: 512바이트 또는 4096바이트

- 사용자 클록 주파수는 PCIe 클록(Gen3의 경우 250MHz)보다 크거나 같아야 함

- 사용 가능한 참조 설계:

- AB17-M2FMC 어댑터 기판이 포함된 ZCU102

- AB18-PCIeX16/AB16-PCIeXOVR 어댑터 기판이 포함된 KCU105

- AB18-PCIeX16 어댑터 기판이 포함된 VCU118

Design Gateway는 NVMe SSD에 액세스하기 위한 NVMe 호스트 컨트롤러로 실행할 NVMeG3-IP를 개발했습니다. 사용자 인터페이스와 표준 기능은 NVMe 프로토콜에 대한 지식이 없어도 쉽게 사용할 수 있도록 설계되었습니다. NVMeG3-IP의 추가 기능에는 데이터 링크 계층과 순수 논리를 통해 PCIe 프로토콜의 일부 물리적 계층을 구현하는 내장형 PCIe soft IP가 있습니다. 따라서 NVMeG3-IP는 내장형 PCIe Soft IP 및 Xilinx PCIe PHY IP Core를 사용하여 PCIe 통합 블록이 없는 FPGA에서 실행될 수 있습니다. Xilinx PCIe PHY IP는 트랜시버와 논리 이퀄라이저를 포함하는 무료 IP Core입니다.

NVMeG3-IP는 여섯 가지 NVMe 명령(Identify, Shutdown, Write, Read, SMART, Flush)을 지원합니다. 256KB BlockRAM은 NVMeG3-IP에 통합되어 데이터 버퍼 역할을 합니다. 시스템에 CPU와 외부 메모리가 필요하지 않습니다. NVMeG3-IP에 대한 자세한 내용은 규격서를 참조하십시오. 웹 사이트에서 다운로드할 수 있습니다.

XCZU9EG-2FFVB1156E FPGA 장치의 FPGA 리소스 사용은 아래 표 1에 나와 있습니다.

|

표 1: Ultrascale/Ultrascale+ 장치에 대한 구현 통계 예

ZCU102의 구현 및 성능 결과

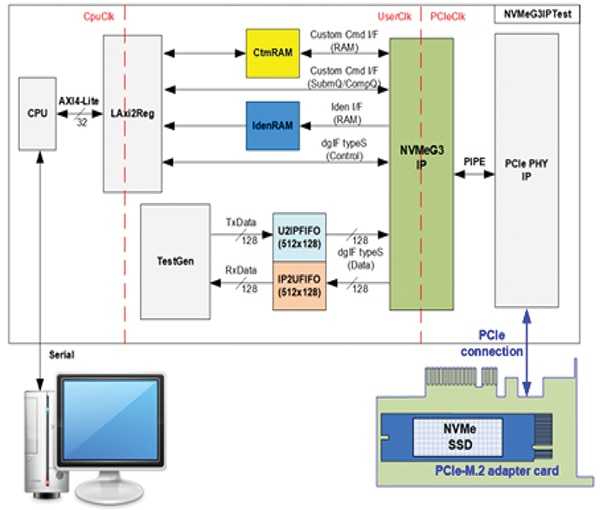

표 4는 NVMeG3-IP 작동을 보여주는 ZCU102 기반 참조 설계의 개요를 제공합니다. 데모 시스템의 NVMeG3IPTest 모듈은 TestGen, LAxi2Reg, CtmRAM, IdenRAM, FIFO 모듈에 포함되어 있습니다.

NVMeG3-IP 참조 설계에 대한 자세한 내용은 Design Gateway의 웹 사이트에 제공된 NVMeG3-IP 참조 설계 문서를 참조하십시오.

그림 4: NVMeG3-IP 참조 설계 개요 (이미지 출처: Design Gateway)

그림 4: NVMeG3-IP 참조 설계 개요 (이미지 출처: Design Gateway)

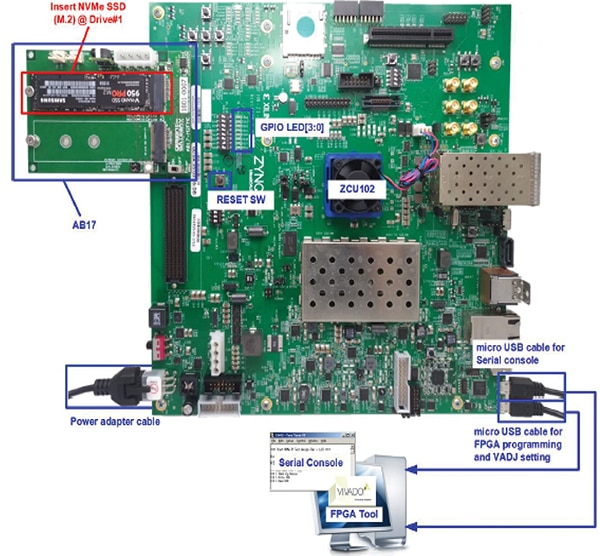

데모 시스템은 ZCU102에서 NVMe SSD를 사용하여 데이터를 읽고 쓰도록 설계되었습니다. 사용자는 직렬 콘솔을 통해 테스트 작업을 제어합니다. NVMe SSD에서 ZCU102와 연결하려면 그림 5에 표시된 AB17-M2FMC 어댑터 기판이 필요합니다.

그림 5: ZCU102에 설정된 NVMeG3-IP 데모 환경 (이미지 출처: Design Gateway)

그림 5: ZCU102에 설정된 NVMeG3-IP 데모 환경 (이미지 출처: Design Gateway)

512GB Samsung 970 Pro를 사용하는 중에 ZCU102에서 데모 시스템을 실행할 때의 예제 테스트 결과가 그림 6에 나와 있습니다.

그림 6: Samsung 970 PRO S를 사용 시 ZCU102의 NVMe SSD 읽기/쓰기 성능(이미지 출처: Design Gateway)

그림 6: Samsung 970 PRO S를 사용 시 ZCU102의 NVMe SSD 읽기/쓰기 성능(이미지 출처: Design Gateway)

결론

NVMeG3-IP Core는 ZCU102 평가 키트에서 NVMe SSD 인터페이스를 활성화하기 위한 솔루션과 PCIe 통합 블록이 제공되지 않는 Xilinx® Zynq® UltraScale+™ MPSoC 장치 제품군을 위한 솔루션을 제공합니다. NVMeG3-IP는 CPU 없이 NVMe SSD에 액세스하기 위해 최소한의 FPGA 리소스로 최고의 성능을 실현한다는 목표로 고안되었습니다. 이 제품은 CPU 발명이 없는 고성능 NVMe 스토리지에 적합하며 FPGA 장치에서 사용 가능한 PCIe 통합 블록 수에 제한 없이 GTH 트랜시버를 활용하여 여러 NVMe SSD 인터페이스를 구현할 수 있습니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.