ADC, 단순한 난수 발생기?

2025-10-22

ADC의 성능은 어떤가요? 이 질문은 ADC의 분해능을 묻는 것이 아닙니다. 놀랍게도 16비트 ADC가 항상 16비트의 유효 정보를 제공하는 것은 아닙니다! Mike Stone은 자신이 기고한 “Choosing an ADC”에서 "많은 16비트 ADC가 실제로는 7비트 ADC와 9비트 난수 생성기로 작동하고 있습니다."라고 말합니다. 이 기사에서는 ADC가 유용한 값보다 무작위 값을 더 많이 생성하는지 여부를 확인하는 방법과 함께, 무작위성을 줄이는 몇 가지 간단한 방법을 설명합니다.

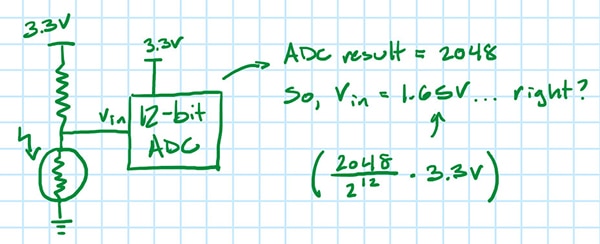

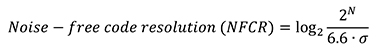

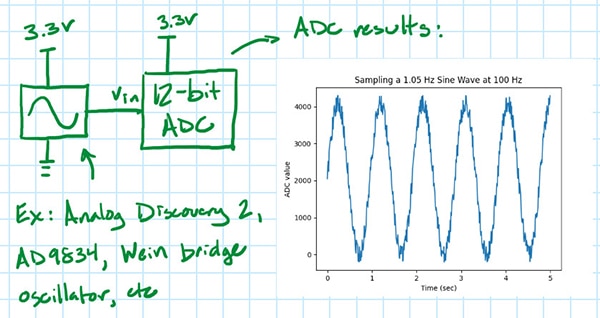

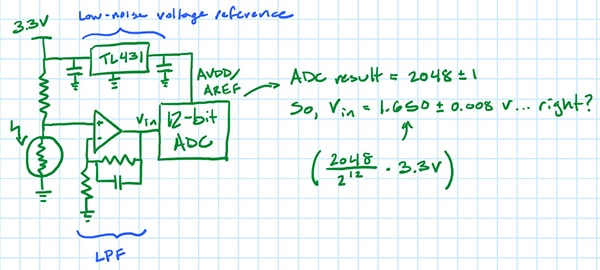

간단한 설정 즉, 광저항기의 전압을 측정하는 ADC를 고려해 보겠습니다. 그림 1의 12비트 ADC(VFS = 3.3V)가 값 2048을 보고한다면, 광저항기의 전압이 1.65V라는 의미일까요?

그림 1: 광저항기 전압을 측정하기 위한 간소화된 ADC 설정(이미지 출처: Nathan Jones)

그림 1: 광저항기 전압을 측정하기 위한 간소화된 ADC 설정(이미지 출처: Nathan Jones)

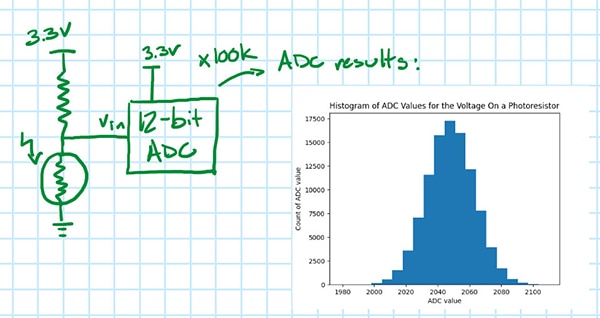

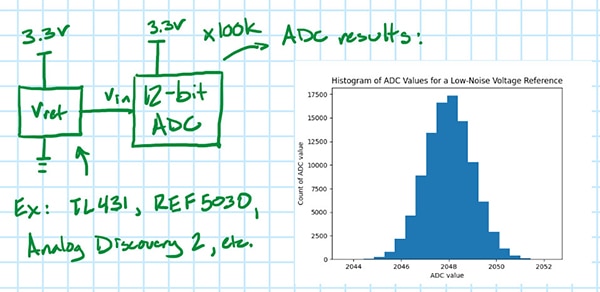

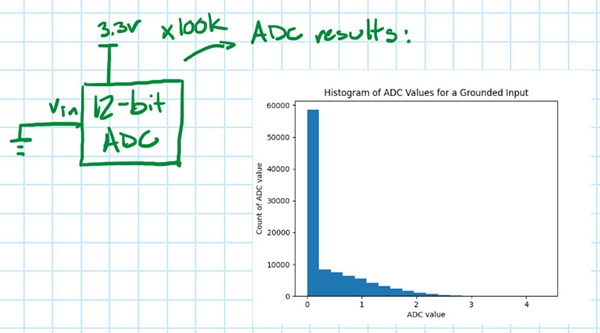

아니요, 그렇지 않습니다! 시연을 위해, 두 번째 샘플 다음에 세 번째 샘플을 가져오는 식으로 실제로 100,000개 샘플을 가져온 후 결과를 플로팅해보겠습니다. 그림 2처럼 ADC 값 분포가 표시됩니다. 설정에서 아무 것도 변경되지 않으면 이 중 하나가 광저항기의 실제 전압일 수 있으며, 이러한 모든 샘플의 평균값이 실제 전압일 가능성이 가장 높습니다.

그림 2: 광저항기 전압의 100,000개 샘플에 대한 ADC 값의 히스토그램이 표시되어 있습니다(이미지 출처: Nathan Jones).

그림 2: 광저항기 전압의 100,000개 샘플에 대한 ADC 값의 히스토그램이 표시되어 있습니다(이미지 출처: Nathan Jones).

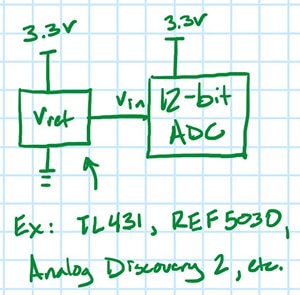

여기서 또 다른 질문이 생깁니다. 이 변화 중 일부는 입력 신호의 실제 변화일 수 있을까요? 예, 그렇습니다. 이를 테스트하기 위해, 저항 분배기를 알려진 잡음 레벨을 가진 전압 레퍼런스(그림 3)로 교체하고 실험을 반복합니다.

그림 3: 전압 레퍼런스를 사용한 새 테스트 설정으로 저항 분배기를 대신합니다(이미지 출처: Nathan Jones).

그림 3: 전압 레퍼런스를 사용한 새 테스트 설정으로 저항 분배기를 대신합니다(이미지 출처: Nathan Jones).

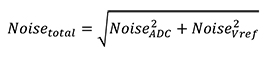

이상적으로, 사용된 전압 레퍼런스는 ADC에서 필요한 잡음 레벨의 1/3 미만인 잡음 레벨을 가져야 합니다(예를 들어, ADC에서 ±1LSB의 잡음이 예상되는 경우[위 예시의 ADC를 사용할 경우 ±0.8mV에 해당할 수 있음], 이상적으로는 전압 레퍼런스의 잡음 레벨이 0.27mVpp 미만이어야 함). 그럴 경우, 상관관계가 없는 잡음은 구적법으로 더해진다는 사실(방정식 1)에 따라, 측정된 잡음은 모두 ADC에서 발생한 것으로 예상됩니다.

[1]

[1]

NoiseVref=NoiseADC/3인 경우 Noisetotal=1.054 × NoiseADC. 이는 전압 레퍼런스가 총 잡음의 단 5.4%만 차지한다는 것을 의미하며, 사실상 무시할 수 있는 양입니다. 전압 레퍼런스의 잡음이 ADC 잡음의 1/3보다 큰것으로 드러나면, 측정된 표준 편차에서 기여도를 빼면 됩니다(방정식 2 참조).

[2]

[2]

전압원의 잡음 레벨을 확인하는 방법

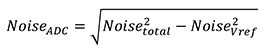

가장 쉬운 방법은 규격서에서 찾는 것입니다. 다음은 Texas Instruments REF5030에 대한 규격서의 예로 9μVpp의 잡음 레벨이 표시되어 있습니다.

그림 4: REF5030 규격서에서 발췌한 내용으로, 출력 전압 잡음 사양이 표시되어 있습니다(이미지 출처: Texas Instruments).

그림 4: REF5030 규격서에서 발췌한 내용으로, 출력 전압 잡음 사양이 표시되어 있습니다(이미지 출처: Texas Instruments).

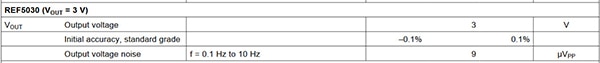

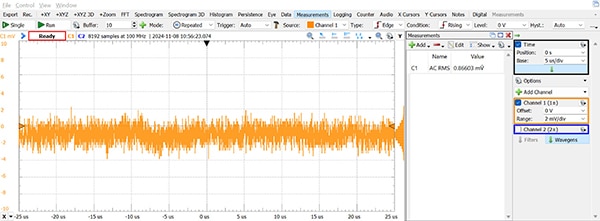

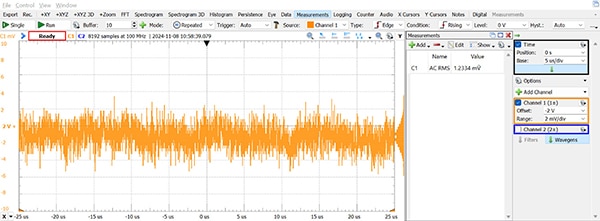

규격서에 잡음 레벨이 표시되어 있지 않은 경우(또는 단지 해당 값을 확인하려는 경우), 오실로스코프를 사용하여 측정할 수 있습니다(먼저 오필로스코프의 잡음 플로어를 확인해야 함). 이는 오실로스코프 입력 중 하나를 접지에 연결하고 표시된 신호 변동의 RMS 값을 측정하여 수행할 수 있습니다. 그림 5는 Analog Discovery 2(AD2)를 사용하여 이를 수행한 결과를 나타내며, RMS 잡음이 0.9mV임을 보여줍니다. 흥미롭게도 이 값은 시간축이 8µs/div를 초가하여 증가할 경우 감소합니다(µV 범위까지 감소). AD2가 유효 분해능을 증가시키기 위해 오버샘플링 및 데시메이션을 사용하기 때문인 것으로 추정됩니다.

그림 5: Analog Discovery 2 오슬로스코프의 잡음 플로어 레벨 플롯(이미지 출처: Nathan Jones)

그림 5: Analog Discovery 2 오슬로스코프의 잡음 플로어 레벨 플롯(이미지 출처: Nathan Jones)

전압원 측정 시, 오실로스코프 신호의 변동은 전압원과 오실로스코프의 잡음이 결합된 결과입니다. 이러한 잡음원이 서로 상관이 없다면 위와 같이 Noisemeasured=√(Noise²Scope+Noise²Vref), NoiseVref=√(Noise²Measured-Noise²Scope)입니다. AD2에서 생성된 2VDC 신호 측정 시, 해당 잡음은 1.2mV로 확인되었습니다(그림 6).

그림 6: 이 2VDC 신호 플롯은 오실로스코프 잡음이 1.2mV임을 나타냅니다(이미지 출처: Nathan Jones).

그림 6: 이 2VDC 신호 플롯은 오실로스코프 잡음이 1.2mV임을 나타냅니다(이미지 출처: Nathan Jones).

이는 AD2의 신호 생성기에도 약 0.9mV의 잡음 레벨이 있음을 나타냅니다. 이는 10비트 ADC를 테스트하기에는 충분히 낮은 수준입니다(3.3V 풀스케일 판독을 사용하는 10비트 ADC에서 0.9mV는 LSB의 1/3에 불과함). 그러나 그보다 분해능이 높은 ADC의 경우, 측정 시 이 잡음을 고려해야 합니다.

그림 7: 전압 레퍼런스를 사용하는, 광저항기 전압의 100,000개 샘플에 대한 ADC 값의 히스토그램이 표시되어 있습니다(이미지 출처: Nathan Jones).

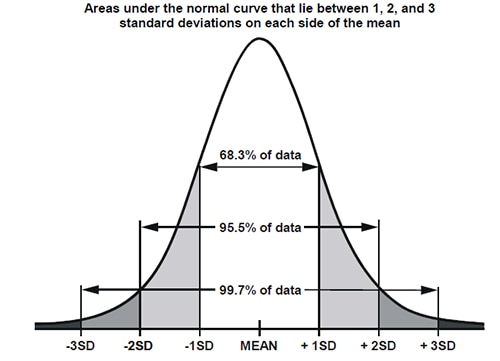

결과가 훨씬 좋아졌습니다! 이제 두 번째 히스토그램(그림 7)의 x축이 최대 2052까지만 나오는 반면(해당 그래프 그림 8의 분포는 표준 편차가 1LSB임), 첫 번째 그래프는 2100까지 이어져 있음을 볼 수 있습니다(표준 편차 15LSB). 이는 ADC에 대한 DC 히스토그램 테스트라고 하며, 표준 편차는 ADC에 포함된 잡음의 양을 효과적으로 나타냅니다. ADC에서 값을 측정할 때마다, 아날로그 핀의 실제 값이 실제로 해당 값의 ±1 표준 편차 내에 있을 확률은 68%에 불과하지만 실제 값이 해당 값의 ±3 표준 편차 내에 있을 확률은 99.7%에 달합니다.

그림 8: 표준 편차 분포 곡선(이미지 출처: https://i.sstatic.net/jkMDV.png)

그림 8: 표준 편차 분포 곡선(이미지 출처: https://i.sstatic.net/jkMDV.png)

LSB의 이 표준 편차를 볼트로 변환하면 ADC의 입력 참조 잡음이 됩니다(방정식 3).

![Input - referred noise [V_RMS ]=(σ∙V_FS)/2^N 방정식 3](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2025/October/Can%20an%20ADC%20Be%20Just%20a%20Random%20Number%20Generator/article-2025october-can-an-adc-be-just-equation3.jpg?la=en&ts=6126a5a1-ecae-4e79-bfb0-97e98cce83fa) [3]

[3]

ADC의 잡음이 너무 적어 모든 ADC 코드가 단일 빈에 속하는 경우 ADC 레퍼런스 전압을 낮춰 보십시오. 잡음 레벨은 동일하게 유지되지만 이전보다 많은 ADC 코드를 차지하므로, 입력 참조 잡음에 대한 적절한 값을 찾을 수 있습니다.

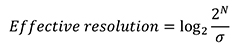

ADC의 유효 분해능과 NFCR(무잡음 코드 분해능)은 이 잡음이 ADC 분해능을 제한하는 정도를 나타내며 ADC 코드의 전체 범위를 표준 편차 1(방정식 4) 또는 표준 편차 6.6(방정식 5)의 너비만 갖는 빈으로 나누어 계산합니다.

[4]

[4]

[5]

[5]

본질적으로, 결과에서 실제로 유효한 비트 수가 더 적어지는데, ADC 코드의 마지막 몇 비트가 잘못되었거나 잡음일 가능성이 점점 커지기 때문입니다.

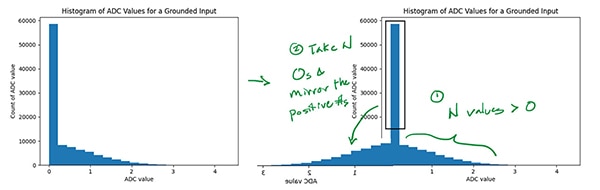

DC 히스토그램 테스트를 좀 더 간단하게 수행하려면 오실로스코프에서와 같이 ADC의 입력을 접지한 후 ADC의 히스토그램을 생성하면 됩니다(그림 9).

그림 9: 입력이 접지된 상태의 ADC 출력 전압 샘플 히스토그램이 표시되어 있습니다(이미지 출처: Nathan Jones).

그림 9: 입력이 접지된 상태의 ADC 출력 전압 샘플 히스토그램이 표시되어 있습니다(이미지 출처: Nathan Jones).

이 히스토그램의 표준 편차는 ADC 잡음 측정값이도 하지만(판독값 0V에 영향을 주지 않는 ADC 레퍼런스 전압의 잡음 기여도를 뺀 값) 낙관적으로 보면 낮은 수치입니다. ADC는 0V보다 낮은 값을 단지 0으로 보고하므로 실제 잡음 분포의 1/2만 볼 수 있습니다. 이 경우, 분포가 평균값을 중심으로 대칭이라고 가정하고, 분포가 대칭이 되도록 중앙값을 음수로 충분히 바꾼 뒤 해당 분포의 표준 편차를 계산함으로써 ADC 잡음을 근사할 수 있습니다(그림 10).

그림 10: 그림 9 히스토그램의 미러링을 통해 ADC 잡음의 근사치를 구합니다(이미지 출처: Nathan Jones).

그림 10: 그림 9 히스토그램의 미러링을 통해 ADC 잡음의 근사치를 구합니다(이미지 출처: Nathan Jones).

자, 이제 이 모든 잡음을 어떻게 처리할 수 있을까요? 다행히 ADC의 분해능이 여전히 프로젝트 요구 사항 내에 있다면, 모든 ADC 측정값에 약간의 불확실성이 있다는 것만 기억하세요.

- 두 개의 ADC 값을 비교할 경우, 두 값의 차이가 6.6σ 이내이거나(이 경우 비교에 대한 신뢰도가 99.7%임) 1σ 이내(이 경우 신뢰도가 68%에 불과함)인 경우에만 서로 동등한 값으로 취급해야 합니다

- ADC 값을 임계값에 비교할 때 임베디드 시스템이 잡음만을 기반으로 하는 임계값 위/아래에서 다시 트리거링되지 않도록 하기 위해 (온도 조절기와 마찬가지로) 임계값 비교 시 약간의 히스테리시스를 추가합니다.

ADC가 프로젝트 요구 사항을 더 이상 충족하지 않는 것으로 판명될 경우 성능을 향상시키기 위해 시도할 수 있는 몇 가지 간단한 방법이 있습니다. 하드웨어 측면에서는 다음이 포함됩니다.

- AVCC 및 AREF에 잡음이 더 낮은 레퍼런스 사용(예: Texas Instruments REF5030 또는 EVVO TL431)

- PCB에서 아날로그 신호와 디지털 신호 사이의 누화 최소화

- 디지털 잡음을 줄이기 위해, ADC 변환 중 CPU 끄기(MCU가 지원하는 경우)

소프트웨어 측면에서는 잡음을 줄이기 위해 입력 신호가 오버샘플링될 수 있습니다(예: N개 샘플의 평균 사용). 이런 경우 최대 샘플링 속도가 확실히 감소하는 경향이 있습니다. 실제로, '오버샘플링 및 데시메이션'이라고 하는 기술은 입력이 오버샘플링되는 회수와 관련된 크기만큼 ADC의 분해능을 증가시키는 데 사용할 수 있습니다.

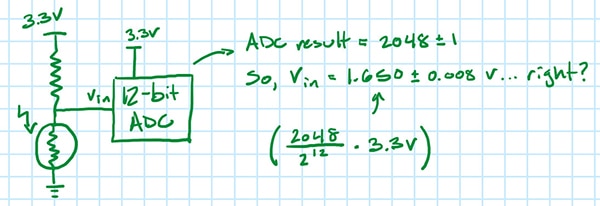

초기 설정을 위한 DC 히스토그램 테스트의 표준 편차가 1LSB라고 가정해 보겠습니다. 이제 ADC가 2048을 출력하면, (68%의 확률로) 실제 값이 1.650 ± 0.008V라는 뜻이 되는 걸까요(그림 11)?

그림 11: 그림 1 설정의 표준 편차가 1이고 ADC 출력이 2048이라고 가정할 때 실제 입력 전압은 1.650±0.008V일까요?(이미지 출처: Nathan Jones)

그림 11: 그림 1 설정의 표준 편차가 1이고 ADC 출력이 2048이라고 가정할 때 실제 입력 전압은 1.650±0.008V일까요?(이미지 출처: Nathan Jones)

매우 근접했지만 아직 아닙니다! 이는 모든 ADC가 일부 주파수에서 급변하는 입력 신호를 측정하는 데 어려움이 있어 측정 결과가 정확하지 않기 때문입니다(예: 잡음). 놀랍게도 이러한 현상이 발생하는 주파수는 ADC의 최대 샘플링 속도보다 훨씬 낮을 수 있습니다. 즉, 1MSPS(초당 메가 샘플 수)의 샘플링 속도를 갖는 12비트 ADC가 실제로는 500kHz 가까운 입력 신호에 대해 12비트 분해능을 갖지 않을 수 있으며, 입력 신호 주파수가 그 정도로 높으면 해당 ADC의 분해능이 6비트 이하로 떨어질 수 있습니다. 광저항기에서 10Hz가 넘는 신호를 측정하려고 할 때 ADC의 분해능은 실제로 12비트에 미치지 못할 수 있습니다.

더 높은 입력 주파수에서 ADC의 분해능이 얼마나 잘 유지되는지 확인하려면, 알려진 양호 신호(이 경우 사인파)를 보내고 ADC 값이 알려진 양호 신호와 얼마나 일치하는지 측정합니다(그림 12). (사인파가 '충분히 양호'한가에 대해서는 테스트 수행 절차가 공개된 후 논의될 것이며, 이렇게 하는 것이 훨씬 이해하기 쉬울 것입니다.)

그림 12: 알려진 양호 사인파 입력을 사용하는 테스트 설정(이미지 출처: Nathan Jones)

그림 12: 알려진 양호 사인파 입력을 사용하는 테스트 설정(이미지 출처: Nathan Jones)

사인파의 경우 함수 발생기를 사용하거나(예: 여러 USB 오실로스코프에서 사용되는 함수 발생기) DDS 칩(예: Analog Devices의 AD9834) 또는 맞춤형 사인파 생성기를 조립할 수 있습니다(예: Wien 브리지 발진기를 기반으로 하거나 Analog Devices의 MAX7400을 사용해 사인파를 저역 필터링하는 방식). 이 테스트에는 샘플링 주파수의 정수 하위 배수가 아닌 입력 주파수만 사용해야 합니다(예를 들어, 샘플 속도가 100kHz인 경우 입력 주파수 1kHz를 사용하면 안 됩니다). 이는 모든 주기에서 동일한 위치에서 사인파를 샘플링하는 오류를 회피하기 위한 것입니다. 또한, ADC에 대한 스트레스를 최대화하려면 입력 사인파의 진폭을 출력을 '클리핑'하지 않는 최대 값으로 설정하십시오(예: 위 예의 ADC의 경우 1.65V보다 약간 낮은 값).

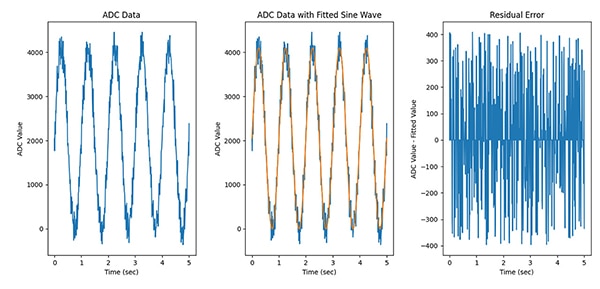

ADC 결과를 수집한 후, 잔여 오차를 계산하기 위해 데이터가 사인파에 피팅됩니다. 사인파 피팅은 어떤 데이터 양으로도 수행할 수 있지만 최적의 결과를 얻으려면 전체 주기의 입력 사인파가 최소 5개는 있어야 합니다. 사인 피팅 알고리즘은 진폭, 주파수, 위상 변이, 오프셋에 대한 초기 추정값을 제공하여 초기화해야 할 가능성이 큽니다(그림 13).

그림 13: 사인파 피팅 알고리즘을 사용하여 잔여 오차를 확인할 수 있습니다(이미지 출처: Nathan Jones).

그림 13: 사인파 피팅 알고리즘을 사용하여 잔여 오차를 확인할 수 있습니다(이미지 출처: Nathan Jones).

이 테스트는 ADC에 대한 사인파 피팅 테스트라고 하며, 잔여 오차의 RMS 값은 해당하는 특정 입력 주파수에서 ADC의 잡음 정도를 측정한 값입니다. 더 낮은 주파수에서는 RMS 잡음이 DC 히스토그램 테스트의 입력 참조 잡음과 일치해야 하지만, 더 높은 주파수에서는 위에서 설명한 이러한 주파수 종속 잡음원으로 인해 거의 확실하게 저하됩니다.

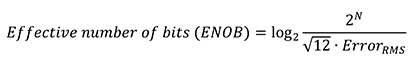

사인파 피팅 테스트의 RMS 잡음 값은 ADC의 ENOB(유효 비트 수), 즉 유일한 잡음원인 양자화 잡음이 ADC의 잡음과 동일한 RMS 값을 갖는 이상적 ADC의 비트 수를 계산하는 데 사용할 수 있습니다(방정식 6).

[6]

[6]

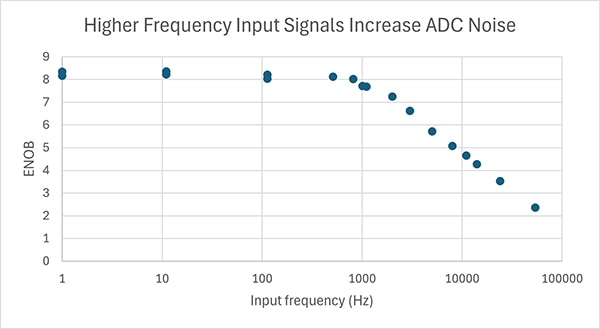

이 값은 사용된 입력 주파수에 따라 다릅니다. ADC를 더욱 완전하게 파악하려면, 이 테스트를 관심 있는 최고 입력 신호까지 또는 최대 샘플링 속도의 1/2에 이르는 주파수에서 반복해야 합니다. 최대 샘플링 속도의 절반보다 훨씬 낮은 주파수에서는 잡음이 크게 올라가고 ENOB는 크게 감소할 수 있습니다. 예를 들어, 동일한 일련의 테스트를 STMicroelectronics STM32F042K6의 ADC에서 수행하고 결과를 플로팅할 수 있습니다(그림 14).

그림 14: STM32F042K6 마이크로 컨트롤러의 ADC에 대한 주파수 잡음 테스트 그래프(이미지 출처: Nathan Jones)

그림 14: STM32F042K6 마이크로 컨트롤러의 ADC에 대한 주파수 잡음 테스트 그래프(이미지 출처: Nathan Jones)

STM32F042K6 마이크로 컨트롤러의 ADC는 1MHz에서 샘플링할 수 있지만 1kHz 이상에서는 분해능이 떨어집니다. 이 ADC로 10kHz 신호를 측정하려고 한다면, 그때의 분해능은 약 5비트에 불과합니다. 또한, 최대 ENOB는 약 8.3 정도에 불과합니다. 이는 DC에서도 약 10LSB의 잡음이 존재하여 ADC의 유효 분해능이 12비트에서 약 8.7비트로 감소하기 때문입니다. 이 테스트는 개조되지 않은 STMicroelectronics Nucleo-F042 개발 기판에서 수행되었으며, 위의 [이제 이 모든 잡음을 어떻게 처리할 수 있을까요?]에서 언급한 기술 중 하나라도 사용한다면, 결과는 훨씬 더 개선될 것입니다.

사인파의 잡음 레벨을 확인하는 방법

전압 레퍼런스와 마찬가지로, 사인파의 잡음 레벨이 선험적인 경우(즉, 규격서에서 제공되지 않는 경우) 오실로스코프로 측정해야 합니다. 앞에서 설명한 사인파 피팅 기법을 사용하면 사인파 생성기의 잡음을 특성화할 수 있습니다.

- 먼저 오실로스코프의 입력을 접지에 연결하고 출력의 RMS 값을 계산하여 오실로스코프의 잡음 플로어를 결정합니다([전압원의 잡음 레벨을 확인하는 방법]의 앞 부분에 설명되어 있음).

- 그런 다음 사인파 생성기의 출력을 측정하고 결과를 완벽한 사인파에 피팅한 후 잔차의 RMS 값을 계산합니다. 그런 다음 방정식 2를 사용하여 사인파 생성기의 잡음을 결정합니다(오실로스코프의 잡음 플로어를 AC 잡음의 근사치로 사용).

- 아날로그 핀에 연결된 장치의 출력 임피던스가 매우 낮은지 확인하고, 버퍼링을 위해 연산 증폭기를 삽입할 수 있습니다.

- 내부 커패시터가 충전할 수 있는 충분한 시간을 제공하면서 ADC 클록 또는 샘플/홀드 시간을 가능한 한 빠르게 조정합니다.

- 저지터 ADC 클록 소스를 사용하고 일정한 간격으로 ADC 샘플을 가져오도록 시스템을 구성합니다.

- Characterizing the Raspberry Pi Pico ADC

- Understanding Data Converters (Texas Instruments)

- Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor (Analog Devices)

- The Good, the Bad, and the Ugly Aspects of ADC Input Noise--Is No Noise Good Noise? (Analog Devices)

- Getting the most out of the SAM D21's ADC (Thea Codes)

- "Analog-to-Digital Converter Testing" (Kent Lundberg)

- Dynamic Tests For A/D Converter Performance (Texas Instruments)

- How to optimize the ADC accuracy in the STM32 MCUs (STM)

- Enhancing ADC resolution by oversampling (Atmel)

- Fundamentals of Precision ADC Noise Analysis (Texas Instruments)

- ADC Gain and Offset Error Calibration on ARM® Cortex®-M0+ Based MCUs (Microchip)

- Sine wave generation via low-pass filtering a square wave

- Understanding the impact of digitizer noise on oscilloscope measurements (EE Times)

- Understanding Effective Number of Bits (Robust Circuit Design)

이상적으로는 사인파의 잡음 레벨이 ADC에서 예상되는 잡음 레벨의 1/3 미만(즉, 사인파가 '스펙트럼적 순수')이어야 하며 이렇게 되면 사인파가 측정된 잡음에 미치는 영향은 거의 무시할 수 있습니다. 사인파의 잡음 레벨이 이보다 높으면 잔차 오차의 RMS 값을 계산하여 얻은 측정된 잡음에서 사인파의 잡음 레벨을 빼야 합니다.

이 테스트는 ADC를 테스트하는 데 사용하려는 모든 입력 주파수에 대해 반복해야 합니다.사인파 생성기에도 주파수 종속 잡음원이 있을 수 있습니다.

이 모든 잡음을 어떻게 처리할 수 있을까요? 먼저, 고주파 잡음을 제한하기 위해 신호 소스와 ADC 사이에 LPF(저역 통과 필터)를 배치하고 차단 주파수는 관심 있는 신호의 가장 높은 주파수 바로 위로 설정하는 것이 좋습니다(이는 일반적으로 모든 데이터 획득 시스템에서 '좋은 방법'입니다). 관심 있는 신호의 최고 주파수가 ENOB 대 입력 주파수 그래프에서 ‘무릎'보다 낮다면, 분해능 손실이 없는 것입니다. 이 '무릎' 보다 높은 주파수를 가진 신호를 측정하려고 할 때, 더 높은 주파수에서 분해능을 개선하기 위해 시도할 수 있는 몇 가지 방법이 있습니다. 여기에는 다음이 포함됩니다.

매우 협소한 주파수 대역의 신호가 목표가 아니라면, 다음으로 가장 간단한 방법은 실제 입력 신호가 DC부터 LPF의 차단 주파수까지 동일한 주파수 성분을 가지므로 모든 ADC 측정의 RMS 잡음은 DC부터 차단 주파수까지 사인파 피팅 테스트를 사용하여 측정한 평균 RMS 잡음이라고 가정하는 것입니다. 앞서 설명한 STM32F042K6을 사용하여 최대 10kHz의 광대역 신호를 측정하려는 경우 각 측정에 대해 ADC에 약 6비트의 ENOB만 있는 것처럼 작동하는 것이 가장 좋습니다. 이 값은 DC 히스토그램 테스트를 사용하여 구한 값보다 매우 낮을 수 있으며, 이는 각 신호에 더 높은 주파수 성분이 있을 가능성이 있는 경우 각 ADC 측정값에 대한 확실성이 낮아진다는 것을 나타냅니다.

다음으로 고려할 가정은, 센서와 ADC 사이에 LPF를 추가하여 DC부터 차단 주파수까지의 RMS 잡음이 ±1LSB에 불과하도록 하는 것입니다. 이제 ADC가 2048을 출력하면, (68%의 확률로) 실제 값이 1.650 ± 0.008V라는 뜻이 되는 걸까요(그림 15)?

그림 15: 회로에 저역 통과 필터를 추가하면 실제 값이 1.650±0.008V가 되나요(이미지 출처: Nathan Jones)?

그림 15: 회로에 저역 통과 필터를 추가하면 실제 값이 1.650±0.008V가 되나요(이미지 출처: Nathan Jones)?

짜증 나시겠지만 아직 아닙니다! 이 기사에서는 ADC의 잡음을 효과적으로 특성화했지만 아직 오차를 특성화하지는 않았습니다. 여기에 설명된 테스트를 수행한 후 확신할 수 있는 것은 두 ADC 값이 같은지 또는 다른지뿐입니다. ADC 코드 2048이 정확히 1.65V에 해당하는지 여부는 알 수 없습니다. 이득, 오프셋, 차동 비선형성 오차 등으로 인해 ADC 코드에서 실제 전압으로 변환하는 것이 Vin=ADC result × VFS/2N을 사용하는 것보다 더 복잡할 수 있습니다. 하지만 이 주제는 다른 기사에서 다루도록 하겠습니다.

참고 자료

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.