ADC/DAC 자습서

DigiKey 제공

2017-09-13

오늘날의 세상은 디지털 신호와 아날로그 신호가 넘쳐납니다. 이러한 신호는 서로 다르게 동작하지만 두 신호는 모두 더 큰 목표를 달성할 수 있도록 도와줍니다. HVAC 장치 제어 작업을 수행하는 엔지니어를 상상해 보세요. 마이크로 컨트롤러 또는 마이크로 프로세서를 사용하려면 무한대의 값을 가진 아날로그 온도를 읽어서 이산 소자 스텝에 레이아웃되는 이진 표현으로 변환할 수 있어야 합니다. 이 이진 표현 아날로그 값은 마이크로 컨트롤러 또는 마이크로 프로세서에서 처리됩니다. 이 데이터는 HVAC 장치에서 공정을 실행하여 안정적인 환경을 유지할 수 있도록 도와줍니다. 디지털 시스템에서 처리되어야 하는 아날로그 값을 처리할 경우 아날로그 디지털 컨버터(ADC)가 필요합니다. 아날로그 신호로 변환되어야 하는 디지털 신호에도 동일한 이론을 적용할 수 있습니다. 온라인으로 노래를 스트리밍할 경우 디지털 신호를 아날로그 신호로 변환하는 데 사용되는 몇 가지 스텝을 포함합니다. 서버로부터 호스트 장치에 수신되는 신호는 원본 아날로그 신호의 이진 표현입니다. 이 이진 데이터의 가청 응답은 수신자가 이해할 수 없습니다. 원본 신호가 아날로그이므로 최종 신호도 아날로그여야 합니다. 이 문제는 디지털 아날로그 컨버터(DAC)를 사용하면 해결됩니다. 이러한 유형의 장치에서는 아날로그 디지털 컨버터에서 인코딩된 이진 코드를 가져와서 아날로그 전압으로 되돌립니다.

아날로그 디지털 신호 변환 또는 디지털 아날로그 신호 변환은 오늘날의 엔지니어에게 불가피한 작업입니다. 다양한 종류의 아날로그 디지털 컨버터 및 디지털 아날로그 컨버터가 있습니다. 종류마다 아키텍처가 다르지만 모든 컨버터는 비슷한 용도로 사용됩니다. 아날로그 값으로 디지털 신호를 처리할 수 없습니다. 이는 프랑스어를 사용하는 사람이 독일어를 사용하는 사람과 대화하려고 하는 경우와 비슷합니다. 통역이 없이는 가능하지 않습니다. ADC 장치와 DAC 장치가 통역 역할을 할 수 있습니다. ADC에서는 아날로그 전압이 표시되면 지정된 기간에 아날로그 전압을 이진 코드로 전환합니다. 즉, ADC에서는 즉시 아날로그 전압을 샘플링한 다음 ADC의 출력 부분에서 이진 값을 결정합니다. 장치에서 초당 가져오는 샘플량은 설명서에 명시되어 있습니다. 예를 들면 Maxim Integrated의 MAX1118EKA+T가 있습니다. 이 장치는 샘플링 속도가 100kHz이므로 입력 부분에서 초당 100,000회의 속도로 아날로그 전압을 샘플링할 수 있습니다. 초당 이렇게 많은 샘플을 가져올 수 있으므로 이진 해석을 사용하여 아날로그 전압을 정확히 기록할 수 있습니다. ADC의 샘플링 속도가 낮아서 앨리어싱을 일으키는 입력을 정확히 다시 생성할 수 없는 경우도 있습니다. 이 경우 신호가 다른 신호 또는 다른 신호의 앨리어스와 구분되지 않습니다. 녹화할 때 초당 24프레임을 촬영할 수 있는 동영상 카메라를 상상해 보세요. 대부분의 응용 분야에서는 이 정도로 충분하지만, 매우 빠르게 움직이는 사물을 보려는 경우에는 그림이 왜곡될 수 있습니다. 90년대 후반에 TV 시청이 녹화에 미친 영향을 생각해 보세요. TV의 그림이 깜박거립니다. TV 화면 주사율이 녹화 시 지정된 초당 프레임 속도로 캡처할 수 있는 것보다 훨씬 더 빠르기 때문입니다. 동영상은 실제로 연속된 일련의 그림이므로 이미지가 왜곡됩니다. 이러한 왜곡은 동영상에 실제로 나타나는 각 그림 사이에서 많이 발생합니다. ADC에서도 동일한 효과가 발생할 수 있습니다. 이 문제를 방지하려면 샘플링 속도가 전송해야 하는 최대 주파수보다 2배 이상 높아야 합니다. 이를 나이퀴스트 속도라고 합니다.

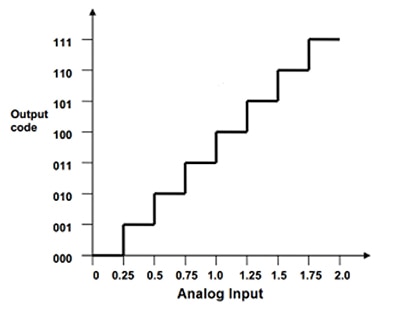

샘플링 속도가 높을수록 장치는 더 정확할 수 있지만 이것이 정확성을 제어하는 유일한 방법은 아닙니다. 이 경우 아날로그 신호를 이진 코드로 변환하므로 특정 시점에 전압을 표시하는 데 사용할 수 있는 이산 소자 스텝은 한정적입니다. 이 수를 표시하는 데 사용될 수 있는 비트 수가 분해능입니다. ADC의 분해능이 높을수록 ADC에서 사용할 수 있는 이산 소자 스텝이 더 많아집니다. 자세히 알아보려면 ADC에서 만들 수 있는 스텝 수를 결정하는 방법을 이해해야 합니다. ADC에는 공급 전압을 나타내는 이진 출력이 있습니다. 공급 전압이 10V이고 8비트 ADC가 있을 경우 256스텝이 가능합니다. 분해능을 결정하려면 2n 방정식을 사용합니다. “2”는 상수이고 N은 비트 수입니다. 28을 적용하면 256스텝이 됩니다. 10V 공급 전압에서 256스텝을 사용할 경우 각 스텝은 39.0625mV가 됩니다. 스텝마다 다른 이진 코드가 있습니다. 가장 낮은 스텝부터 가장 높은 스텝까지 ADC에서 사용 가능한 모든 입력 옵션을 실행할 경우 계단의 아웃라인이 표시됩니다. 이 계단은 ADC의 전달 함수입니다. 그림 1은 2V 레퍼런스를 제공하는 3비트 ADC를 통한 전송을 보여줍니다.

그림 1: 2V 레퍼런스를 제공하는 3비트 ADC의 전달 함수 (Microchip Technology 제공)

3비트가 있으므로 다음과 같이 2n 방정식을 사용하여 총 스텝 수를 계산할 수 있습니다.

![]()

그림 1을 보면 000과 111 사이에 8개의 스텝이 있습니다. 스텝마다 LSB가 하나씩 높아집니다.

앞에서 설명한 것처럼 몇 가지 종류의 ADC 아키텍처가 있습니다. 가장 많이 사용되는 세 가지 ADC 아키텍처는 연속 근사화 레지스터(SAR), 델타 시그마(∆∑) 및 파이프라인 컨버터입니다. 각 아키텍처는 아날로그 신호를 디지털 출력으로 변환하지만 작업 방법이 약간씩 다릅니다. SAR은 아날로그 입력을 샘플링하여 유지한 다음 디지털 신호로 전환한 후 전달합니다. 델타 시그마 컨버터는 디지털 신호로 변환하는 데 걸린 시간에 대한 샘플링 평균을 구합니다. 파이프라인 컨버터는 변환을 다른 스테이지로 나누어 매우 빠른 변환 속도를 실현합니다. 각 컨버터는 장단점이 있습니다. SAR 아키텍처는 사용이 간편하며 일반적으로 전력 소비가 낮고 대기 시간은 짧은 반면에 정확성은 높습니다. 델타 시그마는 분해능이 매우 높고 안정성이 높은 반면에 전력 소비와 비용은 낮지만 SAR 및 파이프라인 아키텍처보다 속도가 훨씬 느립니다. 파이프라인 ADC는 이전 예제보다 더 높은 속도와 더 높은 대역폭에서 작동하지만 분해능이 더 낮고 실행하는 데 더 많은 전력이 필요합니다.

연속 근사화 레지스터

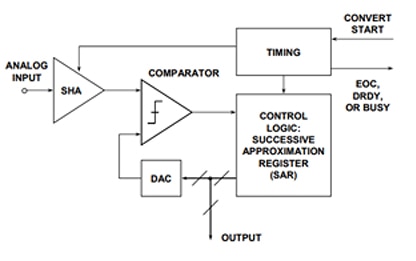

연속 근사화 레지스터는 가장 널리 사용되는 ADC 유형입니다. 주로 I2C 또는 SPI 인터페이스가 있지만 병렬 출력이 있는 경우도 있습니다. 아날로그 신호를 처리할 수 있도록 SAR ADC에는 신호를 일정하게 유지하는 샘플 앤 홀드가 있습니다. 내부 DAC에 대하여 아날로그 입력을 측정하는 비교기가 있습니다. 이 DAC는 이 지점에서 전위 전압의 ½로 설정됩니다. 입력이 DAC보다 높은 경우 비교기는 1을 출력하여 ‘연속 근사화 레지스터’의 MSB에 저장합니다. 이후에는 DAC가 전위 전압의 ¼로 설정되고 공정이 반복됩니다. 모든 비트가 레지스터에 로드될 때까지 DAC의 다음 값은 1/8, 1/16 등의 순으로 설정됩니다. 무게를 연속적으로 추가하거나 추가하지 않고 다른 무게를 확인하는 이 그림은 유사성이 있습니다. 아래 그림 2는 이 점을 보여줍니다.

그림 2: 연속 근사화 ADC가 아날로그 값에서 디지털 값을 얻는 방법을 보여주는 비유 (Analog Devices 제공)

블록 = 45단위이며, 첫 번째 테스트에서는 각각 단위가 1인 작은 블록 32개를 사용합니다. 여전히 블록이 작은 블록들보다 더 무겁습니다. 블록이 여전히 더 무거우므로 작은 블록은 그대로 유지됩니다. 다음 테스트에서는 작은 블록을 16개 더 추가합니다. 그러면 32개 + 16개 = 48개가 되어 너무 무겁습니다. 따라서 블록 중 16개를 제거합니다. 다음 테스트에서는 저울에 블록을 8개 더 추가합니다. 이제 32개 + 8개 = 40개로 수량이 늘어납니다. 이제 블록을 4개 더 추가하여 44개로 만들 수 있습니다. 블록을 2개 더 추가하면 46단위가 되어 45단위보다 더 많으므로 블록이 제거됩니다. 마지막으로 양쪽의 블록 무게가 같아지도록 블록을 1개 추가합니다. 블록을 추가할 때마다 추가되는 수는 반으로 줄어듭니다. 이는 SAR의 DAC에서 제공되는 값을 나타냅니다. 그림 3은 연속 근사화 레지스터 ADC의 제품 구성도를 보여줍니다.

그림 3: 연속 근사화 ADC 기능별 제품 구성도 (Analog Devices 제공)

SAR ADC의 예로 Texas Instruments의 ADS7886SDBVT가 있습니다. 0V와 공급 전압 사이에 4,096개 스텝을 사용할 수 있는 12비트 ADC입니다. 샘플링 속도는 1MHz로 입력을 초당 100만 번 읽습니다. 완제품으로 구현하기 이전에 ADC 성능을 테스트해야 하므로 제조업체에서 테스트에 도움이 되는 평가 도구를 만들 수 있습니다. ADS7886SDBVT에는 ADS7886EVM이라는 평가 도구가 있습니다. ADC를 기능적으로 테스트하는 데 필요한 모든 수동 소자 부품이 이미 기판에 탑재되어 있으므로 테스트가 훨씬 더 쉬워집니다.

시그마 델타 ∆∑

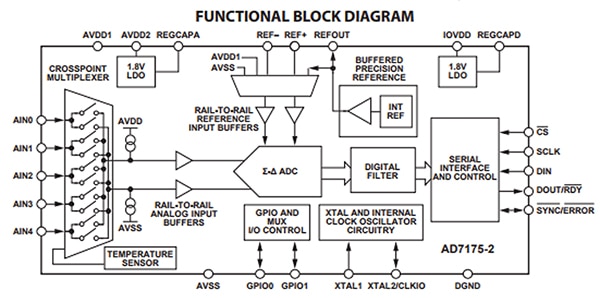

시그마 델타 컨버터는 높은 분해능과 정밀도가 필요한 경우에 매우 널리 사용됩니다. 오디오 녹음은 시그마 델타 컨버터 응용 분야의 좋은 예입니다. 시그마 델타 컨버터에서는 입력을 초과 샘플링해야 합니다. 시그마 델타 컨버터는 나이퀴스트 속도와 무관하지만, 샘플링 속도가 샘플링할 최대 주파수보다 약 20배 더 높을 때 최적의 상태로 작동합니다. 시그마 델타 컨버터의 출력은 비트 스트림을 처리하여 최종 출력을 생성하는 디지털 필터 및 데시메이터에 제공됩니다. 디지털 필터와 출력 사이에 직렬 인터페이스가 있는 경우가 있습니다. 시그마 델타 ADC의 예로는 Analog Devices, Inc의 AD7175-2BRUZ가 있습니다. 그림 4는 AD7175-2BRUZ의 ‘기능별 제품 구성도’를 보여줍니다.

그림 4: Analog Devices의 AD7175-2BRUZ 시그마-델타 ADC 기능별 제품 구성도 (Analog Devices 제공)

시그마 델타 ADC의 분해능은 24비트이고 샘플링 속도는 250kHz입니다. 전위는 최대 16,777,216스텝입니다. 즉, 이전 예제보다 분해능이 훨씬 더 높지만 샘플링 속도의 약 ¼입니다. 이전 예제와 마찬가지로 AD7175-2BRUZ에도 테스트용 평가 기판이 있습니다. 이 기판은 EVAL-AD7175-2SDZ이며 ADC를 쉽게 평가할 수 있도록 해줍니다.

파이프라인

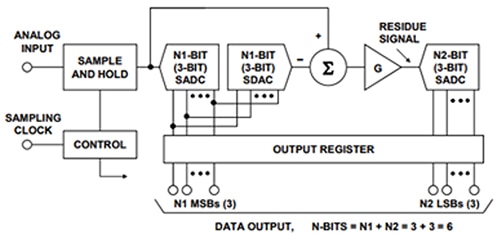

파이프라인 ADC가 가장 빠릅니다. ‘ADC 아키텍처 V: 파이프라인 서브레인지 ADC’ 예에서는 6비트 파이프라인 ADC를 사용하여 설명합니다. 샘플 앤 홀드는 SAR과 비슷하지만 샘플 앤 홀드 바로 뒤에 신호를 디지털화하는 3비트 서브-ADC 플래시 컨버터가 있습니다. 3비트 변환은 최상위 비트 3개를 위한 것입니다. 서브-DAC를 사용하여 이 비트를 아날로그 신호로 다시 변환합니다. 이 출력을 샘플 앤 홀드 출력에서 빼서 증폭한 다음 나머지 세 최하위 비트에 대한 두 번째 스테이지 3비트 서브-ADC로 다시 보냅니다. 그림 5에는 이 점을 보여주는 제품 구성도가 있습니다.

그림 5: 파이프라인 서브레인지 ADC 기능별 제품 구성도. (Analog Devices 제공)

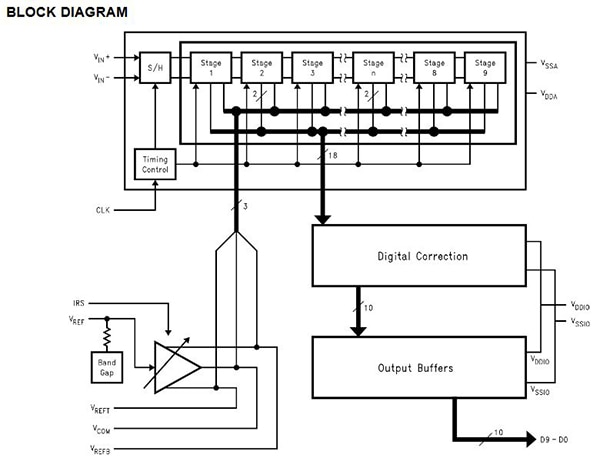

파이프라인 ADC의 예로 Texas Instruments의 ADC10080CIMT/NOPB가 있습니다. 이 ADC는 10비트 ADC이므로 전위가 1,024스텝이고 초당 80Ms를 변환할 수 있습니다. 이 장치에 대한 응용 분야로는 초음파 진단기, 계측, 데이터 취득 시스템을 비롯하여 고속 변환을 포함하는 거의 모든 분야가 해당됩니다. ADC10080CIMT/NOPB 제품 구성도를 보면 위에 설명한 설정 방법을 알 수 있습니다. 그림 6에는 ADC1008CIMT/NOPB 규격서에서 가져온 제품 구성도가 있습니다.

그림 6: Texas Instruments의 ADC10080CIMT/NOPB 기능별 제품 구성도 (Texas Instruments 제공)

이진 가중 DAC

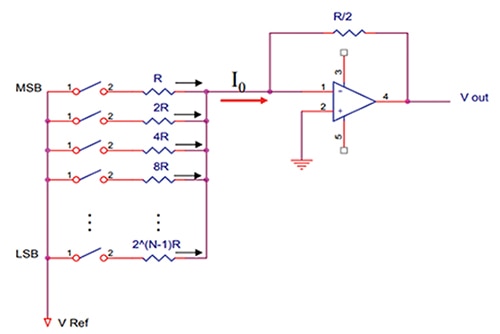

지금까지 이 기사에서 데이터 변환의 ADC 부분을 중점적으로 살펴보았고 앞으로 아직 반이 남아 있습니다. 이진 데이터를 아날로그 신호로 다시 변환해야 하는 경우가 있습니다. 이 경우 디지털 아날로그 디지털 컨버터가 사용됩니다. 대부분 학교에서 가장 먼저 배우는 DAC 유형은 이진 가중 DAC입니다. 여기서는 저항기 시스템을 사용하며 이 시스템의 출력은 모두 동일한 가산 저항기에서 만납니다. 상위 비트일수록 하위 비트보다 더 많은 전류를 출력합니다. 이를 위해 반비례 저항 회로망을 생성합니다. 디지털 코드의 각 이진 비트는 전압 값이 동일하므로 각 비트에서 반비례 저항기를 사용하여 비트가 높을수록 더 많은 전류를 흐르게 할 수 있습니다. 현재는 더 쉬운 방법이 사용되므로 이 변환 방법은 더 이상 많이 사용되지 않지만, DAC의 작동 방법을 설명할 때 매우 좋은 시작점이 됩니다. 이 방법에서는 함께 작동할 다양한 수준의 저항기를 찾는 것이 가장 큰 문제입니다. 허용 오차 범위를 매우 정밀하게 설정해야 하며, 이진 가중 방법을 사용할 때처럼 여러 개의 다른 값을 찾을 필요 없이 비슷한 값을 가진 저항기를 쉽게 찾을 수 있습니다. 그림 7은 이진 가중 저항기 회로망의 회로도를 사용하여 이 아키텍처를 보여줍니다.

그림 7: 이진 가중 레지스터 회로망 회로도 (Georgia Institute of Technology 제공)

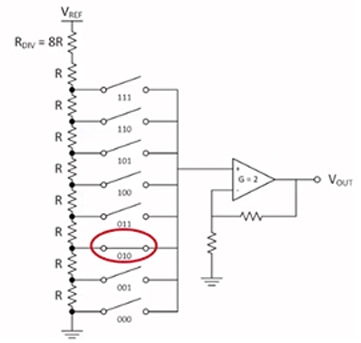

스트링 DAC

널리 사용되는 다른 DAC용 아키텍처로는 스트링 DAC가 있습니다. 가장 간단한 최소 선형 아키텍처이며, 켈빈 분배기라고도 합니다. 직렬로 연결된 등가 저항기 스트링이 있습니다. 스트링의 맨 위에 참조 전압이 있고 스트링 앞에 고 임피던스 저항기가 있으며 각 노드에는 이진 코드 전용 스위치가 있습니다. 장치에서 코드를 읽으면 이 스위치가 닫힙니다. 따라서 이진 입력에 따라 아날로그 전압 값을 사용할 수 있습니다. 그림 8은 Texas Instruments의 ‘What is a String DAC?’ 동영상에서 발췌한 것입니다. 코드 010은 십진수 값 2를 나타냅니다. 이제 010에서 스위치가 닫히며 해당 노드의 DC 전압을 가산 증폭기에 전달할 수 있습니다.

그림 8: 스트링 DAC의 회로도 (Texas Instruments 제공)

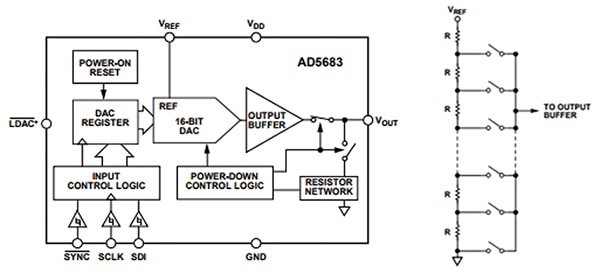

스트링 DAC는 스트링의 모든 부분에서 값이 동일한 저항기를 사용하므로 쉽게 생산할 수 있습니다(고 임피던스 저항기 제외). 스트링 DAC의 예로는 Analog Devices Inc.의 AD5683RBRMZ가 있습니다. 이 DAC는 SPI에서 작동하는 16비트 스트링 DAC입니다. 그림 9는 이 장치의 기능별 제품 구성도를 보여주고 그림 10은 저항 분배기를 보여줍니다. 또한 이 제품에는 평가 도구인 EVAL-AD5683RSDZ가 있습니다.

그림 9 및 10: Analog Devices의 AD5683RBRMZ(왼쪽) 및 저항기 분배기 회로망(오른쪽)의 기능별 제품 구성도. (Analog Devices 제공)

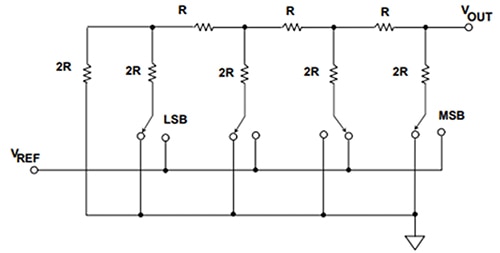

R-2R

R-2R 회로망은 매우 일반적인 DAC 아키텍처입니다. 이 회로망에서는 저항기 값을 두 개만 사용하며, 2R이 R의 2배이기만 하면 값은 중요하지 않습니다. 따라서 R-2R DAC의 확장성이 매우 우수합니다. DAC의 비트 수에 상관없이 저항기 값이 두 개만 있으면 됩니다. 그림 11은 4비트 R-2R 래더 회로망을 보여줍니다.

그림 11: R-2R DAC 회로도. (Analog Devices 제공)

이 분배기 회로망에서는 데브난의 정리를 사용하여 전체 회로망 “R”에 대한 데브난의 등가 저항을 가져옵니다. 모든 스테이지에서는 마지막 스테이지보다 2배 높은 전압이 허용됩니다. 이 예에서 Vref가 5V일 경우 LSB의 맨 왼쪽 스테이지에서는 0.3125V만 생성할 수 있습니다. 왼쪽에서 오른쪽으로 이동할 때 비례 전압 출력은 다음과 같습니다.

![]()

모든 디지털 입력을 나타내며, X0은 LSB이고 X3은 MSB입니다. 5V 참조 전압을 사용할 경우 다음과 같습니다.

![]()

동일한 논리로 최상위 비트에 대한 아날로그 전압을 찾으려면 다음과 같이 할 수 있습니다.

![]()

1111이라는 이진 입력이 있을 경우 출력은 5V가 아닙니다. 앞에서 설명한 분해능 과정을 기억해 보세요. 4비트 DAC가 있을 경우 16개의 스텝이 존재할 수 있습니다. 즉, 허용되는 스텝 수는 24 = 16개이기 때문입니다. LSB가 0.3125V에 있습니다. 만약 0.3125를 16으로 곱하면 정답은 5가 됩니다. 그러나 스텝 중 하나가 이진수 0000을 나타내는 0V 접지를 포함하므로 이는 잘못되었습니다. 즉, 달성할 수 있는 최고 전압은 공급 전압에서 1 LSB 전압을 뺀 값입니다. 따라서 4.6875V가 됩니다.

![]()

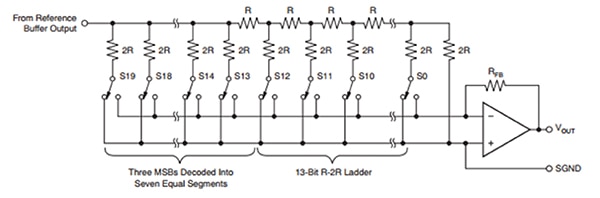

R-2R DAC의 예로 Texas Instruments의 DAC8734SPFB가 있습니다. 이 DAC는 장치의 확장성을 보여주는 16비트 컨버터입니다. 여기서 R-2R 회로망에 사용되는 레이아웃은 위에서 설명한 것과 흡사합니다. 그림 12는 DAC8734SPFB용 R-2R 회로망을 보여줍니다. 또한 DAC8734EVM이라는 DAC8734SPFB용 평가 도구가 있습니다.

그림 12: Texas Instruments의 DAC8734SPFB R-2R DAC 회로도 구성도 (Texas Instruments 제공)

다양한 종류의 ADC/DAC 아키텍처가 있지만 이 기사에서는 널리 사용되는 몇 가지 아키텍처에 대해서만 살펴봅니다. 이러한 장치는 오늘날의 디지털 신호 처리 환경에 꼭 필요합니다. ADC/DAC 장치가 없으면 아날로그 출력을 디지털 신호 처리에 통합하거나 디지털 출력을 아날로그 신호 처리에 통합할 수 없습니다. 이 단계는 비전문가라도 쉽게 수행할 수 있지만 아날로그 부품을 디지털 시스템에 연결하는 업무를 담당하는 엔지니어라면 고려해야 할 가장 중요한 단계입니다. 아날로그 디지털 변환은 두 사람이 서로 다른 언어로 대화하는 것과 비슷합니다. 통역이 없다면 이 두 사람은 서로 의사소통을 할 수 없습니다. ADC/DAC 장치를 적절히 활용하지 않을 경우 장치에서 아날로그만 사용하거나 디지털만 사용해야 합니다. ADC/DAC 장치는 두 환경 간의 유용한 응답 확인 방식입니다.

관련 자료

- “AVR127: ADC 파라미터 이해” 2016년 5월.

- “응용 분야에 적합한 A/D 컨버터 선택” 2017년 5월 8일 검색.

- Kester, Walt. “ADC 아키텍처 II: 연속 근사화 ADC” 2008년 10월.

- Kester, Walt. "ADC 아키텍처 III: 시그마 델타 ADC 기본 사항" 2008년 10월.

- Kester, Walt. "ADC 아키텍처 IV: 시그마 델타 ADC 고급 개념 및 응용 분야" 2008년 10월.

- Kester, Walt. “ADC 아키텍처 V: 파이프라인 서브레인지 ADC” 2008년 10월

- Kester, Walt. "DAC 인터페이스 기초" 2008년 10월.

- Kester, Walt. “기본 DAC 아키텍처 II: 이진 DAC” 2008년 10월.

- Lee, J., Jeelani K., Beckwith, J. “디지털 아날로그 컨버터” 2017년 5월 8일 검색.

- Poole, Matt. “스트링 DAC란?” 2016년 4월 4일

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.