Spartan 에지 가속 기판

대상 사용자

- 교수

- DIY 엔지니어

- 제작가

- FPGA 개발자

- 학생

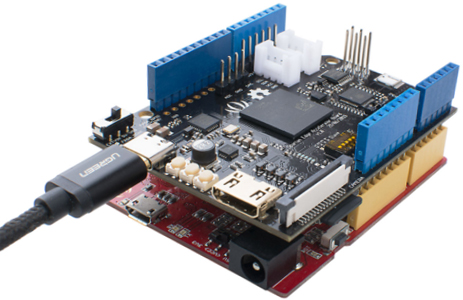

Spartan 에지 가속 기판(SEA 기판)은 Xilinx Spartan-7 칩 기반 경량 FPGA 개발 기판으로 Arduino 차폐 폼 팩터를 따릅니다. 따라서 LCD 및 카메라를 구동하기 위한 Arduino 차폐 또는 독립형 FPGA 개발 기판으로 사용할 수 있습니다. 또한 온보드 ESP32 칩을 통해 SEA 기판은 WiFi 및 Bluetooth 기능을 사용하여 Arduino를 활성화합니다.

Spartan-7은 Xilinx의 FPGA 제품군 중 가장 비용 효율적인 최신 FPGA 칩으로 동급 최고의 와트당 성능을 제공합니다. 또한 Arduino용 전체 FPGA API를 제공하므로 Arduino 사용자는 FPGA에 대한 경험 없이도 FPGA 기능을 사용할 수 있습니다. 이 기판은 간단한 이미지 처리 및 컴퓨터 비전 애플리케이션, 신호 암호화 및 암호 해독, 신호 샘플링 및 처리와 같은 다양한 방식으로 Arduino의 기능을 확장합니다.

- 특징

- 사양 및 기판 주변기기

- 시작하기 및 참조 설계

특징

- 통합 mipi, 미니 HDMI 인터페이스

- Raspberry Pi 카메라 v1.0(OV5640) 지원

- 30fps 이미지 전송에 대한 최대 지원

- IoT WiFi 및 Bluetooth(ESP32 포함)

- AWS, Azure 및 기타 클라우드 서비스 지원

- 소프트웨어 암호화 알고리즘 지원

- 20개의 사용자 정의 확장 I/O 포트(독립형 모드)

- 10개의 사용자 정의 확장 I/O 포트(Arduino 차폐 모드)

- Arduino용 전체 FPGA API

- 8비트 ADC 및 DAC

- 6축 가속도계 및 자이로스코프

- 2개의 사용자 RGB LED 및 버튼

- Arduino 차폐 모드

- FPGA 독립형 모드

응용 분야

- MIPI 카메라 입력 및 HDMI 출력 Vivado 엔지니어링

- 온보드 LED, DIP 스위치, ADC 및 DAC 참조

- 온보드 자이로스코프

- Arduino용 GPIO/UART/ADC/DAC/RGB-LED 확장 제공

- 신호 발생기(Arduino 구성 필요)

- ESP32 제어 신호 발생기

- AWS GreenGrass IoT 플랫폼 사용

- 색상 인식 및 물체 추적

- 그래픽 인식(삼각형, 원형, 사각형 인식)

- 디지털 문자 인식

- FPGA에서 AES 암호화 및 암호 해독 알고리즘 구현

- FPGA에서 PID 알고리즘 구현

FPGA 사양

주의

SEA 차폐의 IO 전압은 5V, FPGA의 IO 전압은 3.3V이며 IO 전압이 호환되도록 분압기를 제작하였습니다. SAM D21 계열의 3.3V IO 전압은 분압 후 3.3V 미만이므로 FPGA의 IO를 구동하기에 충분하지 않습니다. 따라서 현재 SEA 개발 기판은 Arduino UNO 및 Seeeduino V4.2와 같은 5V IO Arduino 기판만 지원합니다.

| FPGA 칩 | Spartan-7 XC7S15 | 논리 셀 | 12,800 |

|---|---|---|---|

| 슬라이스 | 2000 | CLB 플립 플롭 | 16,0000 |

| 최대 분산 RAM(Kb) | 150 | 블록 RAM/FIFO w/ECC(각각 36kb) | 10 |

| 총 블록 RAM(Kb) | 360 | 클록 관리 타일(MMCM 1개 + PLL 1개) | 2 |

| DSP 슬라이스 | 20 | 무선 칩 | Espressif ESP32-D0WDQ6 |

| WiFi | 802.11b/g/n 2.4GHz | Bluetooth | BLE 지원 블루투스 4.1 |

| 동영상 | 미니 HDMI x 1 | 카메라 | CSI/MIPI 인터페이스 x1(Raspberry Pi 카메라 V1 - OV5640과 호환) |

| SD 카드 | 마이크로 SD/TF 카드 슬롯 1개 | FPGA GPIO | 10핀 헤더(IO9~IO0) |

| Arduino GPIO | 32핀 헤더(Arduino 폼 팩터) | Grove | Grove 커넥터 2개(I2C/D2) |

| LED | 모노크롬 LED x2 | 버튼 | 부팅 1개 |

| 리셋 1개 | |||

| RGB LED 2개 | FPGA 리셋 1개 | ||

| 사용자 2인 | |||

| 스위치 | 전원 모드 스위치 1개 | 작동 전압 | 5V |

| 5채널 DIP 스위치 1개 | |||

| IO 전압 | 5V | 전원 모드 | USB Type C 5V |

| VIN 8~17V | |||

| Arduino 마이크로 USB 5V | |||

| ADC | 8비트 ADC1173 | 가속도계 및 자이로스코프 | 6축 LSM6DS3TR |

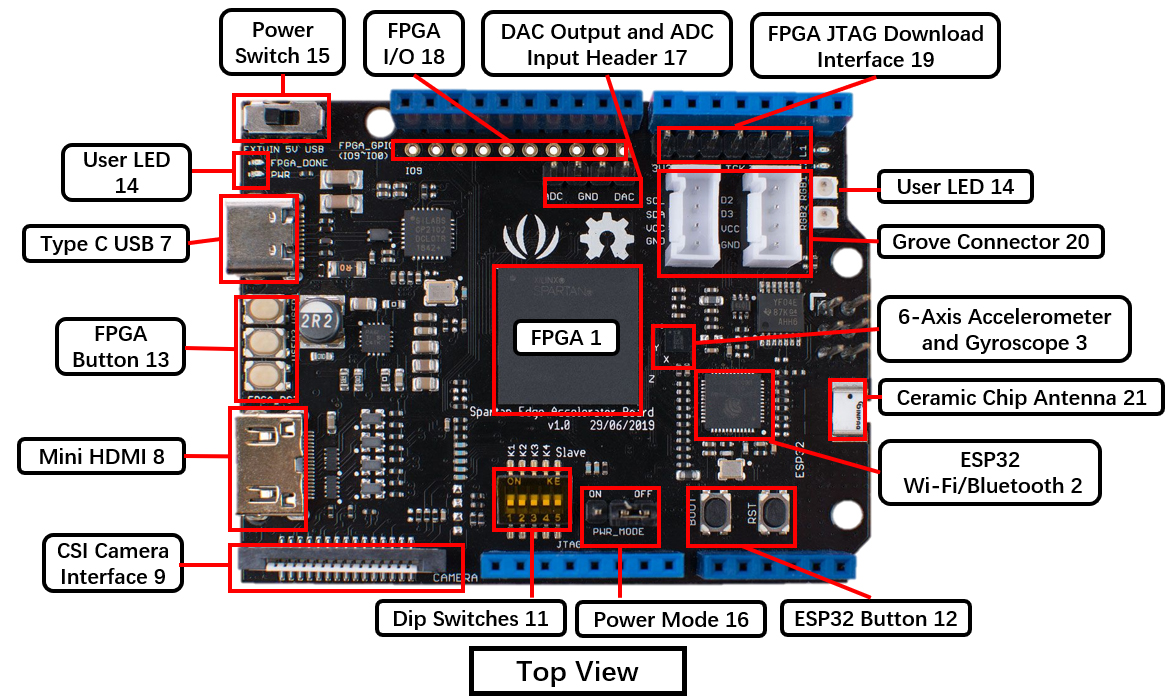

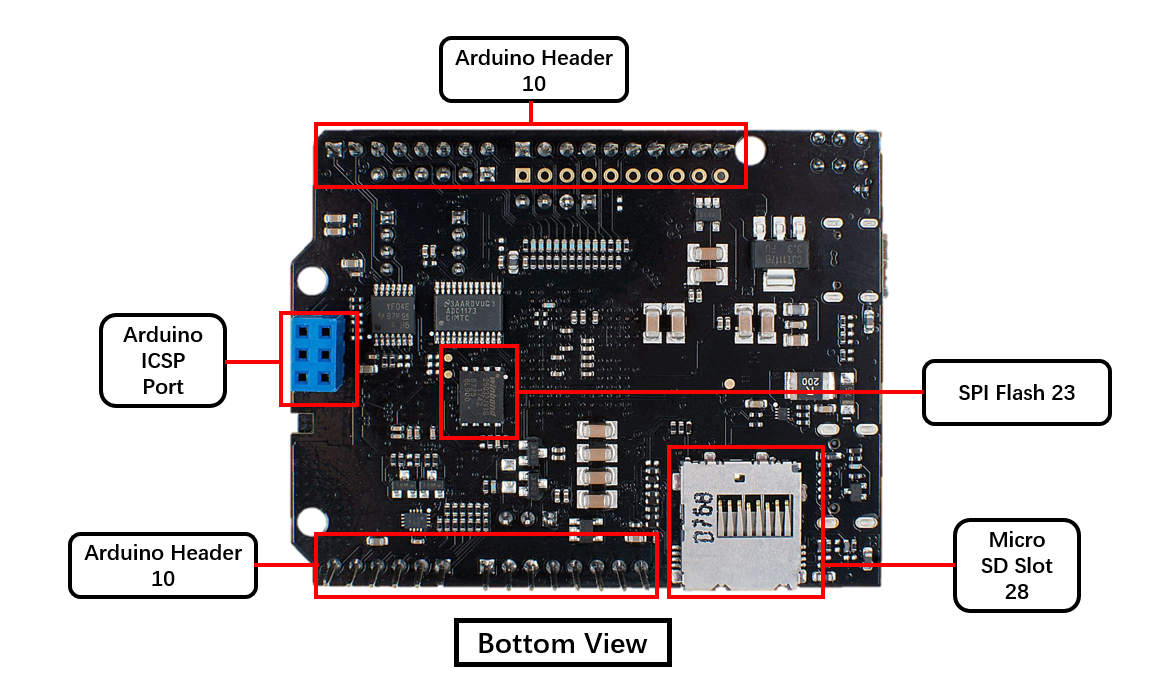

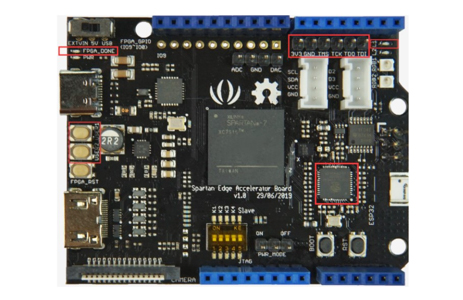

SEA 기판 주변 장치 설명 및 위치

| 1 | FPGA: XC7S15-1FTGB196C | 11 | 딥 스위치 | 19 | FPGA JTAG 다운로드 인터페이스 |

|---|---|---|---|---|---|

| 2 | WiFi/Bluetooth: ESP32-D0WDQ6 | K1-K4 사용자 스위치 | 20 | Grove 커넥터: 1x I2C; 1x D2&D3 | |

| K5 스위치 FPGA 프로그래밍 모드 | |||||

| 3 | 6축 가속도계 및 자이로스코프: LSM6DS3TR | ->>>> JTAG: Xilinx 공식 프로그래밍 도구 사용 | 21 | 세라믹 칩 안테나 | |

| ->>>> 슬레이브:ESP32를 사용하여 FPGA 프로그래밍 | |||||

| 4 | DAC: DAC7311IDCKR | 12 | ESP32 버튼: 부팅 및 RST | 22 | ADC: ADC1173 |

| 5 | 벅-DCDC: TPS62130 | 13 | FPGA 버튼: USER1 USER2 FPGA_RST | 23 | SPI 플래시: W25Q32JVZPIG |

| 6 | USB-UART: CP2102-GMR | 14 | 사용자 LED: L1/L2/RGB1/RGB2 | 24 | 아날로그 스위치: DG2788A |

| PWR: 전원 켜기 | |||||

| FPGA_DONE: esp32로 FPGA를 프로그래밍한 후 켜집니다. | |||||

| 7 | USB: Type-C | 15 | 전원 스위치: | 25 | LDO: XC6221B102MR |

| USB->USB Type C(5V DC)로 전원 공급 | |||||

| 5V->VIN 핀으로 전원 공급(8~17V DC) | |||||

| 8 | 미니 HDMI | 16 | 전원 모드: | 26 | LDO: RT9013-18GB |

| OFF->Arduino 및 Shield의 전원 공급 장치 분리 | |||||

| ON-> Arduino와 Shield의 전원 연결 | |||||

| 9 | CSI 인터페이스: MIPI 카메라(Raspberry Pi 카메라 V1 - OV5640과 호환) | 17 | DAC 출력 및 ADC 입력 헤더 | 27 | LDO: CJ1117-3V3 |

| 10 | Arduino 헤더: Arduino UNO와 호환 가능 | 18 | FPGA IO: IO9~IO0 | 28 | SD 카드 슬롯: 마이크로 SD/TF 카드 |

다음 설명서에서는 Xilinx의 Vivado 2019.2 소프트웨어를 사용하여 SEA 기판에서 FPGA를 설계하는 공정을 안내합니다.

Spartan 에지 가속 기판 개발 설명서 - FPGA 부품

Spartan 에지 가속 기판 개발 설명서 - 실험 파트

Spartan 에지 가속 기판 개발 설명서 - ESP32 부품

Yongming Tang 연구원, SID, IEEE, CVS(중국 진공 학회) 회원, 둥난 대학(Southeast University) 교사 교육 개발 센터 소장 그는 수년 동안 전자 과학 및 기술 과정을 가르치는 일에 종사해 왔으며 "디지털 빌딩 블록 만들기" 교과서 한 권을 편집하고 교과서 한 권을 번역했습니다. 둥난 대학(Southeast University) PLD 디자인 대회와 전국 대학생 FPGA 혁신 디자인 대회를 조직했습니다. 또한 국가 교육 공로 부문에서 2등상, 장쑤성에서 주관하는 교사 특별상 1번회, 1등상 1회, 2등상을 각각 수상했습니다.

Zhixiong Di 박사, Southwest Jiaotong University 정보 과학 및 기술 학교 전자 공학과 부학장 2014년 Xidian University에서 마이크로 일렉트로닉스, 반도체 전자공학 전공으로 졸업했습니다. 그의 연구 과제는 고성능 이미지 압축 VLSI 하드웨어 시스템 설계 및 디지털 집적 회로 레이아웃 알고리즘, FPGA 지능형 하드웨어 설계입니다. 여러 SCI/EI 논문을 발표했으며 10개 이상의 중국 발명 특허를 승인했습니다. 2020 CCF-DAC 컨퍼런스 하위 포럼의 의장을 역임했습니다. 그는 China Postgraduate Electronic Design Competition, China Postgraduate Innovation "Core" Competition 및 National Undergraduate FPGA Innovation Design Competition과 같은 분야의 심사위원을 역임했습니다.