타이밍 지터와 위상 잡음의 차이

더 빠르고 더 많은 데이터에 대한 요구가 계속적으로 증가함에 따라 직렬 데이터 전송 속도도 계속해서 높아지고 있습니다. 데이터 속도가 높아지면 타이밍 마진이 감소하기 때문에 설계자는 데이터 타이밍의 불확실성을 최소화해야 합니다. 데이터 타이밍의 불확실성을 지정하려면 분야에 따라 두 가지 형식 중 하나를 사용해야 합니다. 이 두 파라미터는 지터와 위상 잡음입니다.

위상 잡음과 지터 둘 모두는 신호의 타이밍 안정성을 나타내며 서로 관련되어 있습니다. 기본적으로, 이 두 파라미터를 통해 클록 또는 데이터 스트림의 타이밍 불확실성을 파악할 수 있습니다. 위상 잡음은 주파수 영역에서 신호 주파수의 불안정성을 나타낸 것이며, 지터는 시간 영역에서 신호 파형의 변화를 나타낸 것입니다.

영역의 선택은 응용 분야에 따라 달라집니다. RF 엔지니어는 보통 위상 잡음을 사용하고, 디지털 엔지니어는 지터를 사용하는 경우가 많습니다.

지터와 위상 잡음의 정의 및 측정

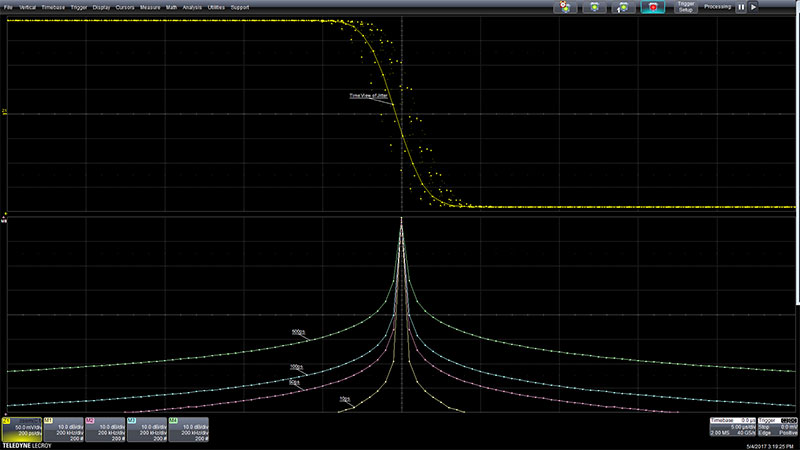

지터는 이상적인 값과 신호 타이밍의 차이이며 보통 오실로스코프로 측정됩니다. 지터는 에지 또는 위상 지터(시간 간격 오류), 기간 지터 또는 주기 간 지터(인접 주기 기간 사이의 차이) 등의 다양한 형식을 가질 수 있습니다. 모든 유형의 지터는 확률적 지터 또는 결정적 지터의 두 가지 성분으로 나눌 수 있습니다. 확률적 성분은 대개 무제한이기 때문에 피크 지터 값은 시간이 증가함에 따라 높아집니다. 결정적 지터 성분은 제한되어 있어 시간이 지나도 증가하지 않습니다. 이러한 주요 성분 각각은 이 기사에서 다루지 않는 여러 하위 성분을 결합합니다.

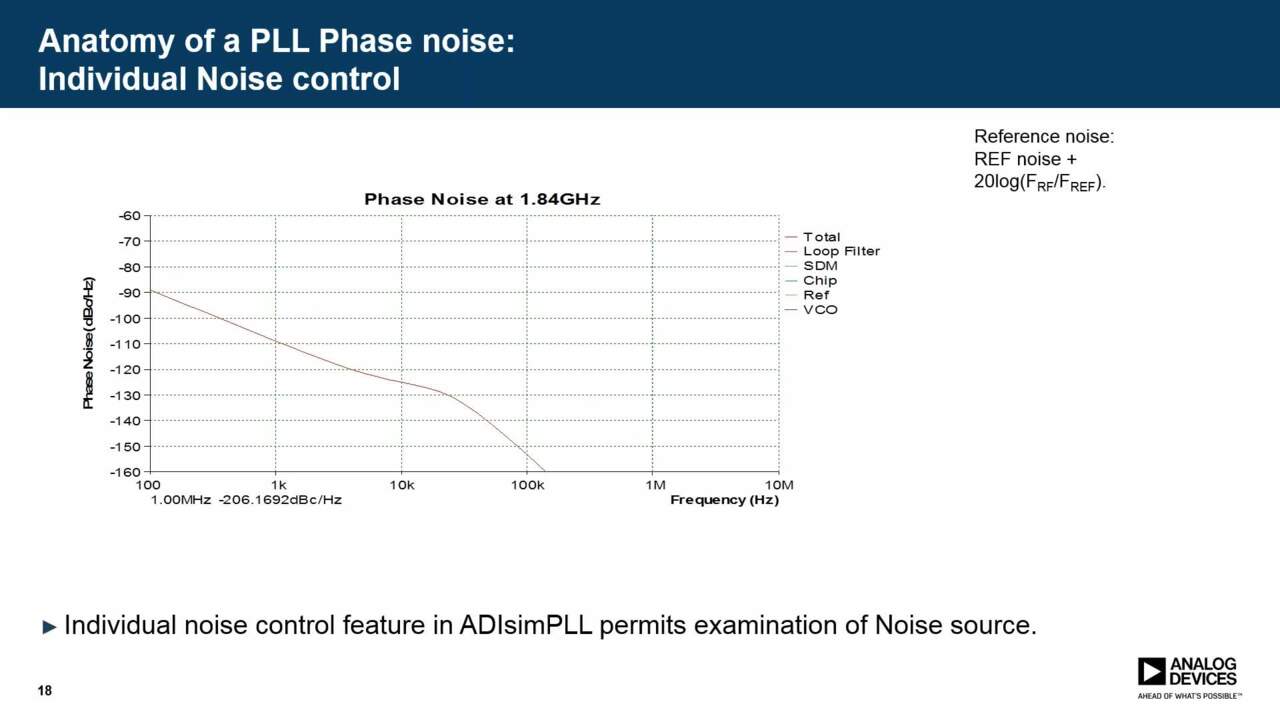

위상 잡음은 주파수 영역의 클록 기본파에 인접한 신호 전력을 고려합니다. 신호 위상 또는 주파수의 변동은 스펙트럼 라인의 너비로 나타납니다. 타이밍 불안정성이 클수록 스펙트럼 라인이 넓어집니다. 예시는 그림 1과 같습니다.

그림 1: 클록 신호의 지터(상단 트레이스)와 위상 잡음(하단 트레이스) 비교 (이미지 출처: DigiKey)

그림 1: 클록 신호의 지터(상단 트레이스)와 위상 잡음(하단 트레이스) 비교 (이미지 출처: DigiKey)

상단 트레이스는 100MHz 클록 신호의 에지를 보여줍니다. 디스플레이 잔상 효과가 켜진 상태로 표시되므로 에지 위치 내역을 알 수 있습니다. 클록 에지는 시간이 흐름에 따라 수평으로 이동합니다. 이 변동이 클록 에지 지터입니다. 이 경우, 피크 간 지터는 약 100ps입니다.

하단 트레이스는 출력 밀도 디스플레이를 사용하는 100MHz 클록 신호의 주파수 스펙트럼을 수평으로 확장하여 보여줍니다. 4개의 겹쳐진 스펙트럼을 통해 10ps, 50ps, 100ps, 500ps의 에지 지터 값에 대한 스펙트럼 너비의 차이를 보여줍니다. 지터가 증가함에 따라 스펙트럼 라인이 넓어집니다. 위상 잡음은 보통 스펙트럼 분석기 또는 전용 위상 잡음 테스트 세트를 사용하여 측정되며, 클록 기본파 주파수에서 고정 주파수 오프셋으로 나타납니다. 예를 들어 위상 잡음을 캐리어(dBc)의 10kHz 오프셋에서 캐리어에 비례하여 -96dB로 지정할 수 있습니다.

지터 및 위상 잡음 제어

설계자는 Analog Devices의 ADF4001BCPZ와 같이 위상 잡음이 낮은 클록 생성기를 사용하여 클록 분배 체인에서 지터와 위상 잡음을 제어할 수 있습니다. 이 장치는 200MHz 대역폭을 제공하며 클록 주파수로부터 1kHz 오프셋에서 일반적인 위상 잡음 사양은 -99dB/Hz입니다(그림 2).

그림 2: Analog Devices ADF4001BCPZ는 위상 잡음이 낮은 200MHz 클록 생성기로, 클록 주파수로부터 1kHz 오프셋에서 일반적인 위상 잡음 사양이 -99dB/Hz입니다. (이미지 출처: Analog Devices)

그림 2: Analog Devices ADF4001BCPZ는 위상 잡음이 낮은 200MHz 클록 생성기로, 클록 주파수로부터 1kHz 오프셋에서 일반적인 위상 잡음 사양이 -99dB/Hz입니다. (이미지 출처: Analog Devices)

클록을 여러 장치에 분배하려면 지로 지연 클록 버퍼가 필요합니다. 이러한 장치는 매우 낮은 타이밍 스큐를 보장하면서도 내장 PLL(위상 고정 루프) 때문에 지터도 낮아집니다. 예를 들어 Cypress Semiconductor의 CY2308SXC-3T 제로 지연 버퍼는 4개 출력을 가진 2개 뱅크가 있습니다. 이 장치는 10MHz ~ 133MHz의 주파수 범위에서 작동하며 출력에서 주기 간 지터는 60ps(통상)입니다(그림 3).

그림 3: 16-SOIC 패키지로 제공되는 제로 지연 Cypress Semiconductor CY2308SXC-3T 버퍼는 출력에서 주기 간 지터 60ps(통상)를 제공합니다. (이미지 출처 Cypress Semiconductor)

그림 3: 16-SOIC 패키지로 제공되는 제로 지연 Cypress Semiconductor CY2308SXC-3T 버퍼는 출력에서 주기 간 지터 60ps(통상)를 제공합니다. (이미지 출처 Cypress Semiconductor)

결론

따라서 처음 질문에 대한 답으로, 위상 잡음과 지터는 클록 또는 데이터 타이밍 안정성에 대한 동일한 정보를 다르게 나타낸 것입니다. 위상 잡음은 주파수 영역에, 지터는 시간 영역에 나타납니다. 적합한 부품을 선택하면 위상 잡음과 지터를 모두 줄일 수 있습니다.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum