전력 변환기 부동 시간이란 무엇이며 이를 제어하는 방법은 무엇입니까?

자동차, 소형 전기 자동차(EV), 무선 도구 및 충전소의 전력 요구 사항이 증가함에 따라 48V 전력 시스템으로의 전환이 가속화되고 있습니다. 이러한 시스템은 더 작은 크기와 무게뿐만 아니라 더 높은 효율성과 낮은 손실의 이점을 제공합니다. 이러한 모든 전력 시스템은 48V 버스에서 공급되는 전력을 사용 가능한 전압으로 변환하므로, 전력 변환기가 요구됩니다.

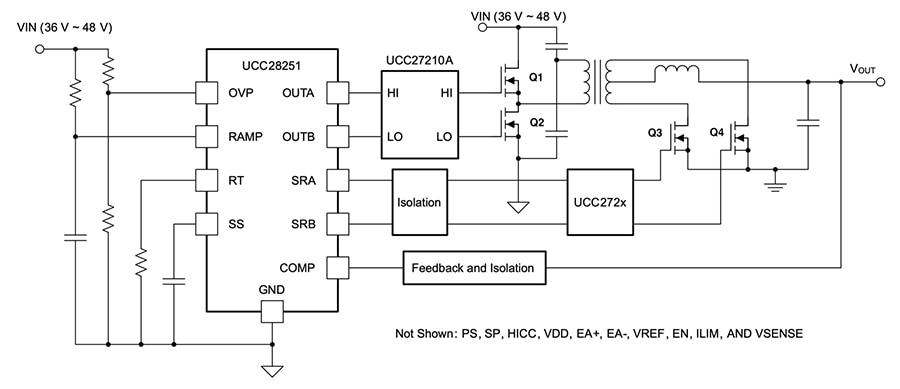

전력 변환기는 스위칭 전력 기술을 사용하여 48V DC를 선택된 전압으로 변환합니다. 이 경우 Texas Instruments의 UCC28251PWR인 일반적인 48볼트 컨버터는 그림 1에서 Q1 및 Q2로 표시된 전계 효과 트랜지스터(FET)와 같은 하프브리지 구성 전력 스위치 장치를 기반으로 합니다. 이 장치는 펄스 폭 변조(PWM) 컨트롤러에 의해 제어되어 원하는 출력 전압을 생성하고 조정합니다.

그림 1: 일반적인 DC-DC 컨버터는 PWM 컨트롤러를 사용하여 하프브리지 구성 전력 FET를 구동합니다. 컨트롤러는 FET 입력에서 펄스 폭을 조절하여, 요구되는 출력 전압(VOUT)을 생성하고 조정합니다. (이미지 출처: Texas Instruments)

그림 1: 일반적인 DC-DC 컨버터는 PWM 컨트롤러를 사용하여 하프브리지 구성 전력 FET를 구동합니다. 컨트롤러는 FET 입력에서 펄스 폭을 조절하여, 요구되는 출력 전압(VOUT)을 생성하고 조정합니다. (이미지 출처: Texas Instruments)

이 회로에서 FET Q1 및 Q2는 하프브리지 토폴로지를 형성합니다. 변압기를 구동하기 위해 교대로 켜집니다. FET Q3 및 Q4는 변압기 2차측의 스위칭 파형을 다시 DC로 변환하는 동기식 정류기입니다. 동기식 정류기는 반도체 정류기와 관련된 직렬 전압 강하를 제거하여 효율성을 향상시킵니다. 이러한 정류기 FET는 1차 전력 스위칭 장치와 동기적으로 구동되어야 합니다.

대체 인버터 토폴로지에는 4개의 FET를 사용하는 풀브리지 또는 'H' 브리지, 또는 3상 컨버터에 사용되는 6-FET 캐스케이드 풀브리지가 포함됩니다. 이러한 모든 기술은 한 쌍 이상의 전력 장치를 사용합니다. 쌍은 그림 1의 FET와 같이 직렬로 연결됩니다.

이러한 토폴로지에는 두 가지 중요한 문제가 있습니다. 첫 번째는 하이사이드(Q1)와 로우사이드(Q2)의 스위칭 장치가 동시에 켜지도록 허용될 수 없다는 것입니다. 그렇게 되면 48V 버스와 접지 간에 단락이 발생합니다. 이 상태를 슛스루라고 하며, 이는 일반적으로 전력 스위치의 손상을 초래합니다. 각 전력 장치의 스위칭 시간을 독립적으로 제어하면 슛스루가 방지됩니다. 목표는 비활성 장치가 켜지기 전에 활성 장치가 꺼지도록 하는 것입니다.

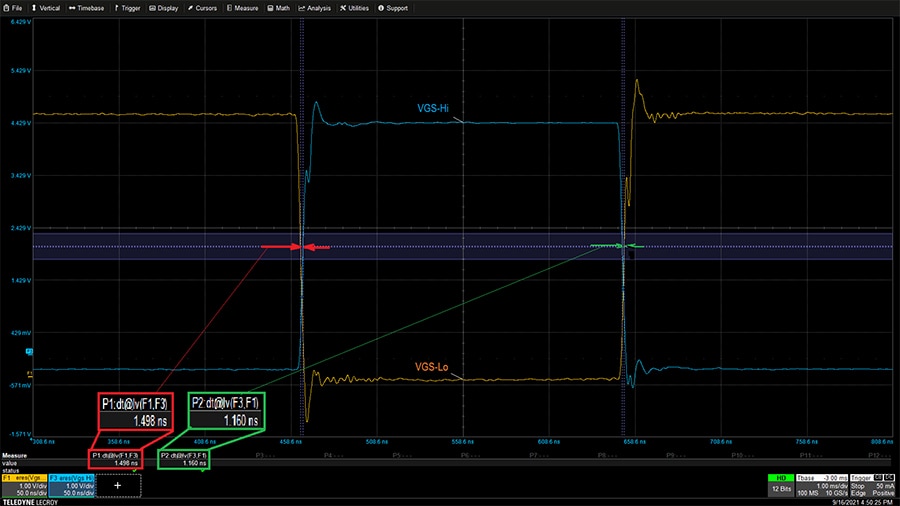

두 이벤트(켜기 및 끄기) 사이의 지연을 기본 부동 시간이라고 합니다. 이는 최대 컨트롤러 펄스 폭에서 하이사이드 및 로우사이드 FET의 게이트 소스 간 전압(VGS)의 전환 시간을 비교하여 측정됩니다(그림 2). 두 전환 설정 사이의 지연은 부동 시간입니다.

그림 2: 1차 부동 시간은 최대 컨트롤러 펄스 폭에서 하이사이드 및 로우사이드 FET의 VGS 전환 시간을 비교하여 측정됩니다. 두 전환 설정 사이의 지연은 부동 시간입니다. 이 예에서는 1.498ns와 1.166ns입니다. (이미지 출처: Art Pini)

그림 2: 1차 부동 시간은 최대 컨트롤러 펄스 폭에서 하이사이드 및 로우사이드 FET의 VGS 전환 시간을 비교하여 측정됩니다. 두 전환 설정 사이의 지연은 부동 시간입니다. 이 예에서는 1.498ns와 1.166ns입니다. (이미지 출처: Art Pini)

그림 2에서 로우사이드 FET(VGS LO)가 꺼지고 하이사이드 FET(VGSHi)가 켜질 때까지의 지연은 1.498ns입니다. 다른 조건은 하이사이드 FET가 꺼지고 로우사이드 FET가 켜질 때 1.166ns의 지연이 발생한 경우입니다. 측정된 지연이 모두 양수이면 부동 시간이 허용됩니다. 이 측정은 PWM 컨트롤러 출력의 최대 펄스 폭에서 이루어집니다.

부동 시간 동안 두 장치 모두 전도되지 않습니다. 이는 '부동 시간' 손실을 초래합니다. 모든 손실과 마찬가지로 부동 시간 손실을 최소화하는 것은 점점 더 중요한 문제입니다.

두 번째로 중요한 문제는 동기식 정류기의 작동을 1차 스위칭 작동과 조절하는 것입니다.

그림 1에 표시된 UCC28251PWR 컨트롤러는 하프브리지 또는 풀브리지 회로를 제어할 수 있으며 게이트 구동 신호와 동기식 정류기 출력에 프로그래밍 가능한 지연을 제공합니다. UCC28251PWR은 1차측 부동 시간을 제어하고 사이클 간 과전류 보호 기능도 포함합니다. 2차 부동 시간이라고 하는 1차 출력과 2차 동기식 정류기 구동 신호 사이의 지연은 2개의 외부 저항기를 통해 독립적으로 프로그래밍할 수 있습니다.

PWM 컨트롤러는 1차측 하프브리지 게이트 구동 IC인 Texas InstrumentsUCC27210DDAR과 함께 사용됩니다. IC는 하프브리지 구성에서 2개의 N 채널 FET의 게이트 소스 간 입력을 모두 구동합니다. 18ns(통상)인 고유한 전파 지연으로 인해 기본 부동 시간에 영향을 줍니다. 두 게이트 구동 출력 간의 지연을 일치시키면 전파 지연 문제가 최소화됩니다. UCC27210DDAR 게이트 구동기 IC는 2ns 이내로 일치하는 출력을 갖습니다. 동기식 정류기 FET를 구동하기 위해 유사한 타이밍 특성을 가진 동일한 제품군의 게이트 구동기가 사용됩니다.

결론

48V 시스템으로 전환하는 것은 효율성, 크기 및 무게 면에서 고유한 이점을 제공하지만, 설계자는 부동 시간의 원인과 이를 최소화하는 방법을 알아야 합니다. 그림과 같이 48V 전력 변환기의 작동을 보호하는 데 필요한 기능을 갖춘 특수 목적의 IC를 사용할 수 있습니다. 이는 1차 및 2차 부동 시간을 모두 제어하여 하프 및 풀브리지 회로 토폴로지에서 발생할 수 있는 주요 문제를 제거합니다.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum