I/O 전압 표준의 역할 - 마이크로 컨트롤러가 동일한 언어를 사용하도록 보장

내 모국어로 외국인과 소통을 시도하지만(그림 1), 상대방이 내 말을 이해하지 못할 뿐만 아니라 나는 '예'라고 말하는데 상대방의 언어로는 '아니오'를 의미한다면 어떠시겠어요? 이러한 상황이 바로, 호환되지 않는 I/O 표준을 가진 두 개의 집적 회로(IC)가 통신을 시도할 때 발생하는 현상입니다. 그 결과 혼란이 야기될 뿐 아니라 최악의 경우에는 하드웨어 손상이 발생하게 됩니다.

그림 1: '다양한 IO 표준 사용으로 인한 혼란'의 모습을 상징적으로 보여주는 AI 생성 이미지. (출처: AI 생성)

그림 1: '다양한 IO 표준 사용으로 인한 혼란'의 모습을 상징적으로 보여주는 AI 생성 이미지. (출처: AI 생성)

마이크로 컨트롤러는 0과 1로 구성된 이진 논리에서 작동합니다. 이 논리 레벨에 해당하는 전압 범위가 있습니다. 예를 들어, 어떤 마이크로 컨트롤러는 논리 '0'을 0.3V 이하로, 논리 '1'을 2.7V 초과하는 값에서 최대 3.3V까지로 인식할 수 있습니다. 하지만 다른 마이크로 컨트롤러는 논리 '1'을 1.2V에서 시작하여 최대 1.8V까지로 인식할 수 있습니다. 첫 번째 마이크로 컨트롤러가 두 번째 마이크로 컨트롤러에 3.3V 신호를 전송할 경우(그림 2), 이는 수신 장치의 전압 허용 오차 범위를 초과하여 영구적인 손상을 입힐 수 있습니다.

그림 2: 호환되지 않는 IO 표준을 갖춘 두 개의 IC가 통신하는 모습에 대한 설명 (출처: AI 생성)

그림 2: 호환되지 않는 IO 표준을 갖춘 두 개의 IC가 통신하는 모습에 대한 설명 (출처: AI 생성)

바로 이러한 이유때문에 임베디드 시스템 설계에서 I/O 전압 호환성을 이해하고 관리하는 것이 중요합니다. 적절한 레벨 조정 또는 전압 변환이 이루어지지 않으면, 두 칩 간의 단순한 연결조차도 예측 불가능한 동작이나 하드웨어 고장을 초래할 수 있습니다.

I/O 전압 표준의 역할

I/O 전압 표준은 디지털 논리 신호에 허용되는 전압 수준을 정의하며, 논리적 고(1) 또는 저(0)의 구성을 명시합니다. 이 표준은 장치가 신호를 정확히 해석하고 적절히 응답할 수 있도록 보장합니다. 이러한 수준에 대한 공통된 기준이 없으면, 장치들이 신호를 잘못 해석하거나 서로 통신하지 못할 수 있습니다.

표준에서 정의된 용어들은 다음과 같습니다.

- VIH(입력 고전압): 논리 고전압으로 인식되는 최소 전압.

- VIL(입력 저전압): 논리 저전압으로 인식되는 최대 전압.

- VOH(출력 고전압): 논리 고전압으로 출력되는 최소 출력 전압.

- VOL(출력 저전압): 논리 저전압으로 출력되는 최대 출력 전압.

성공적인 통신을 위해, 한 장치의 출력 수준은 수신 장치의 허용 가능한 입력 범위 내에 있어야 합니다.

단일 종단 IO 표준

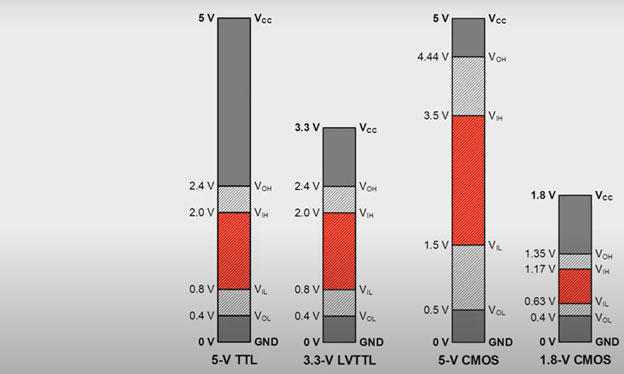

단일 종단 입력-출력(SIO) 표준(그림 3)은 가장 널리 사용되는 입력-출력(I/O) 표준 중 하나입니다. 신호 전송을 위해 공통 접지에 연결된 단일 전선을 사용합니다. 저속 및 저복잡도 설계의 경우, SIO가 두 개의 보완 신호를 사용하는 차동 신호 표준에 비해 비용 효율적이고 단순한 대안입니다.

저전압 상보형 금속 산화 반도체(LVCMOS)는 일반적인 단일 종단 표준으로, 일부 맥락에서는 LVMOS라고도 불립니다. LVCMOS는 일반적으로 1.8V, 2.4V 또는 3.3V에서 작동하며 논리 고전압 및 저전압에 대한 특정 임계값을 정의합니다. SIO 표준과 관련된 단순성으로 인한 단점도 존재합니다. LVCMOS와 같은 SIO는 장거리 또는 고주파에서 잡음과 신호 저하에 취약합니다. LVCMOS와 서로 다른 전압 도메인에서 작동하는 장치 간 인터페이싱 시 적절한 전압 호환성을 확보하기 위해 레벨 시프터를 사용하는 것은 매우 중요합니다.

그림 3: 다양한 IO 표준의 전압 수준. (출처: Texas Instruments)

그림 3: 다양한 IO 표준의 전압 수준. (출처: Texas Instruments)

I/O 인터페이스의 과제

1. 전압 불일치

서로 다른 전압 수준에서 작동하는 장치 간의 인터페이스에서 가장 흔한 문제는 전압 불일치입니다. 예를 들어, 레벨 조정 없이 3.3V 출력을 1.8V 입력에 연결하는 경우, 저전압 장치가 손상될 수 있습니다(그림 2).

이를 완화하기 위해서는 한 IC의 입력 고전압(VIH) 및 입력 저전압(VIL) 수준이 다른 IC의 출력 고전압(VOH) 및 출력 저전압(VOL) 수준과 일치해야만 합니다.

2. 신호 무결성

고속에서 반사, 링잉, 누화는 신호를 손상시킬 수 있습니다. 적절한 종단 처리, 임피던스 매칭, 트레이스 라우팅은 깨끗한 신호 전환을 유지하기 위해 필수적입니다.

3. 전원 공급 장치 도메인

다중 전압 레일이 있는 시스템에서는 도메인 간 신호를 격리하거나 변환하는 데 주의해야 합니다. 일반적인 솔루션으로는 레벨 시프터, 전압 분배기 또는 풀업 저항기를 갖춘 개방 드레인 구성을 활용하는 것입니다.

고급 논리 제품군: LVPECL, CML, VML, LVDS

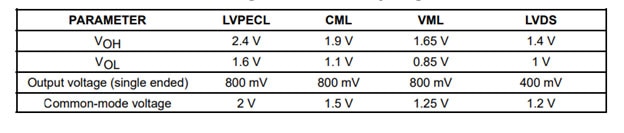

고속 통신 시스템에서는 LVPECL(저전압 양극 방출기 결합형 논리), CML(전류 모드 논리), VML(전압 모드 논리)와 같은 논리 제품군이 사용됩니다(표 1). 이러한 제품은 더 빠른 전환 속도와 우수한 잡음 내성을 제공하지만, 신중한 설계가 필요합니다.

- LVPECL: 3V 전압 범위에서 작동하며, 차동 신호 전송과 고속 성능을 갖추고 있습니다.

- CML: 고속 스위칭과 낮은 지터를 위해 정전류원을 사용합니다.

- VML: 덜 일반적이지만, 부하 독립적인 스윙으로 전압 모드 신호를 제공합니다.

- LVDS: 중간 속도의 저전력 차동 신호에 널리 사용됩니다.

표 1: 논리 레벨별 전압 파라미터(LVPECL, CML, VML, LVDS). (출처: Texas Instruments)

표 1: 논리 레벨별 전압 파라미터(LVPECL, CML, VML, LVDS). (출처: Texas Instruments)

I/O 인터페이싱을 위한 모범 사례

- 항상 규격서에서 VIH, VIL, VOH, VOL 값을 확인합니다.

- 전압 도메인 간 인터페이싱 시 레벨 시프터를 사용합니다.

- 오실로스코프와 논리 분석기를 사용하여 조기에 자주 테스트합니다.

I/O 인터페이싱은 단순히 핀을 연결하는 것에 지나지 않고, 각 신호가 의도한 대로 정확히 해석되도록 보장하는 것이 핵심입니다. 임베디드 시스템이 점점 더 복잡해지고 다양한 전압 도메인과 논리 패밀리에서 작동함에 따라, I/O 호환성에 대한 깊은 이해는 필수적인 사항이 되었습니다.

설계자는 전압 표준을 이해하고, 불일치를 예측하며, 모범 사례를 적용함으로써, 명확하게 통신하며 변환 오류 없이 작동하는 견고하고 신뢰로운 시스템을 설계할 수 있습니다. 그러나 서로 다른 I/O 표준을 가진 IC를 연결해야 하는 경우, 신호 레벨 불일치를 완화하는 한 가지 방법은 레벨 시프터를 사용하는 것입니다.

레벨 시프터

레벨 시프터(LS)(전압 변환기라고도 함)는 임베디드 시스템에서 서로 다른 전압 수준에서 작동하는 부품 간에 안전하게 인터페이싱하기 위해 사용되는 회로입니다. 3.3V로 작동하는 마이크로 컨트롤러가 1.8V 논리 회로로 작동하는 센서와 통신해야 할 경우, 레벨 시프터는 두 회로 간 신호가 정확히 변환되도록 보장하며, 손상이나 논리 오류의 위험 없이 통신을 가능하게 합니다. 사용되는 프로토콜에 따라 레벨 시프터는 단방향 또는 양방향으로 분류될 수 있습니다. LS는 일반적으로 MOSFET, 버퍼 IC 또는 전용 변환 칩을 사용하여 구현되며, 신호 무결성 유지와 혼합 전압 환경에서의 부품 보호에 필수적인 역할을 합니다.

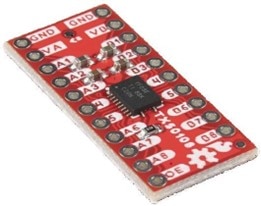

그림 4: 8채널 레벨 시프터 모듈. (출처: SparkFun)

그림 4: 8채널 레벨 시프터 모듈. (출처: SparkFun)

리소스

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum