공간 및 비용 절약을 위해 HyperBus를 사용하여 소형 IoT 및 웨어러블 설계의 메모리 확장

DigiKey 북미 편집자 제공

2018-08-01

IoT 노드와 웨어러블 장치의 크기가 작아짐에 따라 설계자는 기판 공간, 전력, 비용을 최소화하기 위해 마이크로 컨트롤러의 메모리 활용도를 극대화해야 합니다. 그러나 메모리 확장이 불가피한 경우가 있습니다. 이 경우 설계자는 32비트 컨트롤러의 버스 구조를 기본으로 설정하는 대신, 주소 및 데이터 모두에 대한 고속 333Mbit/s, 8비트, 이중 데이터 전송(DDR) 인터페이스인 HyperBus를 고려해야 합니다.

많은 설계자가 확장을 피하려고 하지만 개발 도중 메모리 요구 사항의 증가로 인해 종종 필요로 합니다. 또는 개발자가 미래의 확장 필요를 예측하여 미래 보장 설계를 간소화합니다.

16비트 데이터와 16비트 주소 버스 및 일반적인 32비트 인터페이스의 관련 제어 핀을 사용하는 것에 비해, HyperBus를 사용하면 마이크로 컨트롤러가 동일 버스에서 외부 플래시 및 RAM을 지원할 수 있습니다. 이는 HyperBus 인터페이스 포트가 있는 모든 메모리 장치에서 작동하며 공간 제한적 응용 제품에서 핀 수가 적은 메모리 확장을 위한 효율적이고 사용하기 쉬운 인터페이스입니다.

버스의 작동은 펌웨어를 통해 인식할 수 있지만 HyperBus가 처음인 개발자는 강력한 설계를 위해 고속 버스 신호의 작동에 익숙해져야 합니다. 이 기사에서는 먼저 HyperBus의 작동에 대해 설명합니다. 그런 다음 인터페이스가 통합된 마이크로 컨트롤러를 소개하며 이를 효율적으로 적용하고 설계를 테스트하는 방법을 안내합니다.

HyperBus 설명

앞서 언급한 것처럼 HyperBus는 주소 및 데이터 모두에 고속 8비트 DDR 인터페이스를 사용합니다. 또한 차동 클록, 읽기/쓰기 래치 신호, 각 메모리 장치별 칩 선택을 사용합니다. HyperBus는 동일 버스에서 외부 플래시 및 RAM을 지원하며 HyperBus 호환 주변 장치 인터페이스를 통해 모든 마이크로 컨트롤러와 연동됩니다.

HyperBus는 버스에서 하나의 호스트 마스터가 하나 이상의 슬레이브 메모리 장치에 접속되는 마스터/슬레이브 인터페이스로 설정됩니다. HyperBus 플래시 메모리 장치를 HyperFlash™라고 하며 HyperBus DRAM 메모리 장치를 HyperRAM™이라고 합니다.

버스는 신호 지정 CK 및 CK#을 사용하는 차동 클록을 사용합니다. HyperBus는 DDR 인터페이스이므로 데이터가 상승 및 하강 클록 에지 모두에서 전송됩니다. 클록은 마스터에 의해 구동되며, 그 주파수는 버스에서 가장 느린 HyperBus 메모리의 정격 클록 주파수를 초과할 수 없습니다.

양방향 8비트 버스는 DQ[0-7]로 지정되어 있으며 마스터 장치와 슬레이브 장치 간에 주소, 데이터 및 명령을 전송합니다. 양방향 읽기/쓰기 데이터 스트로브 신호인 지정된 RWDS는 데이터 래치에 사용됩니다. RWDS는 데이터를 읽는 장치에 의해 제어되므로, 마이크로 컨트롤러 호스트가 HyperRAM에 데이터를 쓰는 경우 HyperRAM이 RWDS 신호를 제어합니다. DQ[0-7]에서 읽어 오는 데이터는 클록의 두 가장자리에 맞춰 정렬됩니다.

각 슬레이브 장치는 Low 활성 칩 선택, 지정된 CS0#, CS1#, CS2# 등을 사용하여 선택됩니다. 한 번에 하나의 칩 선택만 활성화될 수 있습니다. 모든 버스 트랜잭션은 HIgh에서 Low로 전환되는 지정된 칩 선택으로 초기화됩니다. 모든 버스 트랜잭션은 Low에서 High로 전환되는 지정된 칩 선택으로 종료됩니다. 개발자는 언제든지 하나의 칩 선택만 활성화되도록 해야 합니다. 그렇지 않을 경우, 둘 이상의 HyperBus 슬레이브 장치가 RWDS를 동시에 구동하여 데이터 손상이 발생할 수 있습니다.

Low 활성 하드웨어 리셋 신호인 지정된 RESET#은 마스터에 의해 구동됩니다. Low로 풀링되면 신호에 연결된 모든 외부 HyperBus 메모리 장치의 상태를 리셋합니다. 여기에는 메모리 장치의 내부 구성 레지스터 리셋이 포함됩니다. 그러나 HyperBus 메모리 장치의 내부 메모리 상태에는 영향을 미치지 않습니다. 대부분의 HyperBus 마스터 마이크로 컨트롤러 인터페이스에서 RESET#은 HyperBus 주변 장치의 일부가 아니라 일반 I/O 핀입니다. HyperBus 슬레이브 장치에는 RESET# 핀에 취약 풀업이 있으므로 부동 상태로 두면 High 상태로 풀링됩니다.

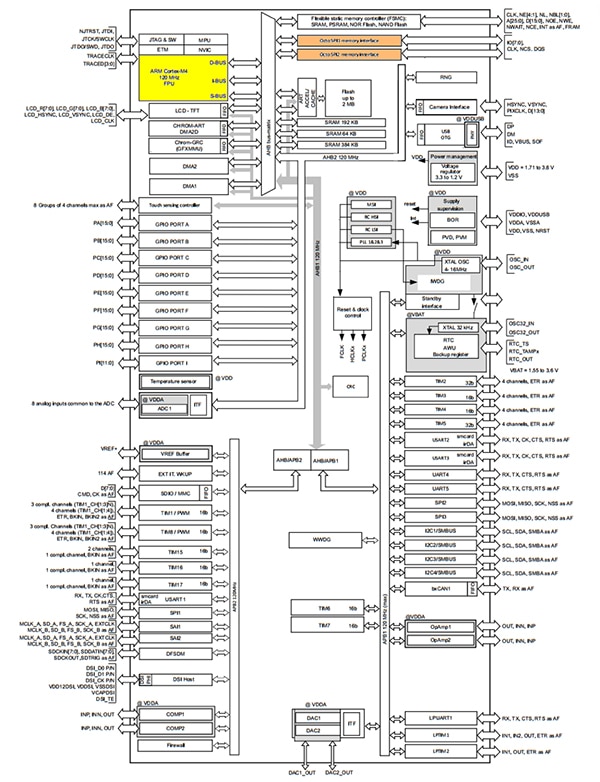

마이크로 컨트롤러의 모든 HyperBus 호환 주변 장치는 HyperBus 사양을 준수해야 합니다. HyperBus 호환 마이크로 컨트롤러의 좋은 예로 STM32L4R9 Arm® Cortex®-M4F(STMicroelectronics)(그림 1)를 들 수 있습니다. STM32L4R9에는 2Mbyte의 내부 플래시 메모리와 640Kbyte의 SRAM이 있습니다. 또한 HyperBus 인터페이스로 구성 가능한 두 개의 OctoSPI 인터페이스를 포함하여 다양한 주변 장치가 있습니다.

그림 1: STMicroelectronics STM32F4L9 마이크로 컨트롤러는 FPU를 갖춘 Arm® Cortex®-M4 코어를 기반으로 하며 두 개의 HyperBus 호환 인터페이스가 포함되어 있습니다(이 그림에서 주황색으로 강조 표시되어 있음). (이미지 출처:STMicroelectronics)

STM32L4R9는 메모리가 마이크로 컨트롤러의 AHB 버스 주소 공간에 매핑될 때 HyperBus 외부 메모리 주소에 액세스하므로 외부 메모리 읽기 및 쓰기는 내부 메모리와 동일한 방법으로 코어에 의해 액세스됩니다. 외부 메모리 장치가 구성되면 HyperBus의 작동이 코어를 통해 인식됩니다.

HyperBus 메모리는 모두 16비트 폭 메모리이므로 STM32L4R9로부터의 모든 액세스는 16비트 메모리 경계에 있어야 합니다. STM32L4R9 마스터로부터의 데이터 액세스는 16비트 또는 32비트일 수 있으며 마찬가지로 정렬된 경계에 있어야 합니다.

HyperBus에서의 일반적인 읽기 또는 쓰기 트랜잭션은 두 개의 8비트 폭, 1/2클록 주기 데이터 전송(각 단일 엔드 클록 에지에서 하나 또는 차동 클록 교차에서 하나)을 통해 일련의 순차적인 16비트, 1클록 주기 데이터 전송으로 구성됩니다. 읽기 및 쓰기 트랜잭션은 항상 전체 16비트 워드의 데이터를 전송합니다. 읽기 데이터 워드는 항상 두 개의 유효 바이트를 포함합니다. 쓰기 데이터 워드는 쓰기 버스트 내에서 개별 바이트 쓰기를 방지하도록 마스크된 1바이트 또는 2바이트를 포함할 수 있습니다. 바이트 전송은 HyperBus 프로토콜에서 지원되지 않으며 비트 밴딩과 같은 비트 연산도 지원되지 않습니다.

STM32L4R9의 각 HyperBus 호환 포트에는 전용 256Mbyte의 메모리 매핑된 주소 공간이 있으며, 다음과 같이 매핑됩니다.

HyperBus1(OctoSPI1) 0x90000000 - 0x9FFFFFFF

HyperBus2(OctoSPI2) 0x70000000 - 0x7FFFFFFF

액세스되는 HyperFlash 또는 HyperRAM 메모리 장치의 내부 주소는 위 위치의 기본 메모리 주소에서 오프셋됩니다. 예를 들어 STM32F4L9가 메모리 위치 0x90000047에서 읽는 경우, 메모리 위치 0x0047의 HyperBus1에서 액세스되는 메모리 장치에 저장된 값을 다시 읽습니다.

Cypress Semiconductor는 HyperBus 사양을 개발했으며 HyperBus 메모리 제품 라인도 공급하고 있습니다. Cypress S26KS512SDPBHI020 64MB x 8 HyperFlash 메모리는 OctoSPI 포트 중 하나에 손쉽게 접속할 수 있습니다. 이 장치는 최대 32개 16비트 워드의 래핑된 버스트 액세스를 지원합니다. 최대 166.6MHz 클록 속도를 가지는 S26KS512 HyperFlash는 333Mbyte/s의 지속적 읽기 속도를 지원합니다. OctoSPI 최대 클록 60MHz에서 STM32L4R9는 최대 120Mbyte/s로 외부 HyperBus 메모리를 읽을 수 있습니다.

STM32L4R9는 Cortex-M4 시스템 버스를 통해 HyperFlash에 액세스하는 경우 이 플래시 메모리에서 직접 코드를 실행할 수 있습니다. 코드 메모리에 사용되는 경우 OctoSPI는 외부 메모리에서 다음 메모리 주소를 로드하는 통합 선인출 버퍼를 사용하는 XIP(eXecute In Place)를 지원합니다.

Cypress Semiconductor S27KS0641DPBHI020 8MB x 8 HyperRAM 메모리는 STM32L4R9 데이터 메모리를 확장할 수 있는 자가 리프레시 DRAM입니다. 최대 64개 16비트 워드의 래핑된 버스트 주소를 지원합니다. 또한 S27KS0641 HyperRAM은 최대 333Mbyte/s의 지속적 읽기 속도를 지원하며 STM32L4R9에서 최대 120Mbyte/s로 읽을 수 있습니다.

HyperBus 메모리에 인터페이싱

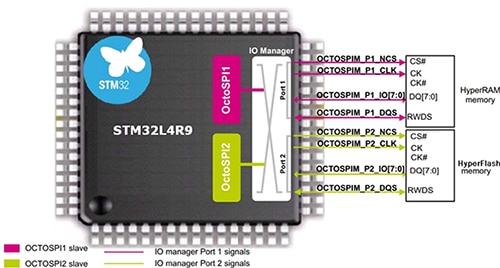

STM32L4R9에는 두 개의 HyperBus 호환 포트가 있으며 각각 HyperRAM 및 HyperFlash 외부 메모리 장치에 독립적으로 접속할 수 있습니다(그림 2). RESET# 신호는 선택적이므로 그림에 표시되지 않았습니다. Cypress HyperFlash와 HyperRAM을 통해 STM32L4R9는 PC 기판 크기와 설계 복잡성에 미치는 영향을 최소화하면서 내부 메모리를 쉽게 확장할 수 있습니다.

그림 2: STM32L4R9에는 두 개의 HyperBus 호환 포트가 있으며 각각 HyperRAM 및 HyperFlash 외부 메모리 장치에 독립적으로 접속할 수 있습니다. (이미지 출처: STMicroelectronics)

레이아웃에 가장 중요한 신호는 DQ[0-7] 및 RWDS입니다. 최적의 성능을 위해 이러한 신호는 PC 기판에서 마이크로 컨트롤러와 메모리 간에 길이가 가능한 짧아야 합니다.

차동 클록 신호 CK 및 CK#은 신호의 길이 동안 서로 간에 일정한 간격을 유지하면서 나란히 배치되어야 합니다. 가능한 경우, EMI를 최소화하기 위해 VSS 가드 트레이스로 CK 및 CK#을 보호합니다. 임피던스 불일치를 최소화하려면 PC 기판의 맨 위 계층에서 모든 신호를 분할해야 하며 그 아래 단일 VSS 계층이 있어야 합니다.

HyperBus를 처음 사용하는 개발자의 경우 프로브 테스트 포인트를 추가하는 것이 좋습니다. DQ[0-7] 및 RWDS의 경우 테스트 포인트가 STM32L4R9 마이크로 컨트롤러와 메모리 장치 모두에 있어야 합니다. STM32L4R9가 쓰는 중에는 메모리 장치에 가장 가까운 테스트 포인트를 관찰하는 것이 좋습니다. STM32L4R9가 읽는 중에는 STM32L4R9에 가장 가까운 테스트 포인트를 확인합니다. CK, CK#, CS의 경우에는 메모리 장치에 더 가까운 테스트 포인트를 사용합니다.

DDR 인터페이스의 경우 클록 주파수가 높기 때문에 STM32L4R9 및 메모리 장치에 대한 전압 공급이 가능한 정확해야 합니다. 잡음이 있으면 신호 타이밍에 영향을 미치며 버스 전송 오류가 발생할 수 있으므로 감결합 커패시터를 사용하는 것이 좋습니다. HyperBus 메모리 장치에는 I/O 핀을 위한 별도의 전원 및 접지가 있으며 맨 위 또는 맨 아래 계층의 1µF 및 0.1µF 커패시터를 I/O 전력 VCCQ에 추가해야 합니다.

HyperBus에 대한 펌웨어 액세스

HyperBus 메모리 장치에는 장치에 대한 옵션 및 타이밍을 설정하는 데 사용되는 온칩 레지스터가 있습니다. HyperBus에서는 이를 구성 레지스터(CR)라고 합니다. 모든 HyperRAM 장치에는 특정 동작 특성을 설정할 수 있도록 하는 내부 CR이 있습니다. HyperRAM S27KS0641의 경우 펌웨어는 저전력 모드, 래핑 버스트 길이, 래핑 버스트 유형, R/W 타이밍 파라미터, 외부 8비트 데이터 버스의 출력 구동력을 구성할 수 있습니다.

HyperFlash에는 CR이 아니라 상태 레지스터가 있습니다.. S26KS512 HyperFlash에는 세 개의 상태 레지스터가 있습니다. 이 장치는 쓰기 작업 검증을 위해 내부 오류 수정 코드(ECC)를 지원하며 쓰기 오류를 나타내기 위한 ECC 상태 레지스터가 있습니다. 또 다른 레지스터에는 ECC 오류의 주소가 포함됩니다. 세 번째 레지스터는 ECC 수정 개수와 수정 불가 오류 개수를 셉니다. 이러한 모든 레지스터는 읽기 전용입니다.

HyperBus 트랜잭션은 두 가지 유형의 메모리 작업을 지원합니다. 첫 번째는 외부 메모리 읽기 또는 외부 메모리에 쓰기입니다. 두 번째는 CR 읽기나 CR에 쓰기 또는 상태 레지스터 읽기입니다.

STM32L4L9 OctoSPI가 HyperBus 포트로 구성되면 코어는 다른 모든 메모리 매핑 위치처럼 메모리에 액세스할 수 있습니다. 메모리 매핑 HyperBus 공간의 모든 읽기 또는 쓰기 작업은 마이크로 컨트롤러와 외부 메모리 간의 트랜잭션을 초기화합니다. 각 HyperBus 트랜잭션은 마이크로 컨트롤러에서 명령/주소 명령어가 포함된 세 개의 16비트 워드를 외부 메모리 장치로 보내는 작업으로 시작합니다. 명령/주소 시퀀스는 외부 메모리 장치에 읽기 작업인지 쓰기 작업인지 여부, 메모리 공간 또는 구성 레지스터가 주소 지정되는지 여부, 트랜잭션이 래핑되었는지 아니면 선형 버스트 트랜잭션인지 여부를 알리며 대상 주소 행 및 열을 제공합니다. 이 모든 작업은 작동 펌웨어를 통해 마이크로 컨트롤러에서 인식되지만 명령/주소 시퀀스는 디버깅 시 중요합니다.

HyperBus 시작

개발자가 HyperBus 프로토콜을 이해한 후에는 특히 개발자가 인터페이스를 처음 사용하는 경우 평가 기판을 사용하여 프로그래밍 실습을 몇 차례 수행해 보는 것이 좋습니다. STM32L4R9 마이크로 컨트롤러용 STMicroelectronics STM32L4R9I-EVAL 평가 기판은 좋은 시작점입니다(그림 3). HyperRAM 메모리 장치는 빨간색 원으로 표시되어 있으며 장치의 테스트 포인트는 오른쪽 헤더 커넥터에 있습니다.

그림 3: STMicroelectronics STM32L4R9I-EVAL은 STM32L4R9 마이크로 컨트롤러의 평가에 사용됩니다. HyperRAM 메모리 장치는 빨간색 원으로 표시되어 있으며 장치의 테스트 포인트는 오른쪽 헤더 커넥터에 있습니다. (이미지 출처: STMicroelectronics)

STM32L4R9I-EVAL은 카메라 인터페이스, 2개의 MEMS 마이크, 조이스틱, 4.3인치 480 x 272 픽셀 컬러 TFT LCD 디스플레이를 포함한 다양한 특징을 제공합니다. 평가 기판은 OctoSPI 인터페이스를 지원하며 ISSI의 IS66WVH8M8BLL 64Mbit HyperRAM 장치가 PC 기판에 납땜되어 있습니다.

결론

HyperBus 프로토콜은 공간이 중요한 응용 분야의 적은 핀 수 메모리 확장에 적절한, 사용이 간편한 인터페이스입니다. 버스의 작동은 펌웨어를 통해 인식되지만 HyperBus를 처음 사용하는 개발자의 경우 견고한 설계를 위해 고속 버스 신호의 작동에 익숙해져야 합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.