강유전체 메모리를 사용하여 자동차 응용 분야의 신뢰성 향상

DigiKey 북미 편집자 제공

2019-06-28

비휘발성 메모리(NVM)는 거의 모든 내장형 시스템 설계에서 중요한 역할을 하는 반면, 대부분의 설계에서는 데이터 쓰기와 액세스 속도, 데이터 보존, 저전력의 측면에서 비휘발성 메모리 관련 요구 사항이 점점 더 엄격해지고 있습니다. 이러한 현상은 설계자가 기능상 중요한 고급 운전자 지원 시스템(ADAS)과 같은 고급 기능을 구축하려고 모색하는 자동차 응용 분야에서 증가하고 있습니다.

안전하고 신뢰할 수 있는 시스템 작동을 보장하기 위해 설계자는 현재의 NVM 솔루션보다 더 빠르고 신뢰성이 높으면서 전력 소비가 적은 저전력 차량용 NVM 옵션으로 고급 강유전체 RAM(F-RAM)을 자세히 살펴보아야 합니다.

이 기사에서는 F-RAM 기술의 주요 특성을 설명하고 개발자가 Cypress Semiconductor의 두 F-RAM 솔루션을 사용하여 ADAS의 신뢰성을 개선하고, 다른 핵심 응용 분야에서 ADAS를 F-RAM용 프록시로 사용하는 방법을 살펴봅니다.

자동차 NVM 요구 사항

자동차 안전 응용 분야는 더 빠른 업데이트 속도와 더 높은 분해능을 가진 고급 센서를 통합하는 업계의 경향이 단적으로 드러납니다. ADAS, 전자 제어 장치(ECU), 이벤트 데이터 레코더(EDR) 등 자동차 서브 시스템은 광범위한 센서로부터 수집되는 세부 데이터 풀을 활용하여 지속적으로 진화하고 있습니다. 데이터가 손실되거나 데이터 액세스 속도가 느려지면 시스템 안전이 저해되거나, 차량 및 승객이 위험해질 수 있습니다.

예를 들어, ADAS 설계에서 전기적 지우기 및 프로그래밍이 가능한 읽기 전용 메모리(EEPROM)에 쓰는 데 필요한 시간으로 인해 감지된 위험을 방지하도록 설계된 자동 조종 장치에서 재난적인 지연 현상이 발생할 수 있습니다. EDR 설계에서는 쓰기 성능이 느릴 경우 차량 사고 시 전원이 차단되면 중요한 센서 데이터가 손실되어 사고의 근본 원인을 파악하는 데 필요한 데이터가 제거될 수 있습니다.

F-RAM NVM 특성

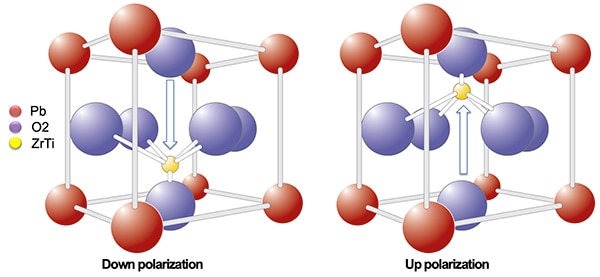

F-RAM 기술로 구축된 메모리 장치는 안정적인 데이터 저장 및 고속 액세스에 대한 증가하는 수요 및 성능 요구 사항을 충족하는 효과적인 NVM 대안이 될 수 있습니다. 장치는 티탄산 지르콘산 납(Pb[ZrxTi1−x]O3) 즉, PZT로 제조됩니다. PZT는 PZT 수정에 내장된 금속 공공(양이온)이 인가된 전계의 방향에 따라 위쪽 또는 아래쪽으로 두 가능한 분극 상태 중 하나에 도달하는 고유한 특성이 있습니다(그림 1).

그림 1: F-RAM 기술은 전계 인가 시 PZT 소재로 표현되는 두 개의 균등하게 안정된 상태를 활용합니다. (이미지 출처: Cypress Semiconductor)

그림 1: F-RAM 기술은 전계 인가 시 PZT 소재로 표현되는 두 개의 균등하게 안정된 상태를 활용합니다. (이미지 출처: Cypress Semiconductor)

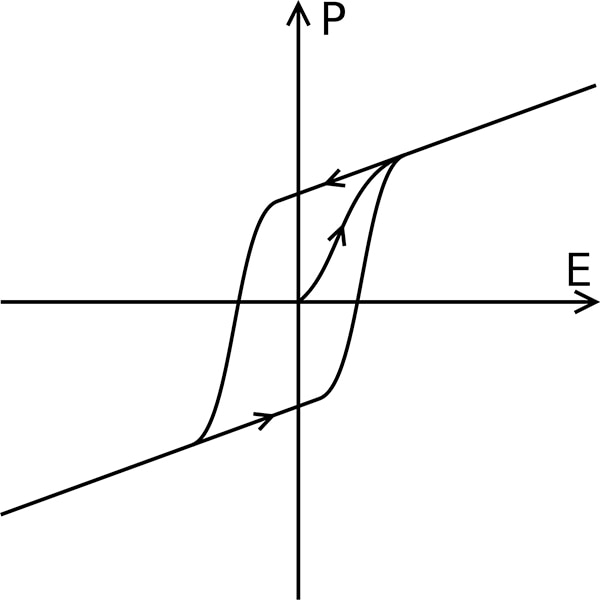

두 상태가 모두 동일한 저에너지 상태이므로 전계가 제거되면 양이온이 최근 분극 상태로 고정됩니다(그림 2). 양전계 또는 음전계 인가 시, 양이온은 강자성 소재에서와 비슷한 특성 히스테리시스 루프에 따라 적절한 분극 상태로 빠르게 다시 전환됩니다.

그림 2: PZT 소재는 인가된 전계에 응답하여 안정적인 두 분극 상태 간에 전환될 때 특유의 히스테리시스 루프를 따릅니다. (이미지 출처: WikiMedia Commons/ CC-BY-SA-3.0)

그림 2: PZT 소재는 인가된 전계에 응답하여 안정적인 두 분극 상태 간에 전환될 때 특유의 히스테리시스 루프를 따릅니다. (이미지 출처: WikiMedia Commons/ CC-BY-SA-3.0)

F-RAM 기술의 특징은 이 기술로 제조되는 NVM 장치에 다양하고 직접적인 이점으로 전환됩니다. 두 PZT 에너지 상태는 모두 균등하게 안정적이므로 양이온이 수십 또는 수백 년 동안 마지막 위치에서 유지되어 PZT 기반 F-RAM NVM 장치에서 전례 없는 데이터 보존율을 나타냅니다. 또한 이 기술은 다른 NVM 기술의 전하 저장 메커니즘 대신 양이온 위치를 기반으로 하므로 F-RAM 장치는 본질적으로 방사선에 대한 내성이 있고 전리 방사선의 단일 이벤트 업셋의 영향을 받지 않습니다.

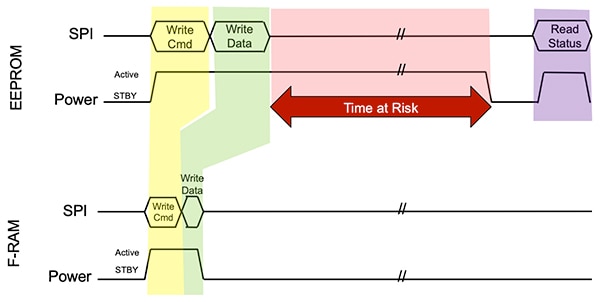

장기 저장 이점 이외에도 F-RAM 기술은 NVM 장치의 작동 성능을 개선합니다. 상태 전환이 매우 빠르고 적은 에너지를 사용하므로 핵심 응용 분야에서 EEPROM 또는 플래시 메모리를 사용할 경우의 기본적인 제한 사항을 극복할 수 있습니다. EEPROM 및 플래시 장치는 상대적으로 느린 쓰기 주기 중 데이터 버퍼링과 관련한 많은 “예비 시간”이 필요합니다. 쓰기 주기에서 이 추가 지연으로 인해 최종 읽기 상태 확인을 통해 작업을 완료하기 전에 전원이 차단될 경우 일정 기간 데이터가 위험에 처하고 완전히 손실될 수 있습니다(그림 3).

그림 3: EEPROM 또는 플래시 쓰기 작업 중에 확장된 예비 시간(빨간색 강조 표시)이 필요하므로 F-RAM 장치에 비해 오랫동안 데이터가 위험한 상태로 유지됩니다. (이미지 출처: Cypress Semiconductor)

그림 3: EEPROM 또는 플래시 쓰기 작업 중에 확장된 예비 시간(빨간색 강조 표시)이 필요하므로 F-RAM 장치에 비해 오랫동안 데이터가 위험한 상태로 유지됩니다. (이미지 출처: Cypress Semiconductor)

EEPROM 또는 플래시 메모리의 느린 쓰기 주기를 고려하여 전원 차단 효과를 완화하려는 개발자는 쓰기 작업을 완료하는 동안 NVM 공급 전압을 유지할 수 있는 적절한 전압 조정기와 함께 대용량 커패시터 또는 배터리를 추가해야 했습니다. 반대로 Cypress Semiconductor의 Excelon-Auto 장치와 같은 F-RAM은 쓰기 작업 중에 버스 속도로 작동하여 중요 데이터의 손실을 크게 줄이고 설계 시 보조 전원이 필요하지 않습니다.

차량용 F-RAM 장치

직렬 EEPROM 및 직렬 플래시 메모리와 기능적으로 유사한 Excelon™-Auto F-RAM 장치는 안정적인 고성능 NVM에 대한 핵심 응용 분야 요구 사항을 충족하도록 고안되었습니다. 자동차 시스템 설계자는 이러한 AEC-Q100 인증 장치를 사용하여 다른 메모리 유형을 대체할 수 있습니다. 예를 들어, 1.71V ~ 1.89V 공급 장치의 경우 CY15V102QN을 선택하고 1.8V ~ 3.6V 공급 장치의 경우 CY15B102QN을 선택할 수 있습니다. 둘 모두 2Mbit 장치이며, 논리적으로 256Kbits x 8로 구성됩니다.

-40°C ~ +125°C 작동 온도 범위 전반에서 Excelon F-RAM은 다른 NVM 기술보다 우수한 데이터 보존율을 나타냅니다. 예를 들어, CY15x102QN은 85°C에서 작동하면서 약 121년 동안 데이터를 유지할 수 있습니다. 데이터 보존은 온도에 반비례하므로 일반 엔진 온도의 상한(예: 95°C)에서 작동할 경우 F-RAM의 데이터 보존율은 약 35년입니다.

신뢰성과 관련하여 F-RAM의 읽기/쓰기 주기 내구성은 1013이며, 이는 일반 EEPROM 또는 플래시 메모리보다 약 7배 더 큽니다. 따라서 이러한 F-RAM 장치를 사용하는 개발자는 다른 NVM 기술과 연관된 제한된 쓰기 주기를 고려하여 섹터 전반에 쓰기를 분산하는 웨어 레벨링과 같은 기술을 구현할 필요가 없습니다.

F-RAM을 통해 설계 간소화

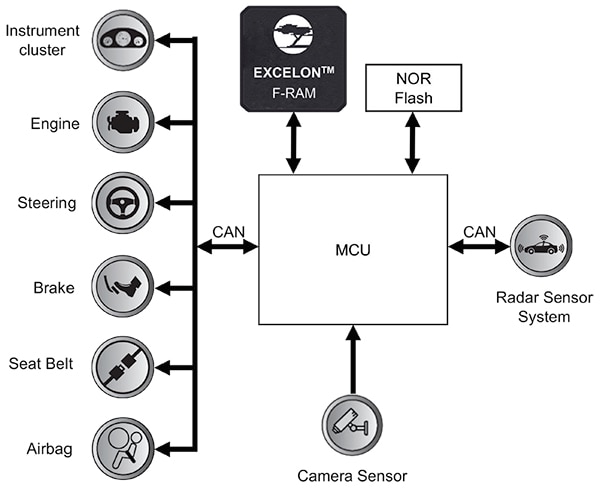

일반적인 설계에서 개발자는 이러한 장치를 사용하여 NOR 플래시와 같은 다른 유형의 NVM 장치를 직접 대체하거나 보완할 수 있습니다. 예를 들어 ADAS 설계에서 개발자는 펌웨어를 저장하는 데 사용되는 NOR 플래시를 ADAS 응용 분야에 입력을 제공하는 다양한 자동차 서브 시스템에서 여러 데이터 스트림을 안정적으로 처리할 수 있는 Excelon F-RAM과 결합할 수 있습니다(그림 4).

그림 4: 자동차 ADAS 개발자는 중요 데이터를 저장하는 Excelon F-RAM 장치를 마이크로 컨트롤러(MCU) 기반 설계에서 펌웨어 또는 구성 데이터를 저장하는 데 일반적으로 사용되는 NOR 플래시 장치와 결합할 수 있습니다. (이미지 출처: Cypress Semiconductor)

그림 4: 자동차 ADAS 개발자는 중요 데이터를 저장하는 Excelon F-RAM 장치를 마이크로 컨트롤러(MCU) 기반 설계에서 펌웨어 또는 구성 데이터를 저장하는 데 일반적으로 사용되는 NOR 플래시 장치와 결합할 수 있습니다. (이미지 출처: Cypress Semiconductor)

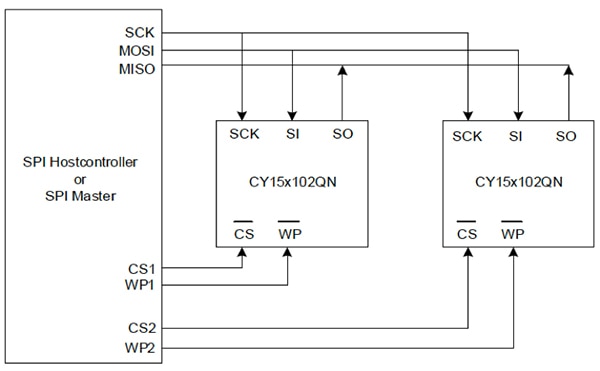

개발자는 Excelon F-RAM을 호스트 프로세서의 직렬 주변 장치 인터페이스(SPI) 버스에 간단히 연결하여 설계에 쉽게 적용할 수 있습니다. SPI 슬레이브 장치로 작동하도록 고안된 CY15x102QN F-RAM은 최대 50MHz의 SPI 클록 속도를 지원할 수 있습니다. 일반 하드웨어 구성에서 개발자는 F-RAM의 직렬 입력(SI) 및 직렬 출력(SO)을 SPI 마스터의 MOSI(Master Out Slave In) 및 MISO(Master In Slave Out) 라인에 각각 연결합니다. 해당 직렬 클록(SCK) 및 칩 선택(/CS) 라인에 연결하면 하드웨어 인터페이스가 완료됩니다. 개발자는 여러 장치를 결합하여 호스트의 SPI 버스를 공유할 수 있습니다(그림 5).

그림 5: 개발자는 공유 SPI 버스를 사용하여 호스트 프로세서를 하나 이상의 CY15x102QN F-RAM과 연결할 수 있습니다. (이미지 출처: Cypress Semiconductor)

그림 5: 개발자는 공유 SPI 버스를 사용하여 호스트 프로세서를 하나 이상의 CY15x102QN F-RAM과 연결할 수 있습니다. (이미지 출처: Cypress Semiconductor)

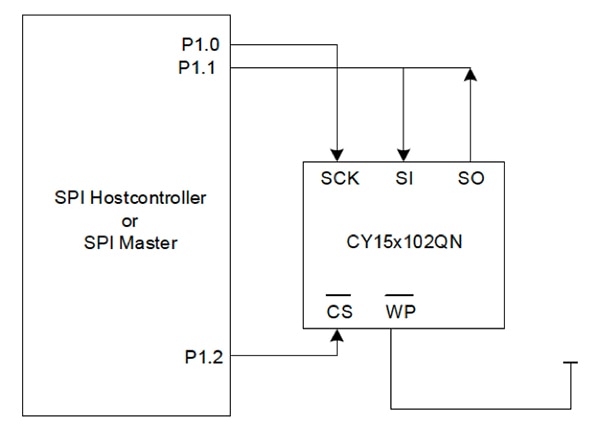

MCU에 SPI 기능이 없는 경우 CY15x102QN 장치는 마이크로 컨트롤러의 범용 IO(GPIO)를 사용하여 F-RAM에 연결하는 방식으로 SPI 하드웨어 인터페이스를 에뮬레이션하는 간단한 대안을 지원합니다. 개발자는 F-RAM의 SI 및 SO 데이터 라인에 동일한 핀을 사용하여 단 세 개의 GPIO로 이 인터페이스를 구현할 수 있습니다(그림 6).

그림 6: 마이크로 컨트롤러에 기본 SPI 기능이 없는 경우 개발자는 간단히 마이크로 컨트롤러의 범용 IO를 사용하여 CY15x102QN 직렬 F-RAM에 액세스하는 SPI 프로토콜을 에뮬레이션할 수 있습니다. (이미지 출처: Cypress Semiconductor)

그림 6: 마이크로 컨트롤러에 기본 SPI 기능이 없는 경우 개발자는 간단히 마이크로 컨트롤러의 범용 IO를 사용하여 CY15x102QN 직렬 F-RAM에 액세스하는 SPI 프로토콜을 에뮬레이션할 수 있습니다. (이미지 출처: Cypress Semiconductor)

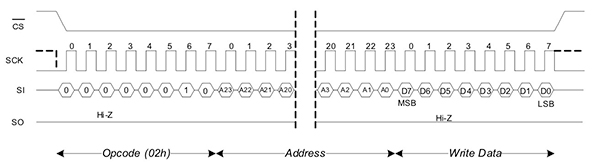

표준 SPI 프로토콜에서 마스터는 /CS를 아래로 당겨서 트랜잭션을 시작합니다. /CS가 아래로 이동하면 F-RAM은 다음 바이트를 연산 부호(opcode)로 해석합니다. 예를 들어, 쓰기 작업에서는 3바이트 주소 및 데이터 바이트를 사용하여 SPI 표준 쓰기 연산 부호(02h)를 따릅니다(그림 7).

그림 7: Cypress CY15x102QN F-RAM 장치는 표준 SPI 연산 부호 및 프로토콜을 지원하므로 개발자가 쓰기 연산 부호(02h), 주소 및 데이터를 순서대로 전송하여 지연 없이 쉽게 쓸 수 있습니다. (이미지 출처: Cypress Semiconductor)

그림 7: Cypress CY15x102QN F-RAM 장치는 표준 SPI 연산 부호 및 프로토콜을 지원하므로 개발자가 쓰기 연산 부호(02h), 주소 및 데이터를 순서대로 전송하여 지연 없이 쉽게 쓸 수 있습니다. (이미지 출처: Cypress Semiconductor)

2Mbit CY15x102QN F-RAM의 경우 주소는 3바이트 시퀀스이며, 상위 6비트는 무시됩니다. 향후에 더 높은 용량의 F-RAM 장치로 쉽게 전환할 수 있도록 이 상위 6비트를 0으로 설정하는 것이 좋습니다.

읽기 작업은 동일한 프로토콜을 따릅니다. 표준 읽기 연산 부호(03h) 및 주소를 수신한 후 F-RAM 장치는 SO에서 데이터 바이트를 순차적으로 전송합니다. 그러면 /CS는 낮게 유지되고 클록 신호는 지속적으로 전송되면서 메모리 주소는 자동으로 증가합니다. 따라서 개발자는 필요한 수의 데이터 바이트를 읽을 때까지 /CS를 낮게 유지하고 SCK 클록 신호를 지속적으로 실행하여 일괄 읽기를 간단히 수행할 수 있습니다.

또한 CY15x102QN F-RAM은 직렬 플래시 메모리와 호환되는 빠른 읽기 기능을 지원합니다. 빠른 읽기 연산 부호(0Bh) 및 주소에 따라 SPI 호스트는 더미 바이트를 전송하여 플래시 읽기 대기 시간을 에뮬레이션합니다. 더미 바이트를 수신한 후 F-RAM은 요청된 데이터로 응답합니다. 또한 빠른 읽기 작업에서는 표준 읽기와 동일한 메커니즘을 사용하여 일괄 읽기를 수행할 수 있습니다.

쓰기 보호

SPI 인터페이스 제어 논리와 함께 CY15x102QN F-RAM은 장치를 식별하고 F-RAM 어레이를 쓰기 보호하는 추가 메커니즘을 제공합니다.

개발자는 SPI 연산 부호를 실행하여 제조업체, 메모리 밀도, 부품 버전 등과 같은 정보를 제공하는 CY15x102QN 장치의 읽기 전용 고유 ID 및 장치 ID에 액세스할 수 있습니다. 또한 개발자는 8바이트 읽기/쓰기 일련 번호 레지스터를 설정하여 F-RAM을 특정 시스템 또는 구성과 연결할 수 있습니다.

F-RAM 보호를 위해 장치는 소프트웨어 및 하드웨어 메커니즘을 모두 제공합니다. 제조 중 데이터 보호를 위해 최대 3회의 표준 리플로 납땜 주기 동안 데이터 무결성을 유지하도록 전용 256바이트 특수 섹터가 고안되었습니다. 일반 작업 중 보호를 위해 장치에서는 WEL(Write-Enable Latch)을 사용하여 의도하지 않은 쓰기로부터 F-RAM 어레이를 보호합니다. 전원을 켜면 WEL이 기본적으로 지워지므로 개발자는 쓰기 작업을 수행하기 전에 WREN(Write-Enable) 연산 부호(06h)를 실행해야 합니다.

장치 상태 레지스터에서 개발자는 블록 보호(BP) 비트 쌍(BP0 및 BP1)을 사용하여 전체 주소 범위(BP1=1, BP0=1), 메모리의 상반부(BP1=1, BP0=0) 또는 메모리의 하반부(BP1=0, BP0=1)에서 메모리를 보호할 수 있습니다.

개발자는 하드웨어 쓰기 보호 핀(/WP)을 사용하여 일반 작업 중에 소프트웨어에서 BP 비트를 수정하지 못하도록 차단할 수 있습니다. 이때 개발자는 상태 레지스터에서 WPEN(Write Protect Enable) 비트를 설정하고 /WP 핀을 아래로 이동하여 상태 레지스터를 잠급니다.

전력 관리

일반 작업에서 일반적으로 F-RAM 기술에 고유한 에너지 효율로 인해 최대 50MHz 클록 속도 작업에서 CY15V102QN(VDD 1.71V ~ 1.89V)의 전류 소비는 5.0mA에 불과합니다. 개발자는 추가적인 전력 절감을 위해 클록 주파수를 줄일 수 있습니다. CY15V102QN의 경우 1MHz에서 전류 소비가 약 0.4mA로 감소합니다. CY15B102QN(VDD 1.8V ~ 3.6V)의 전류 소비는 50MHz에서 6.0mA, 1MHz에서 0.5mA로 약간 더 높습니다.

오래동안 사용하지 않을 경우 개발자는 SPI 연산 부호로 CY15x102QN 장치를 세 가지 저전력 모드로 설정하여 전력 소비를 크게 줄일 수 있습니다.

- 대기 모드: 일반 전류 소비 - 2.7μA(CY15V102QN) 또는 3.2μA(CY15B102QN)

- 최대 절전 모드: 1.1μA(CY15V102QN) 또는 1.3μA(CY15B102QN)

- 절전 모드: 0.1μA(두 부품 모두)

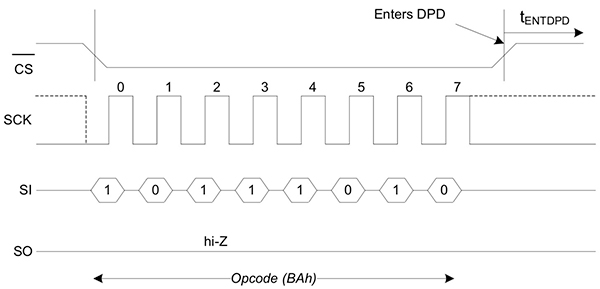

SPI 호스트에서 연산 부호 시퀀스를 마칠 때 /CS를 High로 설정하면 CY15x102QN 장치가 자동으로 대기 모드로 전환됩니다. 장치를 최대 절전 모드 또는 절전 모드로 전환하려면 SPI 호스트에서 SPI 연산 부호 프로토콜을 사용합니다. 특히, SPI 호스트는 /CS를 처음으로 Low로 설정한 후 최대 절전 모드(BAh) 또는 절전 모드(B9h)에 대한 특수 연산 부호를 전송하고 /CS를 High로 설정하여 두 최소 전력 모드 중 하나로 전환합니다(그림 8).

그림 8: CY15x102QN F-RAM 장치는 연산 부호 시퀀스 후에 대기 모드로 자동으로 전환되지만, 개발자는 일반 SPI 연산 부호 절차에 따라 최대 절전 모드(DPD)와 같은 더 낮은 전력 모드로 전환할 수 있습니다. (이미지 출처: Cypress Semiconductor)

그림 8: CY15x102QN F-RAM 장치는 연산 부호 시퀀스 후에 대기 모드로 자동으로 전환되지만, 개발자는 일반 SPI 연산 부호 절차에 따라 최대 절전 모드(DPD)와 같은 더 낮은 전력 모드로 전환할 수 있습니다. (이미지 출처: Cypress Semiconductor)

SPI 호스트에서 적절한 저전력 연산 부호를 전송한 후 /CS를 High로 설정하면 CY15x102QN F-RAM은 약 3μs 이내에 요청된 저전력 모드로 전환됩니다.

대기 모드에서 Cypress F-RAM은 /CS가Low로 설정되면 즉시 활성 모드로 복귀하여 다음 연산 부호 시퀀스를 시작합니다. 최대 절전 모드 또는 절전 모드에서도 F-RAM은 /CS가 Low로 설정되면 활성 모드로 복귀하지만 최대 절전 모드의 경우 약 10μs, 절전 모드의 경우 450μs의 짧은 지연 시간이 발생합니다.

결론

증가하는 센서 어레이의 데이터에 의존하는 광범위한 응용 분야에서 안정적이고 빠른 저전력 고성능 NVM의 중요성이 점점 더 커지고 있습니다. 자동차 ADAS 응용 분야와 같은 핵심 영역에서 데이터 손실은 차량과 탑승객을 보호하도록 고안된 안전 메커니즘의 성능을 크게 저하시킬 수 있습니다.

Cypress Semiconductor의 F-RAM 장치를 사용하여 개발자는 성능 또는 저전력 요구 사항에 영향을 주지 않고 수십 년 동안 중요 데이터를 안정적으로 저장할 수 있는 NVM을 쉽게 추가할 수 있습니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.