부품 선택을 최적화하는 수정 발진기 파라미터 이해하기

DigiKey 북미 편집자 제공

2021-03-02

석영 기반 수정 발진기는 거의 모든 전자 회로의 주파수/타이밍 정확도 및 성능을 좌우하는 핵심 부품입니다. 따라서, 시간에 걸쳐 정확하고 정밀해야 합니다. 물론 “완벽한” 발진기는 이론적으로만 존재합니다. 그러므로 설계자들은 설계 목적을 충족하는 올바른 발진기를 선택해야 합니다. 이는 쉽지 않은 일입니다.

응용 제품에 대해 성능 요구 사항이 결정되면 설계자들은 성능, 비용, 안정성, 크기, 전력, 물리적 구조 및 연결된 회로망에 대한 구동 능력 사이에서 올바른 균형을 갖는 솔루션을 찾아야 합니다. 이렇게 하려면, 발진기 작동 원리, 주요 특성 및 발전 과정을 이해해야 합니다.

이 기사에서는 수정 발진기 기본 사항에 대한 개요를 제공한 후 고성능 수정 발진기 모듈과 연관된 다양한 퍼스펙티브를 살펴보겠습니다. 그런 다음, ECS Inc.의 대표 장치를 사용하여 이러한 발진기의 기본 사항을 간략하게 검토하고, 제1 및 제2 파라미터에 대한 일부 실제 값과 함께 이러한 파라미터를 식별합니다. 또한 서로 다른 장치가 일부 일반적인 응용 제품의 필요 사항에 어떻게 정합되는지 보여줍니다.

수정 발진기의 작동 방식

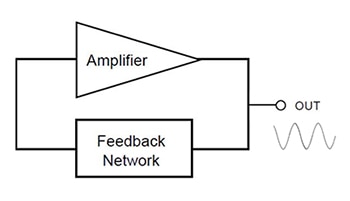

수정 발진기는 프로세서를 위한 클록 하트비트, 데이터 링크를 위한 비트 타이밍, 데이터 변환을 위한 샘플링 시간, 동조기 및 합성기의 마스터 주파수를 제공합니다. 간단히 말해, 수정 발진기의 석영 소자는 발진기 회로의 피드백 네트워크 내에서 초고 Q 공진 소자로서 작동합니다(그림 1). 수정 및 수정 발진기의 중요성으로 인해, 석영 재료의 기초 물리학과 해당하는 전기적 및 기계적 성능은 다양한 발진기 회로와 함께 포괄적으로 연구되고 분석되어 왔습니다.

그림 1: 압전 효과를 사용하는 수정은 발진기 회로의 피드백 루프에서 고 Q, 안정적, 정밀 공진 소자로서 작동합니다. (이미지 출처: ECS Inc. International, modified)

그림 1: 압전 효과를 사용하는 수정은 발진기 회로의 피드백 루프에서 고 Q, 안정적, 정밀 공진 소자로서 작동합니다. (이미지 출처: ECS Inc. International, modified)

여러 해 동안 사용자는 수정 주파수 및 기타 주요 특성을 지정한 다음, 진공 튜브를 사용하여(초기) 별도의 고유한 발진기 회로, 트랜지스터, 마지막으로 IC를 제공했습니다. 여러 절묘한 요소들이 서로 밀접한 관계를 이루고 있는 이 회로는 일반적으로 신중한 설계 분석뿐만 아니라 약간의 “예술적” 및 경험 기반 판단을 필요로 합니다. 설계자는 발진기 성능을 수정 진동자의 "절단" 및 특성뿐만 아니라 응용 제품 우선 순위에 일치시키기 위해 이러한 요소 간에 균형을 맞추려고 시도합니다.

이 경우 올바른 초기 설계를 획득하는 데 시간과 노력이 필요하기 때문에 요즘에는 좀처럼 이러한 DIY 수정 발진기 설계에 노력을 기울이지 않습니다. 다음으로, 발진기의 성능을 정확하게 측정해야 합니다. 이는 복잡한 과정이며 정밀 기기와 주의 깊은 설정이 필요합니다. 대신에, 여러 응용 제품의 경우 설계자가 석영 소자와 발진기 회로 및 출력 구동기를 모두 포함하는 완전히 밀폐된 소형 모듈을 구매할 수 있습니다. 이렇게 하면 설계 노력과 시간이 확실히 감소하고 사용자는 완전히 특성화된 장치와 사양이 보장된 규격서를 얻게 됩니다.

용어 설명: 역사적 이유 및 다른 이유로 엔지니어들은 전체 수정 발진기 회로에 대해 실제로 이야기할 때 "수정"이라는 단어를 종종 사용합니다. 의도된 의미가 상황적으로 이해되기 때문에 이는 일반적으로 문제가 되지 않습니다. 그러나, 이는 여전히 수정을 독립적 부품으로 구입한 다음 별도의 발진기 회로망을 제공해야 할 수 있기 때문에 혼동을 일으킬 수 있습니다. 이 기사에서 사용되는 “발진기”라는 용어는 단지 발진기 회로를 단독으로 가리키는 것이 아니라 독립적 모듈로서 수정 및 수정 발진기 회로망을 의미합니다.

수정 발진기의 특성

다른 부품과 마찬가지로 수정 발진기의 성능은 처음에 일련의 제1 파라미터에 의해 정의됩니다. 중요도 순으로 요약하면 다음과 같습니다.

작동 주파수: 이는 수십 kHz ~ 수백 MHz 범위에 이를 수 있습니다. 기가헤르츠(GHz) 범위와 같이 발진기의 기본 도달 범위를 초과하는 주파수를 위한 발진기는 일반적으로 위상 고정 루프(PLL)를 주파수 승수로 사용하여 기본 주파수를 상향 변환합니다.

주파수 안정성: 이 특성은 발진기의 두 번째 핵심 성능 요인입니다. 이는 외부 조건으로 인해 원래 값에서 출력 주파수의 편차를 정의하므로, 이 숫자가 작을수록 더 좋습니다.

안정성에 영향을 미치는 여러 외부 조건이 있으며, 많은 벤더들이 이를 개별적으로 설명하여 설계자가 응용 제품에 대한 실제 영향을 평가할 수 있습니다. 이러한 요인 중 공칭 주파수(25°C 기준)에 대한 온도 관련 변동이 있습니다. 다른 요인으로는 노화로 인한 장기적 안정성, 납땜 효과, 공급 전압 변동 및 출력 부하 변화가 있습니다. 고성능 장치의 경우 이 특성은 대개 공칭 출력 주파수에 대해, 백만분율(ppm) 또는 십억분율(ppb)로 나타냅니다.

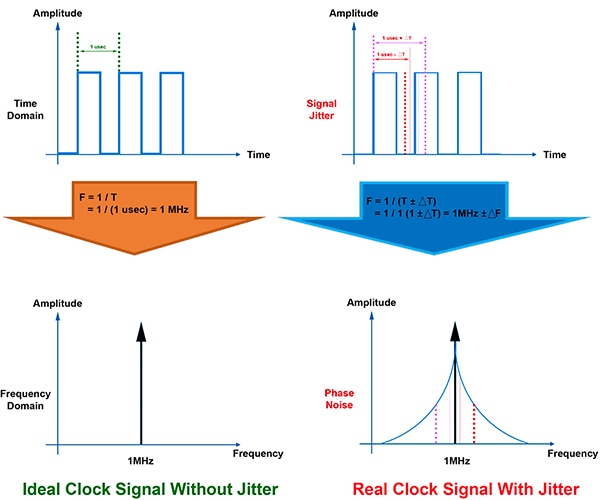

위상 잡음 및 지터: 이는 동일한 일반 성능 등급에 대한 두 가지 퍼스펙티브입니다. 위상 잡음은 주파수 영역에서의 클록 잡음을 나타내고 지터는 시간 영역에서의 클록 잡음을 나타냅니다(그림 2).

그림 2: 시간 영역에서의 지터 및 주파수 영역에서의 위상 잡음은 동일한 결함에 대한 동등하게 유효한 두 가지 해석입니다. 기본 보기는 응용 함수입니다. (이미지 출처: ECS Inc. International)

그림 2: 시간 영역에서의 지터 및 주파수 영역에서의 위상 잡음은 동일한 결함에 대한 동등하게 유효한 두 가지 해석입니다. 기본 보기는 응용 함수입니다. (이미지 출처: ECS Inc. International)

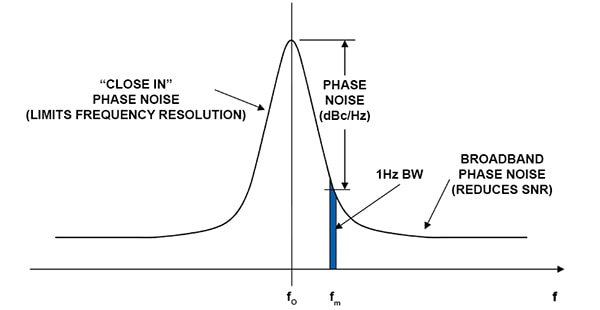

응용 제품에 따라 설계자는 주로 한 영역 또는 다른 영역에서 정의되는 오차에 중점을 둡니다. 위상 잡음은 일반적으로 지정된 주파수 오프셋(fm)을 기준으로 주파수 fO에서의 발진기 신호 진폭까지 1Hz 대역폭에서의 잡음 비율로 정의됩니다. 위상 잡음은 주파수 합성기의 정확도, 분해능, 신호대 잡음비(SNR)를 저하시키고(그림 3), 지터는 타이밍 오차를 일으켜 데이터 링크에서의 비트 오류율(BER)을 증가시킵니다.

그림 3: 위상 잡음은 발진기의 전력 스펙트럼을 확산시키며 분해능 및 SNR에 대한 악효과를 제공합니다. (이미지 출처: ECS Inc. International)

그림 3: 위상 잡음은 발진기의 전력 스펙트럼을 확산시키며 분해능 및 SNR에 대한 악효과를 제공합니다. (이미지 출처: ECS Inc. International)

타이밍 지터는 아날로그/디지털 변환에서 샘플링 시간 오차를 일으키며 이로 인해 SNR 및 후속 고속 푸리에 변환(FFT) 주파수 분석에도 영향을 미칩니다.

ECS Inc.의 MultiVolt 표준 발진기 제품군의 장치(MV)는 ±20ppm 정도의 안정성으로 제공되며 타이트 안정성 발진기(SMV)는 최저 ±5ppm의 안정성을 제공합니다. 더 타이트한 안정성을 위해 MultiVolt TCXO는 ±2.5ppm 성능(HCMOS 출력) 및 클리핑 사인파 출력에 대해서는 ±0.5ppm을 제공합니다(TCXO 및 클리핑 사인파에 대해서는 아래에서 더 자세히 설명됨).

영역에 관계없이, 위상 잡음/지터는 고성능 설계를 위한 중요한 요인이며 응용 제품의 필요 사항과 함께 오차 할당에 고려해야 합니다. 절대 지터, 주기 간 지터, 통합 위상 지터, 장기 지터 및 주기 지터를 포함하여 여러 유형의 지터가 있습니다. 위상 잡음의 경우에도 백색 잡음 및 다양한 잡음 "색상"을 포함하여 여러 다른 통합 범위 및 유형이 있습니다.

발진기의 지터 및 위상 잡음에 대한 세부 사항과 응용 제품에서의 영향을 이해하는 것은 쉽지 않은 과제일 수 있습니다. 영역 간에 사양을 변환하기는 어렵습니다. 대신에 사용자는 규격서를 확인해야 합니다. 전반적인 오차 할당에 이러한 오차를 고려할 때에는 다양한 합법적 벤더 정의를 이해해야 합니다.

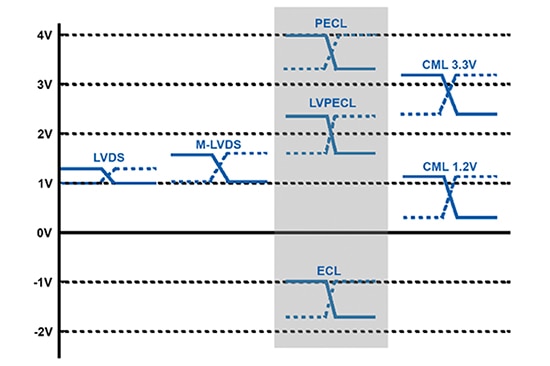

출력 신호 유형 및 구동: 이는 연결된 부하과 일치해야 합니다(그림 4). 두 가지 출력 구동 토폴로지 단일 종단 및 차동이 있습니다.

그림 4: 제공되는 다양한 출력 형식은 발진기 부하 구성과 호환되어야 합니다. (이미지 출처: ECS Inc. International)

그림 4: 제공되는 다양한 출력 형식은 발진기 부하 구성과 호환되어야 합니다. (이미지 출처: ECS Inc. International)

단일 종단 발진기는 구현하기 쉽지만 잡음에 더 민감합니다. 또한 일반적으로 최대 수백 메가헤르츠 종단 발진기는 구현하기 쉽지만 잡음에 더 민감합니다. 또한 일반적으로 최대 수백 메가헤르츠에만 적합합니다. 단일 종단 출력 유형에는 다음이 포함됩니다.

- TTL(트랜지스터-트랜지스터 논리): 0.4V ~ 2.4V(지금은 거의 사용되지 않음)

- CMOS(금속 산화물 반도체): 0.5V ~ 4.5V

- HCMOS(고속 CMOS): 0.5V ~ 4.5V

- LVCMOS(저전압 CMOS): 0.5V ~ 4.5V

차동 출력의 경우 설계하기가 더 어렵지만 고주파 응용 제품에서 더 나은 성능을 제공합니다. 차동 트레이스에 일반적인 모든 잡음이 상쇄 출력의 경우 설계하기가 더 어렵지만 고주파 응용 제품에서 더 나은 성능을 제공합니다. 차동 트레이스에 일반적인 모든 잡음이 상쇄되기 때문입니다. 이는 부하 회로에 표시되는 대로 발진기 성능을 유지하는 데 도움이 됩니다. 차동 신호 유형은 다음과 같습니다.

- PECL(포지티브 방출기 결합 논리): 3.3V ~ 4.0V

- LVPECL(저전압 PECL): 1.7V ~ 2.4V

- CML(전류 모드 논리): 0.4V ~ 1.2V 및 2.6V ~ 3.3V

- LVDS(저전압 차동 신호): 1.0V ~ 1.4V

- HCSL(고속 전류 스티어링 논리): 0.0V ~ 0.75V

신호 유형은 응용 우선 순위 및 연결된 회로망에 따라 결정됩니다.

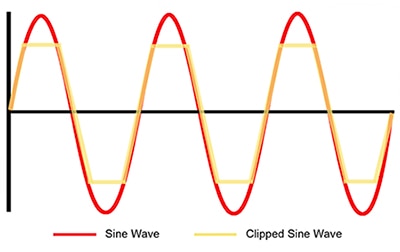

발진기 출력 파형은 전형적인 단일 주파 사인파 또는 클리핑 사인파일 수 있습니다(그림 5). 아날로그파는 비교기 회로를 사용하여 방형파로 변환하는 것과 비교하여 "가장 깨끗하고" 지터/위상 잡음의 영향을 가장 적게 받습니다. 비교기 회로를 사용할 경우 지터/위상 잡음이 추가되어 성능이 떨어지기 때문입니다. 클리핑 사인파는 방형파와 유사한 출력을 생성합니다. 이 출력은 어떠한 성능도 감소시키지 않고 디지털 부하와 호환됩니다.

그림 5: 클리핑 사인파는 방형파와 비슷하지만 추가적인 지터 또는 위상 잡음을 최소화합니다. (이미지 출처: ECS Inc. International)

그림 5: 클리핑 사인파는 방형파와 비슷하지만 추가적인 지터 또는 위상 잡음을 최소화합니다. (이미지 출처: ECS Inc. International)

공급 전압 및 전류: 이 두 사양은 오늘날의 저전압 및 배터리 구동식 시스템의 필요 사항을 충족하기 위해 모두 감소되었습니다. 대부분의 MultiVolt 계열 발진기는 1.8V, 2.5V, 3.0V, 3.3V의 공급 전압으로 작동할 수 있습니다.

패키지 크기: 작동 전압 및 전류와 마찬가지로 발진기 패키지도 소형화되고 있습니다. 업계는 단일 종단 장치(4개의 연결만 필요)에 대해 표준화된 크기를 제공하지만, 차동 발진기는 6개의 접점을 제공하고 더 큰 패키지를 사용합니다(여기에는 mm 단위의 치수가 제공됨).

1612: 1.6mm × 1.2mm

2016: 2.0mm × 1.6mm

2520: 2.5mm × 2.0mm

3225: 3.2mm × 2.5mm

5032: 5.0mm × 3.2mm

7050: 7.0mm × 5.0mm

중요한 인자인 온도

발진기의 성능에 가장 큰 영향을 주고 변화시키는 외부 요인은 온도입니다. 발진기 작동 전력은 낮으며, 이로 인해 자체 발열이 거의 무시되지만 주변 온도는 수정 진동자의 기계적 치수와 응력에 영향을 주기 때문에 작동 주파수에 영향을 미칩니다. 예측된 범위의 변곡점에서 선별된 발진기의 성능을 확인해야 합니다. 이러한 범위는 일반적으로 다음과 같이 설명됩니다.

- 상업, 자동차 등급 : 0°C ~ +70°C

- 확장된 상업: -20°C ~ +70°C

- 산업, 자동차 등급 3: -40°C ~ +85°C

- 확장된 산업, 자동차 등급 2: -40°C ~ +105°C

- 자동차 등급 1: −40°C ~ +125°C

- 군사: -55°C ~ +125°C

- 자동차 등급 0: -40°C ~ +150°C

일부 설계의 경우, 온도에 대한 성능만 고려하는 것이 아니라 다른 신뢰성 사양도 충족해야 합니다. 예를 들어 ECS-2016MVQ는 1.7V ~ 3.6V 작동을 위한 미니어처 표면 실장 MultiVolt HCMOS 출력 발진기입니다(그림 6). 2016(2.0mm × 1.6mm, 위 참조) 세라믹 패키지는 0.85mm 높이이며 더 열악한 산업 응용 제품을 대상으로 합니다. 이는 1등급 온도 요구 사항을 위해 AEC-Q200 인증을 획득했습니다. 이 장치는 -40°C ~ +85°C에서 ±20ppm ~ ±100ppm의 4가지 주파수 안정성 등급으로 1.5MHz ~ 54MHz 범위의 주파수에 사용할 수 있습니다. 위상 지터는 불과 1ps로 매우 낮으며 12kHz ~ 5MHz에서 측정됩니다.

그림 6: ECS-2016MVQ는 1.5MHZ ~ 54MHz의 주파수와 4가지 등급의 안정성(±20ppm ~ ±100ppm)으로 제공됩니다. (이미지 출처: ECS Inc. International)

그림 6: ECS-2016MVQ는 1.5MHZ ~ 54MHz의 주파수와 4가지 등급의 안정성(±20ppm ~ ±100ppm)으로 제공됩니다. (이미지 출처: ECS Inc. International)

작동 범위에서의 드리프트가 허용할 수 없을 정도로 높은 응용 제품의 경우 온도 보정 수정 발진기(TCXO) 및 오븐 제어 수정 발진기(OCXO)의 두 가지 고급 발진기 구현을 사용할 수 있습니다. XTAL은 여러 회로도에서 수정을 지칭하며 “X”는 이에 대한 약자로 사용됩니다. TCXO는 능동 회로를 사용하여 온도 변동으로 인한 출력 주파수 변화를 보정합니다. 반대로, OCXO에서는 최대 주변 온도보다 높은 일정 온도로 가열되고 유지되는 단열 오븐에 수정 발진기가 배치됩니다(발열 전용 오븐은 주변 온도 아래로 냉각될 수 없음).

TCXO에는 기본 발진기와 비교하여 추가적인 회로망이 있어야 하지만 오븐이 있는 OCXO보다 훨씬 낮은 전력(일반적으로 수 와트)을 필요로 합니다. 또한, TCXO는 비보정 장치에 비해 약간 크고 OCXO보다 훨씬 작습니다. TCXO는 일반적으로 비보정 장치보다 10배 ~ 40배의 드리프트 개선을 나타냅니다. 이와 비교하여 OXCO는 2배 정도 개선된 드리프트 성능을 보일 수 있지만 크기와 전력 측면에서는 상당한 불이익이 있습니다.

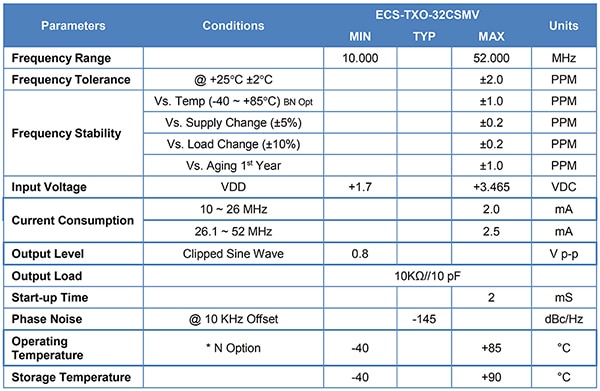

ECS-TXO-32CSMV는 10MHz ~ 52MHz의 주파수를 위한, MultiVolt 기능을 갖춘(1.7V ~ 3.465V 공급) 클리핑 사인파 표면 실장 TCXO입니다(그림 7). 3.2mm × 2.5mm × 1.2mm 세라믹 패키지는 안정성이 중요시되는 휴대용 및 무선 응용 제품에 매우 적합합니다. 주요 사양을 통해 2mA 미만의 적당한 전류 요구 사항과 함께 온도, 공급 변경, 부하 변경, 노화에 대해 매우 높은 안정성을 확인할 수 있습니다(표 1).

그림 7: ECS-TXO-32CSMV는 내부 보정 회로망을 통합하여 안정성 성능을 크게 향상시키는 클리핑 사인파 출력 수정 발진기입니다. (이미지 출처: ECS Inc. International)

그림 7: ECS-TXO-32CSMV는 내부 보정 회로망을 통합하여 안정성 성능을 크게 향상시키는 클리핑 사인파 출력 수정 발진기입니다. (이미지 출처: ECS Inc. International)

표 1: 온도 보정된 ECS-TXO-32CSMV TXCO의 사양에서는 일련의 외부 장애에도 불구하고 내부 보정이 안정성 성능을 얼마나 향상시키는지 보여줍니다. (이미지 출처: ECS Inc. International)

표 1: 온도 보정된 ECS-TXO-32CSMV TXCO의 사양에서는 일련의 외부 장애에도 불구하고 내부 보정이 안정성 성능을 얼마나 향상시키는지 보여줍니다. (이미지 출처: ECS Inc. International)

대부분 중요시되는 저전력 작동

점점 더 높은 주파수 프로세서 클록과 데이터 속도로 향하는 추세에도 불구하고, 초저전력 응용 제품의 타이밍을 위한 저주파 수정 발진기에 대한 요구는 여전히 많습니다. 예를 들어, ECS-327MVATX는 MultiVolt 기능을 사용하여(1.6V ~ 3.6V) 32.768kHz의 고정 주파수에서 작동하는 미니어처 표면 실장 발진기입니다. 200µA(마이크로 암페어)에 불과한 전류 요구 사항과 단일 종단 CMOS 출력을 제공하는 이 장치는 실시간 클록(RTC), 저전력/휴대용, 산업 및 사물 인터넷(IoT) 응용 제품에 적합합니다. 이 장치는 2016 ~ 7050 패키지 크기로 제공되며, 모델에 따라 -40⁰C ~ +85⁰C의 온도 범위에서 타이트한 ±20ppm부터 다소 느슨한 ±100ppm에 이르는 주파수 안정성 범위를 제공합니다.

평균 전력 소비를 최소화하기 위해 여러 발진기는 활성화/비활성화 기능도 제공합니다. 예를 들어 ECS-5032MV는 1.6V ~3.6V의 MultiVolt 작동 성능과 CMOS 출력을 제공하는 125MHz 표면 실장 발진기이며 5032 세라믹 패키지로 제공됩니다(그림 8).

그림 8: ECS-5032MV는 전력 절감에 도움을 줄 수 있는 활성화/비활성화 기능을 갖춘 125MHz 표면 실장 발진기입니다. (이미지 출처: ECS Inc. International)

그림 8: ECS-5032MV는 전력 절감에 도움을 줄 수 있는 활성화/비활성화 기능을 갖춘 125MHz 표면 실장 발진기입니다. (이미지 출처: ECS Inc. International)

4개 접점 중 하나를 통해 발진기를 대기 모드로 전환하여 필요한 전류를 35mA 활성 값에서 10μA (마이크로 암페어) 대기 전류로 줄일 수 있습니다. 시동 시간은 장치를 재활성화한 후 5ms입니다.

응용 제품과 일치하는 사양

응용 제품에 적절한 수정 발진기를 결정하려면 사양, 우선 순위, 비용 및 상대적 가중을 적절하게 조합해야 합니다. 필요한 공칭 주파수, 주파수 안정성, 지터/위상 잡음 및 기타 속성을 가진 장치를 독립형 발진기로 선택하는 것은 명백한 고려사항 그 이상입니다. 사용자는 또한 발진기의 출력 구동이 연결된 부하 및 시스템과 호환되어, 페어링으로 인해 성능이 저하되지 않도록 해야 합니다. 여러 고려 사항이 있지만 일반적인 지침은 다음과 같습니다.

- LVDS 출력은 수신기에 단일 저항기만 있으면 되지만 LVPECL은 송신기와 수신기 모두에 종단이 필요합니다.

- LVDS, LVPECL HCSL는 CMOS보다 빠른 전이를 제공하지만 추가적인 전력을 필요로 하며 고주파 설계에 가장 적합합니다.

- 최저 전력 소비를 원하는 경우(150MHz 이상) CMOS 또는 LVDS가 가장 적합합니다.

- LVPECL, LVDS, CMOS는 더 낮은 주파수에서 최적의 지터 성능을 제공합니다.

결론

수정 진동자 발진기는 여러 회로 및 시스템에 있어 핵심입니다. 이 기능의 성능이 응용 제품 요구 사항과 일치하도록 하려면 공칭 주파수 정확도, 안정성 대 온도 및 기타 요인(예: 지터 및 위상 잡음)부터 시작하여 주요 파라미터 간에 신중하게 균형을 유지해야 합니다. 또한 발진기의 출력 구동 형식을 부하 회로망의 특성에 맞춰야 합니다. ECS MultiVolt 제품군의 수정 발진기는 완전하고 사용이 쉬운 모듈에 여러 사양을 조합함으로써 뛰어난 성능을 제공합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.