위상 고정 루프 주파수 합성기 기본 사항

DigiKey 북미 편집자 제공

2021-02-03

고속 직렬 통식 버스에서 늘어나는 데이터 전송률로 인해 더 높은 주파수, 우수한 안정성과 주파수 솔루션 및 더 높은 신호 순도를 지닌 시스템 클록이 요구됩니다. 직접 디지털 합성기가 이런 특성을 제공하기는 하지만 주파수는 2GHz 또는 3GHz 미만입니다. 최대 수십 기가헤르츠의 주파수를 제공할 수 있는 솔루션이 요구됩니다.

이러한 솔루션은 최대 30GHz의 클록 주파수를 생성하는 위상 고정 루프(PLL) 기반 아날로그 주파수 합성기로부터 시작합니다. 그런 다음 정수형 N 합성기(참조 주파수에 정수형 값을 곱함) 및 실수형 N 합성기(참조 주파수에 비정수형 실수형 값을 곱함)는 위상 잡음 및 유사한 신호 비순도를 최소화하는 특별한 기술을 사용합니다.

이 기사에서는 Analog Devices의 디바이스를 예로 들어 정수형 및 실수형 N 주파수 합성기의 설계에 대해 설명합니다. 또한 이 기사는 이러한 장치를 주파수 가변 레이더뿐 아니라 고속 직렬 데이터 링크에서도 사용할 수 있게 된 혁신에 대해서도 중점적으로 다룹니다.

정수형 N 위상 고정 루프 합성기

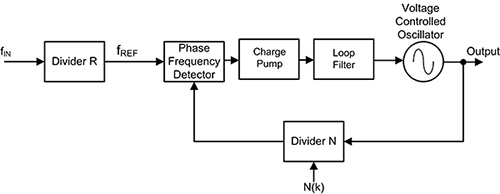

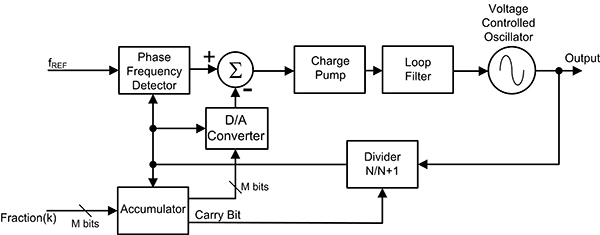

PLL 회로는 주파수 및 위상 제어에 사용됩니다. PLL 회로를 클록 소스, 주파수 배율기, 복조기, 추적 발생기 또는 클록 복구 회로로 구성할 수 있습니다. 응용 분야마다 서로 다른 특성이 요구되지만, 모든 응용 분야에서 기본 회로 개념은 동일합니다. 그림 1은 주파수 배율기로 구성된 PLL의 제품 구성도를 보여줍니다.

그림 1: 기존 정수형 N 위상 고정 루프 주파수 합성기 제품 구성도. (이미지 출처: DigiKey)

그림 1: 기존 정수형 N 위상 고정 루프 주파수 합성기 제품 구성도. (이미지 출처: DigiKey)

모든 위상 고정 루프에서 이러한 회로의 작동이 일반적입니다. 기본적으로 전압 제어 발진기(VCO)의 위상을 제어하는 피드백 제어 시스템입니다. 입력 신호는 사전 비율 조정 분할기로 적용되며, 이 분할기는 입력 주파수를 팩터 R로 나눕니다. 전치 분주기의 출력은 기준 주파수로, 위상 주파수 감지기(RFD) 중 하나의 입력을 형성합니다.

다른 PFD 입력은 N으로 나누기 카운터 출력의 피드백 신호입니다. PLL이 잠긴 경우, 일반적으로 두 신호의 주파수는 거의 동일합니다. 위상 검파기의 출력은 두 입력 간 위상 차이에 비례하는 전압입니다. 루프가 잠기지 않은(시작 시 발생하거나 입력 주파수에 크고 순간적인 전환이 있을 때 발생함) 경우에는, 위상 주파수 감지기가 작동하여 PLL 작동 주파수를 원하는 설정으로 조정합니다. 그 주파수가 달성되면 PFD가 위상 검파기 모드로 되돌아가며, 기준 주파수와 피드백 신호 간의 위상차에 비례하는 출력을 갖춥니다.

위상 주파수 감지기는 양극 스위치 전류원인 충전 펌프를 구동합니다. 이는 감지기가 PLL의 루프 필터로 포지티브 및 네거티브 전류 펄스를 출력할 수 있음을 의미합니다.

루프 필터는 위상 오류 신호를 수정하고 PLL의 동적 특성을 결정합니다. 필터링된 신호는 VCO를 제어합니다. VCO의 출력은 위상 주파수 감지기의 주파수 레퍼런스 입력에 공급되는 입력의 N배에 해당하는 주파수 위치이며, 이는 주파수 입력의 N/R 배에 해당합니다. 이 출력 신호는 N으로 나누기 카운터를 통해 위상 검파기로 다시 전송됩니다.

일반적으로 루프 필터는 PLL 응용 분야에 필요한 특성에 적합하도록 설계됩니다. PLL이 신호를 취득하고 추적하는 경우 루프 필터의 대역폭은 고정 입력 주파수가 필요한 경우보다 더 큽니다. PLL에서 허용되고 고정되는 주파수 범위를 "캡처 범위"라고 합니다. PLL이 고정되고 신호를 추적 중인 경우 PLL이 따르는 주파수 범위를 "추적 범위"라고 합니다. 일반적으로 추적 범위는 캡처 범위보다 더 큽니다. 또한 PLL 루프 필터에 따라 고정 상태를 유지하면서 신호 주파수가 변경될 수 있는 속도(예: 최대 슬루율)가 결정됩니다. 루프 필터 대역폭이 좁을수록 달성 가능한 위상 오류가 더 적습니다. 따라서 응답이 느려지고 캡처 범위가 작아집니다. 클록 응용 분야에 사용되는 PLL은 주로 고정 주파수에서 작동합니다. 일반적으로 루프 필터의 대역폭은 기준 주파수보다 훨씬 낮아야 합니다.

PLL 출력 주파수는 기준 주파수의 정수형 배수이므로, 주파수 분해능은 기준 주파수와 동일합니다. 더 우수한 주파수 분해능을 달성하기 위해서는 기준 주파수가 낮아져야 하며, 이를 위해서는 사전 조정 카운터 R이 필요합니다.

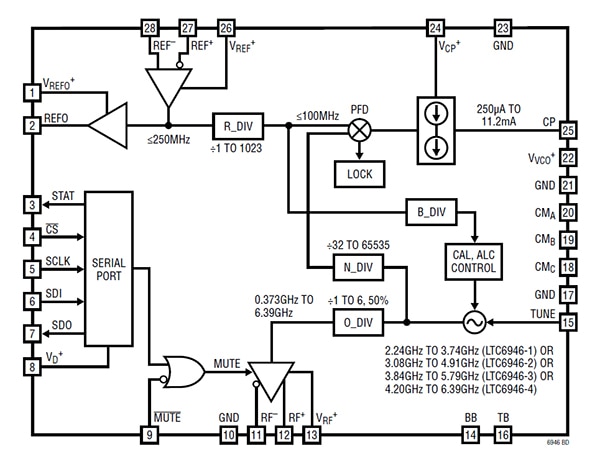

정수형 N 주파수 합성기의 상용 예로는 통합형 VCO 및 우수한 스퓨리어스 성능을 갖춘 저잡음 0.64GHz ~ 5.790GHz 합성기인 Analog Devices의 LTC6946IUFD-3#PBF가 있습니다(그림 2). 4개의 합성기 IC 제품군 중 하나로 각 합성기는 서로 다른 주파수 범위를 지니며 총 범위는 0.373GHz ~ 6.390GHz입니다.

그림 2: 통합형 VCO를 갖춘 Analog Devices LTC6946IUFD-3#PBF 정수형 N 주파수 합성기 제품 구성도 (이미지 출처: Analog Devices)

그림 2: 통합형 VCO를 갖춘 Analog Devices LTC6946IUFD-3#PBF 정수형 N 주파수 합성기 제품 구성도 (이미지 출처: Analog Devices)

이 합성기에는 특정 응용 제품에 최적화할 수 있는 외부 사용자 제공 루프 필터가 있어야 합니다. 분할 범위가 1 ~ 1023인 내부 사전 조정 카운터 분할기는 포함되어 있습니다. 루프 분할기의 범위는 32 ~ 65535입니다. 충전 펌프 전류는 루프 필터의 요구 사항에 맞도록 250mA부터 11.2mA까지 조정 가능합니다.

실수형 N 위상 고정 루프 합성기

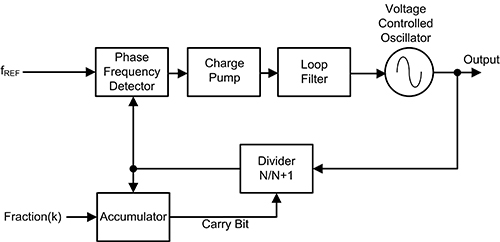

PLL 합성기의 주파수 분해능은 스텝 크기를 정수형 값 미만으로 줄임으로써 개선될 수 있습니다(예: 루프 분할기(N)에서 실수형 스텝을 만듦). 이는 카운트다운 값을 동적으로 변경하거나 "디더링"하는 방법으로 달성됩니다. 이는 분배기 설정이 PLL 출력 주파수의 고정된 회수의 주기 동안 값 N을 유지하고, 주기적으로 N + 1과 같은 다른 값으로 단계적으로 스텝됨을 의미합니다. 예를 들어 분할기 설정이 세 기준 시간에서 4, 네 번째 기준 주기에서 5라면, 유효한 카운트다운은 4.25입니다. 이를 달성하기 위한 방법 중 하나는 그림 3에서 볼 수 있듯이 누산기를 사용하는 것입니다.

그림 3: 분할기 카운트를 변조하는 누산기를 사용하는 실수형 N PLL 합성기 제품 구성도 (이미지 출처: DigiKey)

그림 3: 분할기 카운트를 변조하는 누산기를 사용하는 실수형 N PLL 합성기 제품 구성도 (이미지 출처: DigiKey)

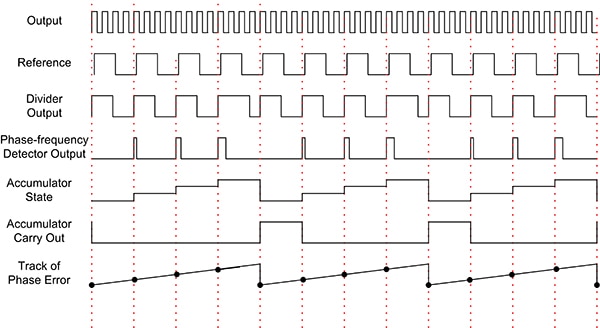

누산기는 분할기로부터의 출력 펄스를 카운트하며, 모든 M(누산기의 계수)은 분할기 입력을 바꾸는 캐리 비트를 출력합니다. 그림 4는 실수형 분할기 설정을 4.25로 설정하는 예입니다.

그림 4: 누산기를 사용하는 실수형 N PLL 합성기 타이밍 구성도. (이미지 출처: DigiKey)

그림 4: 누산기를 사용하는 실수형 N PLL 합성기 타이밍 구성도. (이미지 출처: DigiKey)

이 누산기는 분할 출력에 의해 구동되며 모듈로 4(M=4)로 카운트합니다. 누산기가 네 번째 펄스마다 캐리 출력을 생성하면 이에 따라 분할기 카운트가 1씩 증가하며, 누산기는 재설정 후 카운팅을 다시 시작하게 됩니다. 분할기 설정이 늘어나면 출력 주파수가 바뀌어 누적된 위상 오프셋 오류가 발생합니다. 위상 오류 추적은 펄스 값을 시간 함수로 추정한 것을 나타냅니다.

평균 분할기 설정은 4.25지만 합성기 출력은 위상 변조되어 출력에서 스퓨리어스 톤을 발생시킵니다. 누산기 상태를 확인하면 위상 오류를 추적한다는 것을 확실히 알 수 있으며, 그림 5에서 볼 수 있듯이 변조를 제거하기 위해 이를 사용할 수 있습니다.

그림 5: 실수형 N 디더링으로 인한 위상 변조를 해제하기 위해 D/A 변환된 누산기 상태 사용하기. (이미지 출처: DigiKey)

그림 5: 실수형 N 디더링으로 인한 위상 변조를 해제하기 위해 D/A 변환된 누산기 상태 사용하기. (이미지 출처: DigiKey)

누산기 상태는 디지털-아날로그(D/A) 컨버터에 의해 아날로그로 변환되고 위상 주파수 감지기 출력으로부터 조정되고 감해져, 실수형 N 디더링으로 인한 위상 변조를 해제합니다. 이를 위해서는 매우 세심한 주의가 요구되는데, 보정 신호가 위상 오류와 정확히 일치하지 않을 경우 출력에서 스퓨리어스 톤이 발생하기 때문입니다.

델타 시그마 변조기 입력

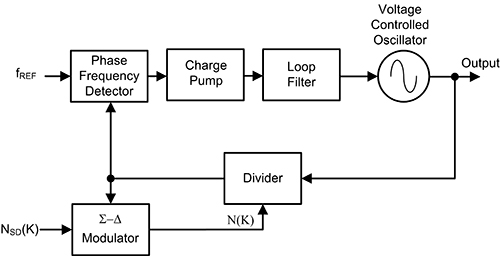

합성기에서 스퓨리어스 출력이 발생하는 이유는 누산기의 주기성때문입니다. 누산기를 시그마 델타 변조기로 대체하는 경우, 스퓨리어스 응답 및 잡음을 최소화하는 방법으로 분할기 카운트를 변조하기 위해 디지털 기술이 활용될 수 있습니다. 그림 6에서 이를 확인할 수 있습니다.

그림 6: 누산기를 시그마 델타 변조기로 대체하는 경우, 스퓨리어스 응답을 줄이는 방법으로 분할기 카운트를 조정하기 위해 디지털 기술이 활용될 수 있습니다. (이미지 출처: DigiKey)

그림 6: 누산기를 시그마 델타 변조기로 대체하는 경우, 스퓨리어스 응답을 줄이는 방법으로 분할기 카운트를 조정하기 위해 디지털 기술이 활용될 수 있습니다. (이미지 출처: DigiKey)

시그마 델타 변조 토폴로지에는 두 가지의 매우 일반적인 디지털 기술이 활용됩니다. 첫 번째 기술은 평균 분할 계수가 원하는 실수형 분할 값을 생성하도록 더 넓은 범위의 값에 걸쳐 N 분할기 카운트를 늘리는 것입니다. 그러면 기본 실수형 스퍼스가 감소됩니다. 누산기 기반 합성기는 두 상태 간에 카운트를 바꿉니다. 이것이 1차 변조 방법입니다. n차 시그마 델타 실수형 PLL은 2n개의 서로 다른 값 사이에서 N 카운터를 변조합니다. 예를 들어 3차 변조기는 8개의 다른 분할기 값 사이를 오가며, 4차 변조기는 16개의 다른 분할기 값 사이를 오갑니다.

두 번째 디지털 기술(디더링이라고도 함)은 의사 난수가 되도록 2N 시퀀스를 무작위화하는 것입니다. 평균 실수형 분할기 비율은 유지하면서도 PLL에 의해 필터링될 수 있는 방식으로 실수형 스퍼스를 모양을 갖춘 랜덤 잡음으로 변환합니다.

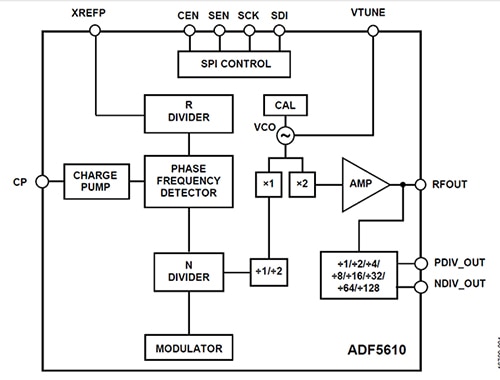

델타 시그마 실수형 N 합성기의 상업용 버전으로는 통합형 VCO를 갖춘 저잡음 0.57MHz ~ 14.6GHz 실수형 N 합성기인 Analog Devices의 ADF5610BCCZ가 있습니다(그림 7).

그림 7: 실수형 N 또는 정수형 합성기 구성을 모두 지원하는 Analog Devices ADF5610BCCZ 제품 구성도 (이미지 출처: Analog Devices)

그림 7: 실수형 N 또는 정수형 합성기 구성을 모두 지원하는 Analog Devices ADF5610BCCZ 제품 구성도 (이미지 출처: Analog Devices)

ADF5610은 외부 기준 발진기 및 루프 필터가 필요합니다. 기본 주파수가 3,650MHz ~ 7,300MHz 인 VCO가 내장되어 있습니다. 이 주파수는 내부적으로 두 배로 확장되어 RFOUT 핀으로 라우팅됩니다. 차동 출력을 통해 두 배로 확장된 VCO 주파수를 1, 2, 4, 8, 16, 32, 64 또는 128로 나눔으로써, 57MHz의 낮은 RF 출력 주파수를 생성할 수 있습니다.

ADF5610은 매우 낮은 스퓨리어스 수준을 달성하는 24비트 실수형 계수가 포함된 고급 시그마 델타 변조기를 사용합니다. 이 장치는 시그마 델타 변조기를 사용하는 모든 합성기에서와 마찬가지로 디지털 신호 처리 기술을 사용하여 원하는 평균 실수형 분할기 비율을 찾아냅니다. 이러한 과정은 PFD율에 클록되며, 고역 통과 주파수 응답과 함께 양자화 잡음으로 불리는 출력 변조 잡음을 생성합니다. 외부 저역 통과 루프 필터가 이 양자화 잡음을 VCO의 위상 잡음 수준 미만으로 필터링하는 데 사용되어, 이러한 잡음으로 인해 시스템의 전체 위상 잡음이 심해지는 것을 방지합니다.

ADF5610에는 0Hz 주파수 오류에 대한 정확한 주파수 모드도 포함되어 있습니다. 이 모드는 전체 24비트 위상 누산기 계수를 계속 사용하면서, 인접한 정수형 N 경계 스텝 사이의 정확한 주파수를 생성할 수 있습니다. 높은 위상 검파기 비교율을 통해 정확한 주파수 스텝을 달성하여 PLL이 이 모드에서 우수한 위상 잡음 및 스퓨리어스 성능을 유지할 수 있도록 합니다.

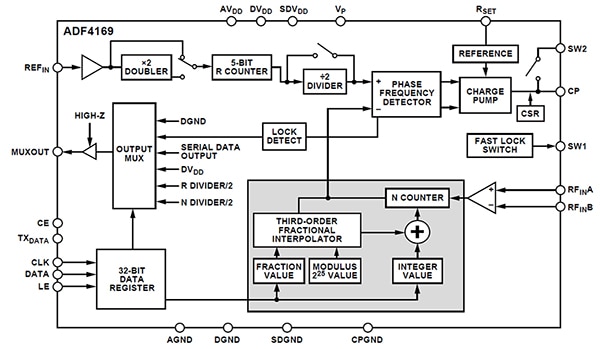

Analog Devices ADF4169CCPZ-RL7은 정수형 N 또는 실수형 N 장치 중 어느 것으로도 구성될 수 있는 또 다른 PLL 합성기입니다. 변조 및 파형 생성과 함께 최대 13.5GHz의 RF 대역폭에서 작동합니다. 외부 기준 주파수 입력, VCO 및 루프 필터를 사용합니다. 이 장치에는 분수형 N 합성을 위한 3차 시그마 델타 변조기가 있는데, 이 변조기는 비활성화될 수 있으므로 정수형 N 모드로 실행될 수 있습니다(그림 8).

그림 8: Analog Devices ADF4169CCPZ-RL7은 3차 델타 시그마 변조기를 사용합니다. (이미지 출처: Analog Devices)

그림 8: Analog Devices ADF4169CCPZ-RL7은 3차 델타 시그마 변조기를 사용합니다. (이미지 출처: Analog Devices)

ADF4158WCCPZ-RL7 합성기는 주파수 변조 지속파(FMCW) 레이더에서의 사용을 위해 설계되었습니다. 주파수축에서 톱니 및 삼각형 램프를 포함한 다양한 형태의 변조된 파형을 생성할 수 있습니다. 이는 레이더 응용 제품에서 필요한 특별한 기능입니다.

결론

고속 직렬 통신 버스의 데이터 전송률이 증가함에 따라, 설계자는 시스템 클록 솔루션을 위해 3GHz 미만에서 가장 잘 작동하는 직접 디지털 합성기보다 더 효과적인 방법을 찾아야만 합니다. 정수형 N 및 실수형 N 토폴로지를 사용하는 PLL 기반 주파수 합성기는 고주파수 클록, 직렬 데이터 통신 및 최대 수십 기가헤르츠의 주파수를 요구하는 레이더 응용 제품을 위한 안정적인 저잡음 신호를 제공합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.