대수 증폭기의 기초 사항 및 대수 증폭기에서 넓은 작동 범위 신호를 처리하는 방법

DigiKey 북미 편집자 제공

2019-03-21

높은 작동 범위 신호로 작업하는 설계자에게는 중요한 문제가 발생합니다. 진폭 변화가 100dB을 초과하는 신호를 60dB ~ 100dB의 일반 작동 범위를 가진 선형 증폭기 또는 아날로그 디지털 컨버터(ADC)에 적용하려면 어떻게 해야 할까요? 이러한 신호는 레이더, 수중 음파 탐지기, 통신 시스템과 같은 에코 거리 측정 장치와 광섬유 시스템에서 발생합니다. 그런 시스템에서는 낮은 진폭 신호를 위한 높은 이득과 높은 진폭 신호를 위한 낮은 이득이 필요합니다.

이러한 신호를 동적으로 조정하여 진폭 범위가 낮은 쪽에서는 신호 손실을 방지하면서 높은 쪽에서는 신호 손실을 제한하거나 클리핑할 방법이 있을까요?

대수 컨버터 또는 간단히 로그 앰프라고도 하는 대수 증폭기는 낮은 수준 신호에 높은 이득을 제공하고 신호 수준이 높아질수록 더 낮은 이득을 제공하여 이러한 문제를 해결합니다.

이 기사에서는 저주파 응용 분야와 고주파 응용 분야 모두에 적합한 다양한 유형의 로그 증폭기를 소개하고 설명합니다. 그런 다음 이러한 유용한 비선형 증폭기의 사양과 일반적인 응용 분야를 설명합니다.

대수 증폭기로 수행하는 작업

로그 앰프는 입력 신호의 대수이거나 신호의 엔벨로프인 출력을 생성하는 비선형 아날로그 증폭기입니다. 이 증폭기는 작동 범위가 큰 입력 신호를 고정 진폭 범위를 가진 출력 신호로 압축합니다. 이를 위해 낮은 입력 신호 수준에 높은 이득을 제공하고 더 높은 수준 신호에 점점 낮아지는 이득을 제공합니다(그림 1).

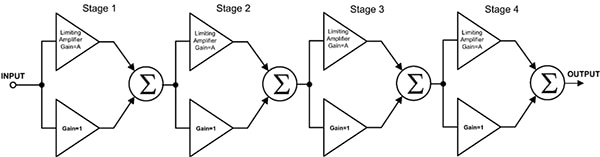

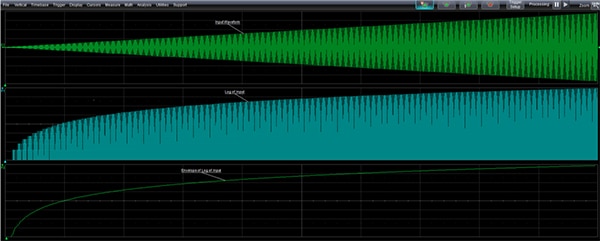

그림 1: 로그 앰프는 가장 낮은 진폭 신호에 더 높은 이득을 제공하고 신호 수준이 높아질수록 더 낮은 이득을 적용하여 입력 신호(상단 트레이스)를 압축합니다. 중간 트레이스는 입력 로그를 보여주고 하단 트레이스는 로그 앰프 출력의 엔벨로프를 나타냅니다. (이미지 출처: DigiKey)

입력 신호(상단 트레이스)는 진폭 변조 캐리어입니다. 변조 신호는 선형 램프입니다. 로그 증폭기 출력(중간 트레이스)은 낮은 수준 신호에 더 높은 이득을 제공하고 신호 수준이 높아질수록 더 낮은 이득을 제공하여 대수 가중치를 적용한 출력 신호를 생성합니다. 하단 트레이스는 검출기 형태의 로그 앰프를 위한 출력 옵션인 로그 앰프 출력의 엔벨로프입니다. ADC 앞에 적용된 로그 앰프는 입력 신호를 ADC의 고정 입력 범위에 맞게 압축합니다.

로그 앰프 토폴로지

다중 스테이지 로그 증폭기와 DC 로그 증폭기라는 두 가지 로그 앰프 토폴로지가 있습니다. 다중 스테이지 로그 증폭기는 일련의 증폭기에서 순차적 제한에 의존합니다. 이 토폴로지는 기가헤르츠 단위 이하의 고주파 신호에 가장 널리 사용되며 일반적으로 레이더와 통신 응용 분야에서 찾을 수 있습니다.

DC 로그 증폭기는 연산 증폭기(op amp)의 피드백 루프에서 다이오드 또는 다이오드 연결 트랜지스터를 사용합니다. 이 유형의 로그 앰프는 20MHz 이하의 주파수로 제한됩니다. 이 기술을 사용하는 로그 앰프는 일반적으로 제어 응용 분야의 센서에 사용됩니다.

다중 스테이지 로그 앰프

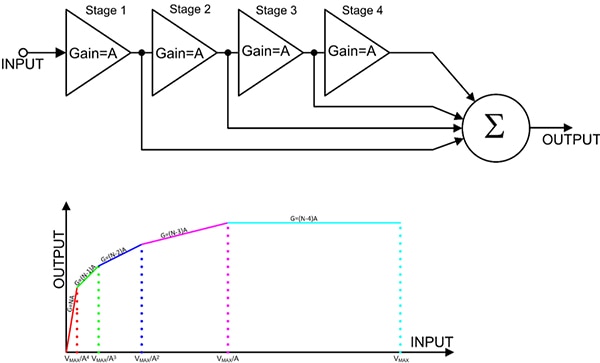

다중 스테이지 로그 앰프에서는 정상 작동하는 과부하 제한 특성, 다음 스테이지를 구동하는 각각의 출력, 가산 회로 등을 갖춘 일련의 선형 증폭기를 사용하여 대수 진폭 응답을 제공합니다(그림 2).

그림 2: 개별 출력이 합산되는 다중 선형 증폭기를 직렬로 연결하는 개념적으로 단순한 모델을 보여줍니다(위쪽). 이 접근 방식에서는 전달 함수 플롯으로 표시되는 대수 진폭 응답을 생성합니다(아래쪽). (이미지 출처: DigiKey)

그림 2에 표시된 증폭기 열에서는 동일한 이득(A)을 가진 증폭기 4개를 사용합니다. 모든 스테이지에서 제한을 유발하는 수준보다 낮은 진폭 신호는 N × A(이 경우 4 × A)의 이득을 생성합니다. 이는 그림 아래쪽에 전달 함수로 표시됩니다. 여기서 맨 왼쪽(빨간색) 선분은 0과 VMAX /A4 사이의 진폭에 대한 선분의 기울기로 표시되는 N X A에 해당하는 이득을 가집니다. 여기서 VMAX는 최대 입력 전압입니다.

입력 수준이 높아지면 일부 지점에서 마지막 증폭기 즉, 스테이지 4가 제한되기 시작합니다. 그러면 전체 이득이 (N - 1) × A 또는 3 × A로 떨어집니다. 입력 수준 VMAX /A3과 VMAX /A4 사이에 있는 녹색 선분의 기울기는 이 이득 범위를 나타냅니다. 마찬가지로 입력 수준이 지속적으로 증가하면서 이전 스테이지 증폭기가 제한되기 시작합니다. 어두운 파란색 선분의 이득은 (N - 2) × A이고, 자홍색 선분의 이득은 (N - 3) × A이고, 연한 파란색 선분의 이득은 (N - 4) × A 또는 0입니다.

이 개념 모델은 일련의 증폭기를 사용하여 대수 응답을 개발하는 방법을 설명하는 데 유용하지만 아쉬운 점이 하나 있었습니다. 각 증폭기 스테이지에 고유한 전파 지연이 있습니다. 첫 번째 스테이지의 신호 구성 요소가 이후 스테이지의 신호 구성 요소보다 먼저 가산 회로에 도달하여 출력 파형을 왜곡합니다. 기본 회로를 변경하면 이 문제를 해결할 수 있습니다(그림 3).

그림 3: 증폭기를 쌍으로 사용하는 계단식 아키텍처를 통해 계열 로그 증폭기 토폴로지를 수정하여 지연을 제거할 수 있습니다. 각 쌍은 필요 시 이득을 제공하는 제한 증폭기와 증폭이 필요하지 않을 때 사용되는 단위 이득 버퍼로 구성됩니다. 스테이지마다 합산을 통해 지연을 제거합니다. (이미지 출처: DigiKey)

이 토폴로지는 단일 스테이지 증폭기를 증폭기 쌍으로 대체합니다. 각 쌍은 필요 시 이득을 제공하는 제한 증폭기와 이득이 필요하지 않은 경우의 단위 이득 버퍼로 구성됩니다. 스테이지마다 합산하여 단일 가산기를 사용할 때 발생하는 지연을 제거합니다. 작은 신호를 위해서는, 제한 증폭기가 우세한 경로를 제공합니다. 신호 진폭이 증가하면 마지막 스테이지가 제한되기 시작하여 해당 스테이지의 단위 이득 증폭기가 가산기에 우세한 입력으로 작용합니다. 입력 수준이 더 증가하면 이전 스테이지가 차례로 제한되어 전체적으로 낮은 이득이 제공됩니다.

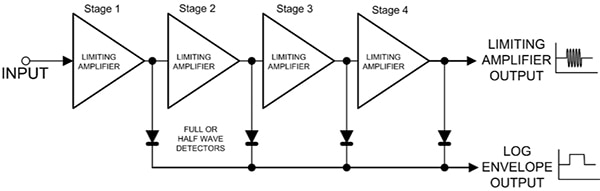

연속 감지 로그 앰프는 계열 증폭기 토폴로지의 변형입니다(그림 4).

그림 4: 연속 감지 로그 앰프는 각 스테이지 이후에 피크 감지를 추가합니다. 그런 다음 출력을 합산하여 로그 증폭 출력 신호의 진폭 엔벨로프를 생성합니다. (이미지 출처: DigiKey)

연속 감지 로그 앰프는 앞에서 설명한 것과 동일한 제한 증폭기 체인을 사용하지만 각 스테이지 이후에 피크 감지를 추가합니다. 그런 다음 검출기 출력을 합산하여 로그 앰프 출력의 진폭 엔벨로프를 생성합니다. 일부 버전에서는 로그 증폭 신호도 출력합니다. 회로 설계에 따라 검출기를 반파장 또는 전파장으로 구현할 수 있습니다. 로그 엔벨로프는 감지된 신호 수준을 추출해야 하는 응용 제품에 유용합니다. 그런 응용 제품으로는 자동 이득 제어기, 수신기 신호 강도 표시기(RSSI)가 있습니다.

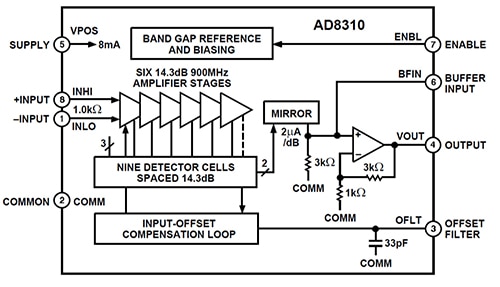

상업용 다중 스테이지 복조 로그 앰프의 좋은 예로는 Analog Devices의 AD8310ARMZ-REEL7이 있습니다(그림 5).

그림 5: AD8310 다중 스테이지 복조 로그 앰프는 각 공칭 이득이 14.3dB(이득 5.2)이고 대역폭이 900MHz인 증폭기 6개를 계단식으로 배열합니다. (이미지 출처: Analog Devices)

AD8310에서는 440MHz 대역폭에서 작동 범위가 95dB이고 ±0.4dB의 로그 선형성을 가진 차동 입력을 제공합니다. 이 앰프는 각 공칭 이득이 14.3dB(이득 5.2)이고 대역폭이 900MHz인 증폭기 6개를 계단식으로 배열합니다. 각 증폭기는 내부 버퍼 증폭기를 통해 전류 출력을 전압으로 변환한 후 출력하는 검출기를 구동합니다.

DC 로그 증폭기

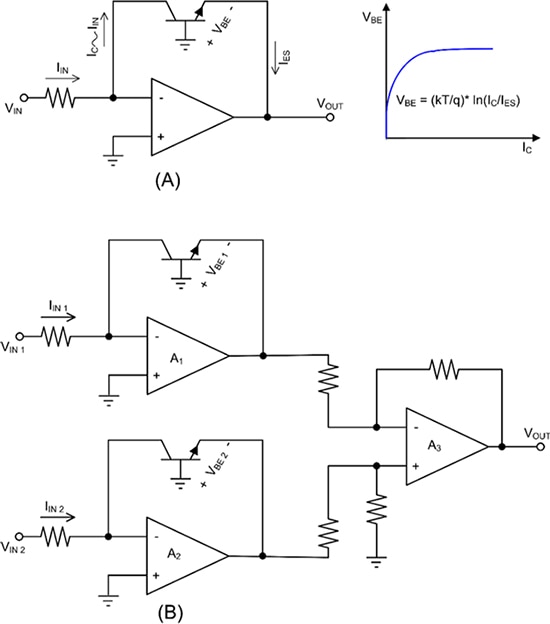

앞서 설명한 대로 DC 로그 앰프는 로그 앰프 토폴로지를 대체할 수 있습니다. DC 로그 앰프는 연산 증폭기의 피드백 경로에서 다이오드 또는 다이오드 연결 트랜지스터를 사용합니다. 다이오드 연결 트랜지스터가 가장 일반적으로 사용되는 구성입니다(그림 6A). 트랜지스터 기저 방출기 접합부를 통과하는 전압은 해당 접합부를 통과하는 전류의 대수에 비례합니다. 연산 증폭기의 피드백 경로에 있는 다이오드 연결 트랜지스터로 인해 방출기 침투 전류에 대한 입력 전류의 비율 대수(IES)에 비례하는 출력 전압이 생성됩니다.

그림 6: 연산 증폭기의 피드백 경로에서 다이오드 연결 트랜지스터를 사용하여 로그 증폭기를 구현할 수 있습니다(A). 서로 다르게 연결된 두 앰프를 사용하여 이 유형 로그 앰프의 온도 종속성을 크게 줄일 수 있습니다(B). (이미지 출처: DigiKey)

그림 6(A)에 표시된 간단한 구성에서는 출력이 방정식에 표시된 대로 온도에 종속되도록 제한합니다. 여기서 T는 침투 방출기 전류 IES로 곱한 캘빈 온도입니다. 그림 6(B)에 표시된 대로 두 증폭기를 차동 회로로 구성하여 이 종속성을 크게 완화할 수 있습니다. 차동 버전은 IIN 2/IIN 1의 비율 로그를 계산하고 전압 출력을 갖는 트랜스 임피던스 증폭기입니다. IIN 1은 일반적으로 고정 레퍼런스 전류로 설정됩니다.

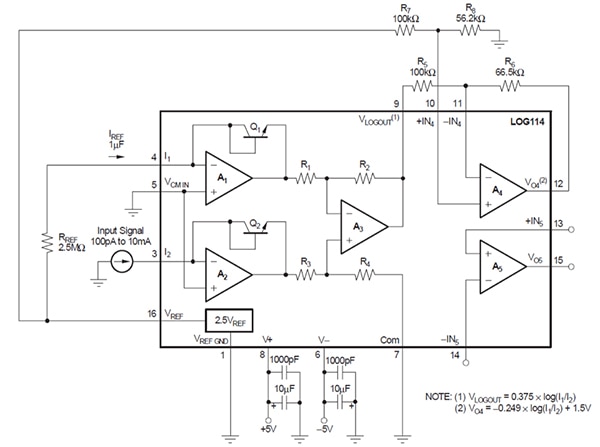

Texas Instruments의 LOG114AIRGVT는 대역폭이 5MHz이고 작동 범위가 최대 80개인 DC 로그 앰프입니다. 로그 앰프 또는 로그 비율 앰프로 구성될 수 있습니다. 온도 보정 로그 증폭기 이외에 비율 조정 연산 증폭기 두 개와 2.5V 전압 레퍼런스 소스를 포함합니다(그림 7).

그림 7: LOG114 로그 증폭기의 기능별 제품 구성도 및 연결된 외부 구성 요소 이 증폭기는 온도 보정 회로를 기반으로 하며 추가 비율 조정 증폭기 두 개를 포함합니다. (이미지 출처: Texas Instruments)

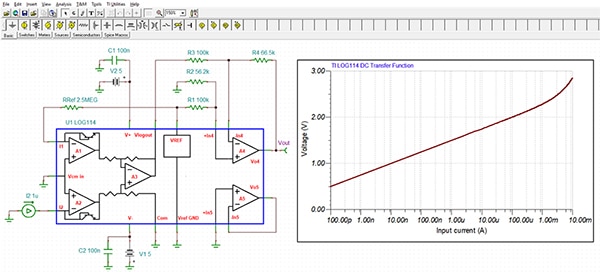

Texas Instruments는 설계자가 TINA-TI Texas Instruments의 회로 시뮬레이터에서 설계를 시뮬레이션할 수 있도록 LOG114용 회로 모델을 제공합니다(그림 8).

그림 8: LOG114 로그 앰프 모델의 TINA-TI 시뮬레이션은 70개 이상의 입력 전류에서 탁월한 로그 선형성을 보여줍니다. (이미지 출처: DigiKey)

이 회로에서는 내장된 2.5V 전압 레퍼런스를 사용하여 1 µA에서 I1 레퍼런스 전류를 생성합니다. 해당 전달 함수는 100pA ~ 1mA 및 140dB 전류 범위에서 70개 이상의 선형 응답을 보여줍니다. 추가 연산 증폭기 두 개 중 하나로 로그 앰프 출력을 조정하여 전달 함수 방정식 VOUT = -0.249 x log(I1/I2) + 1.5V를 생성합니다.

결론

로그 증폭기는 기저대역 또는 RF와 상관없이 설계자에게 넓은 작동 범위 신호를 처리할 수 있는 기술을 제공합니다. 넓은 작동 범위 신호를 고정 출력 범위로 압축하고 다음 스테이지에서 오버플로 및 클리핑 조건을 방지하면 됩니다. 로그 앰프 솔루션은 즉시 사용 가능하며 온라인 시뮬레이션 도구에서 널리 지원되므로 설계 공정에 유용합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.