제로 드리프트 연산 증폭기를 사용하여 정밀하고 정확한 저전력 산업 시스템 제어를 달성하는 방법

DigiKey 북미 편집자 제공

2020-10-22

산업 시스템이 점차적으로 기계 제어에서 전자 제어로 이동함에 따라 제조업체는 제품 품질과 작업자 안전 모두에서 이득을 보고 있습니다. 작업자 안전의 경우 주로 작업자가 열악한 환경으로부터 더 많이 보호되기 때문입니다. 그러나 신호 조정이 산업 기계의 작동 수명에 걸쳐 안정적이고 정밀하며 정확한 제어를 제공하는 데 필요한 회로 안정성과 감도를 유지하는 데 매우 중요한 이유는 극한 온도뿐만 아니라 전기적 잡음 및 전자기 간섭(EMI)이있는 가혹한 환경 때문입니다.

신호 조정 체인의 중요한 구성요소는 필요한 신호를 수집하고 증폭하는 데 사용되는 고이득 DC 차동 증폭기인 연산 증폭기(op-amp)입니다. 표준 연산 증폭기는 온도 드리프트에 민감하며 정밀도와 정확도가 제한적입니다. 따라서 산업 요구 사항을 충족하기 위해 설계자는 특정 형태의 시스템 수준 자동 보정을 추가합니다. 문제는 이러한 보정 기능은 복잡하여 구현하기 어려울 수 있고 전력 소비를 증가시킨다는 것입니다. 또한 더 많은 기판 공간을 요구하고 비용과 설계 시간이 늘어납니다.

이 기사에서는 산업 응용 제품의 신호 조정 요구 사항과 설계자들이 고려해야 할 사항에 대해 살펴봅니다. 그런 다음 ON Semiconductor의 고성능 제로 드리프트 연산 증폭기 솔루션을 소개하고 산업 신호 조정 요구 사항을 충족하기 위해 이러한 솔루션을 사용하는 이유와 그 방법을 소개합니다. 또한 높은 공통 모드 제거비(CMRR), 높은 전원 공급 제거비(PSRR), 높은 개방 루프 이득과 같이 이러한 장치의 다른 주요 특성도 검토합니다.

산업용 신호 조정 응용 제품

로우사이드 전류 감지 및 센서 인터페이스는 산업용 시스템에서 종종 사용됩니다. 이러한 회로와 연결된 매우 작은 차동 신호로 인해 설계자는 고정확도 연산 증폭기를 필요로 합니다.

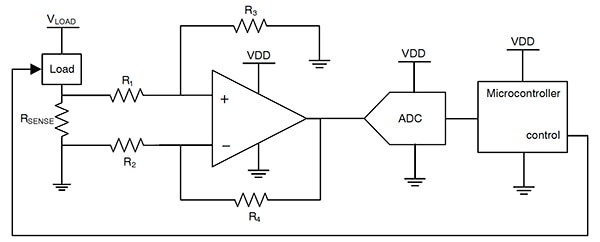

로우사이드 전류 감지 기능은 과전류 조건을 감지하는 데 사용되며 대개 피드백 제어에 사용됩니다(그림 1). 낮은 값 감지 저항기(<100밀리옴(mΩ))가 부하와 접지에 직렬로 배치되어 있습니다. 저항기의 낮은 값은 전력 손실과 열 생성을 줄이지만 그에 상응하여 전압 강하도 작습니다. 정밀 제로 드리프트 연산 증폭기를 사용하면 외부 저항기 R1, R2, R3, R4(여기서 R1 = R2, R3 = R4)로 설정된 이득으로 감지 저항기에 걸쳐 전압 강하를 증폭할 수 있습니다. 높은 정확도를 위해 정밀 저항기가 필요하며, 최고의 분해능을 위해 아날로그-디지털 컨버터(ADC)의 전체 범위를 활용하도록 이득이 설정됩니다.

그림 1: 감지 저항기와 ADC 간 연산 증폭기 인터페이스를 보여주는 로우사이드 전류 감지. (이미지 출처: ON Semiconductor)

그림 1: 감지 저항기와 ADC 간 연산 증폭기 인터페이스를 보여주는 로우사이드 전류 감지. (이미지 출처: ON Semiconductor)

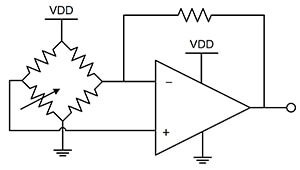

산업용 및 계측 시스템의 스트레인, 압력, 온도를 측정하는 데 사용되는 센서는 대개 휘스톤 브리지 구성으로 제공됩니다(그림 2). 측정값을 제공하는 센서 전압 변화는 아주 작을 수 있으며 ADC로 이동하기 전에 증폭되어야 합니다. 정밀 제로 드리프트 연산 증폭기는 높은 이득, 낮은 잡음 및 낮은 오프셋 전압 덕분에 대개 이러한 응용 분야에 사용됩니다.

그림 2: 정밀 연산 증폭기는 대개 휘스톤 브리지와 함께 사용되어 센서의 신호를 ADC로 보내기 전에 스트레인, 압력, 온도에 대한 센서 신호를 증폭합니다. (이미지 출처: ON Semiconductor)

그림 2: 정밀 연산 증폭기는 대개 휘스톤 브리지와 함께 사용되어 센서의 신호를 ADC로 보내기 전에 스트레인, 압력, 온도에 대한 센서 신호를 증폭합니다. (이미지 출처: ON Semiconductor)

정밀 연산 증폭기의 주요 파라미터

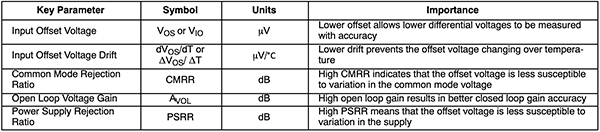

오프셋 전압, 오프셋 전압 드리프트, 잡음에 대한 민감성, 개방 루프 전압 이득은 전류 감지 및 센서 인터페이스 응용 제품의 연산 증폭기 성능을 제한하는 주요 파라미터입니다(표 1).

표 1: 정확도 및 정밀도에 영향을 주는 정밀 연산 증폭기의 주요 파라미터. (이미지 출처: ON Semiconductor)

표 1: 정확도 및 정밀도에 영향을 주는 정밀 연산 증폭기의 주요 파라미터. (이미지 출처: ON Semiconductor)

입력 오프셋 전압(제조업체에 따라 VOS 또는 VIO로 표시)은 반도체 제조 공정의 결함에서 유래하며 이러한 결함은 VIN+와 VIN- 간 차동 전압을 일으킵니다. 부품 간 변동은 온도에 걸쳐 달라질 수 있고 포지티브 또는 네거티브일 수 있으므로 보정이 어렵습니다. 표준 연산 증폭기의 오프셋 또는 드리프트를 줄이려는 설계자의 노력은 복잡성을 더할 뿐만 아니라 경우에 따라 전력 소비를 늘릴 수도 있습니다.

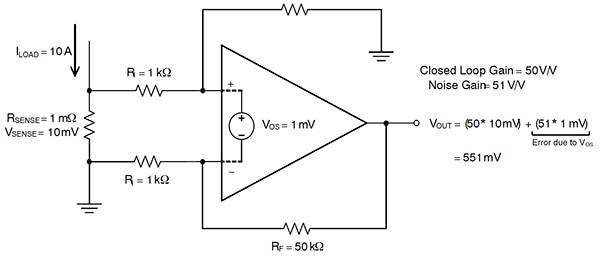

예를 들어, 차동 증폭기 구성에서 연산 증폭기를 사용하는 전류 감지를 생각해 보겠습니다(그림 3).

그림 3: 차동 증폭기 구성에서 연산 증폭기를 사용하는 전류 감지. 입력 오프셋 전압은 잡음 이득에 의해 증폭되어 출력에서 오프셋 오차를 생성하므로(“Error due to VOS”로 표시됨) 낮은 오프셋 전압은 대단히 중요합니다. (이미지 출처: ON Semiconductor)

그림 3: 차동 증폭기 구성에서 연산 증폭기를 사용하는 전류 감지. 입력 오프셋 전압은 잡음 이득에 의해 증폭되어 출력에서 오프셋 오차를 생성하므로(“Error due to VOS”로 표시됨) 낮은 오프셋 전압은 대단히 중요합니다. (이미지 출처: ON Semiconductor)

출력 전압은 방정식 1에 표시된 대로 신호 이득 항(VSENSE)과 잡음 이득 항(VOS)의 합계입니다.

![VOUT = (VSENSE x RF/R1) + (VOS x [1 + RF/R1]) 방정식 1](http://sc-a.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2020/October/How%20to%20Use%20Zero-Drift%20Op%20Amps%20to%20Achieve%20Industrial%20System%20Control/article-2002october-how-touse-zero-drift-equation1.jpg?la=en&ts=41c863e8-cf99-46af-9354-34a51ce4a00a) 방정식 1

방정식 1

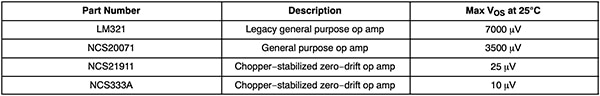

내부 연산 증폭기 파라미터인 입력 오프셋 전압은 신호 이득이 아니라 잡음 이득이 곱해지므로 출력 오프셋 오차(그림 2의 “Error due to VOS”)가 제공됩니다. 정밀 연산 증폭기는 다양한 기법을 사용하여 가능한 한 오프셋 전압을 최소화합니다. 제로 드리프트 연산 증폭기에서 이는 특히 저주파 및 DC 신호에 적용됩니다. 정밀 제로 드리프트 연산 증폭기의 오프셋 전압은 범용 연산 증폭기에 비해 두 배 이상 낮을 수 있습니다(표 2).

표 2: 선택한 범용 연산 증폭기와 초퍼 안정화 제로 드리프트 연산 증폭기의 최대 오프셋 전압 비교에서 정밀 제로 드리프트 연산 증폭기의 오프셋 전압이 두 배 이상 낮을 수 있습니다. (이미지 출처: ON Semiconductor)

표 2: 선택한 범용 연산 증폭기와 초퍼 안정화 제로 드리프트 연산 증폭기의 최대 오프셋 전압 비교에서 정밀 제로 드리프트 연산 증폭기의 오프셋 전압이 두 배 이상 낮을 수 있습니다. (이미지 출처: ON Semiconductor)

제로 드리프트 연산 증폭기

이러한 향상된 성능 덕분에 설계자는 제로 드리프트 연산 증폭기를 사용하여 산업 응용 제품의 신호 조정 요구 사항을 충족할 수 있습니다. 서로 다른 성능 레벨을 제공하는 제로 드리프트 연산 증폭기의 두 예로 ON Semiconductor의 NCS325SN2T1G와 NCS333ASN2T1G가 있습니다. 설계자는 정밀 응용 제품을 위해 50마이크로볼트(µV) 오프셋과 0.25µV/°C 드리프트의 혜택을 누릴 수 있는 NCS325SN2T1G 장치를 사용할 수 있으며, NCS333ASN2T1G 제품군은 10µV 오프셋과 0.07µV/°C에 불과한 드리프트를 제공하여 가장 까다로운 고정밀 응용 제품에 적합합니다. 이러한 두 연산 증폭기는 서로 다른 내부 아키텍처를 사용하여 제로 드리프트를 달성합니다.

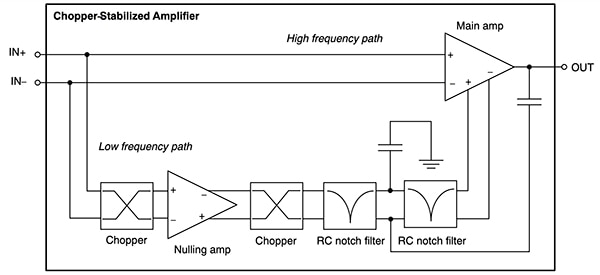

NCS333ASN2T1G는 초퍼 안정화 아키텍처를 사용하여 온도와 시간에 걸쳐 오프셋 전압 드리프트의 이점을 제공합니다(그림 4). 전형적인 초퍼 아키텍처와 달리, 초퍼 안정화 아키텍처에는 두 개의 신호 경로가 있습니다.

그림 4: NCS333ASN2T1G에는 두 개의 신호 경로가 있습니다. 두 번째 경로(아래)는 입력 오프셋 전압을 샘플링하며 출력에서 오프셋을 수정하는 데 사용됩니다. (이미지 출처: ON Semiconductor)

그림 4: NCS333ASN2T1G에는 두 개의 신호 경로가 있습니다. 두 번째 경로(아래)는 입력 오프셋 전압을 샘플링하며 출력에서 오프셋을 수정하는 데 사용됩니다. (이미지 출처: ON Semiconductor)

그림 4에서 하부 신호 경로는 초퍼가 입력 오프셋 전압을 샘플링하는 위치입니다. 그런 다음 출력에서 오프셋을 수정하는 데 사용됩니다. 오프셋 수정은 125킬로헤르츠(kHz)에서 수행됩니다. 초퍼 안정화 아키텍처는 관련된 나이퀴스트 주파수(최대) 주파수에서 최고의 성능을 위해 최적화됩니다. 신호 주파수가 나이퀴스트 주파수 62.5kHz를 초과할 경우, 출력에서 에일리어싱이 발생할 수 있습니다. 이는 모든 초퍼 및 초퍼 안정화 아키텍처에 대한 내재적 제한입니다.

그러나, NCS333ASN2T1G 연산 증폭기는 최대 125kHz까지 최소한의 에일리어싱을, 최대 190kHz까지 낮은 에일리어싱을 제공합니다. ON Semiconductor의 고유한 접근 방식에서는 초퍼 주파수와 5차 고조파에 맞게 조정된, 종속적으로 연결된 두 개의 대칭적 저항기 커패시터(RC) 노치 필터를 사용하여 에일리어싱 효과를 줄입니다.

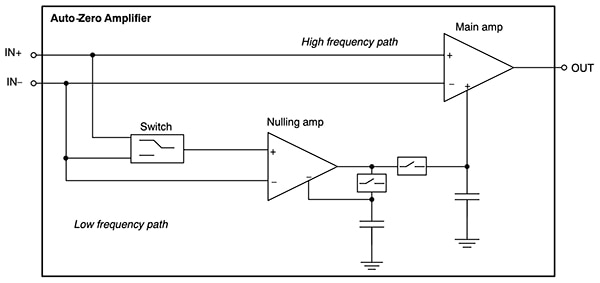

자동 제로 아키텍처

제로 드리프트 연산 증폭기에 대한 또 다른 접근 방식은 자동 제로 아키텍처입니다(그림 5). 자동 제로 설계에는 주 증폭기와 널링 증폭기가 포함되어 있습니다. 이 설계는 또한 클록형 시스템을 사용합니다. 첫 번째 위상에서, 스위치형 커패시터는 널링 증폭기 출력에 대한 이전 위상의 오프셋 오차를 유지합니다. 두 번째 위상에서는 널링 증폭기 출력의 오프셋을 사용하여 주 증폭기의 오프셋을 수정합니다. ON Semiconductor의 NCS325SN2T1G는 자동 제로 아키텍처를 사용하여 구축됩니다.

그림 5: 스위치형 커패시터를 보여주는 NCS325SN2T1G와 같은 자동 제로 연산 증폭기에 대한 간소화된 제품 구성도. (이미지 출처: ON Semiconductor)

그림 5: 스위치형 커패시터를 보여주는 NCS325SN2T1G와 같은 자동 제로 연산 증폭기에 대한 간소화된 제품 구성도. (이미지 출처: ON Semiconductor)

위에서 설명한 오프셋 전압과 드리프트 측면에서 NCS333ASN2T1G(초퍼 안정화 아키텍처)와 NCS325SN2T1G(자동 제로 안키텍처)의 차이 이외에, 서로 다른 이 두 아키텍처는 개방 루프 전압 이득, 잡음 성능, 에일리어싱 민감성에서의 차이를 생성합니다. NCS333ASN2T1G는 145데시벨(dB)의 개방 루프 전압 이득을 제공하고 NCS325SN2T1G는 114dB 개방 루프 전압 이득을 제공합니다. 잡음을 고려하여 NCS333ASN2T1G는 111dB의 CMRR과 130dB의 PSRR을 제공하고, NCS325SN2T1G는 108dB의 CMRR과 107dB의 PSRR을 제공합니다. 둘 모두 우수한 정격을 가지지만 NCS333ASN2T1G의 성능이 NCS325SN2T1G 보다 뛰어납니다.

NCS333ASN2T1G 계열 연산 증폭기는 또한 최소한의 에일리어싱을 가집니다. 이는 초퍼 주파수와 5차 고조파에 맞게 조정된, 종속적으로 연결된 두 개의 대칭적 RC 노치 필터를 사용하여 에일리어싱 효과를 줄이는 ON Semiconductor의 고유한 접근 방식 덕분입니다. 이론적으로, 자동 제로 아키텍처는 초퍼 안정화 유형보다 더 극적인 에일리어싱을 나타냅니다. 그러나 에일리어싱 효과는 크게 다를 수 있으며 지정되지 않는 경우도 있습니다. 이는 사용되는 특정 연산 증폭기의 에일리어싱 특성을 이해하는 설계자에 달려있습니다. 에일리어싱은 샘플링 증폭기의 결함이 아니라 동작입니다. 이러한 동작에 대한 이해와 이를 회피하는 방법을 통해 제로 드리프트 증폭기가 최적으로 작동하도록 할 수 있습니다.

마지막으로 연산 증폭기는 다양한 크기의 EMI 민감성을 제공합니다. 반도체 접합은 EMI 신호를 픽업 및 정류하여 출력에서 EMI 유도 전압 오프셋을 생성하고 총 오차에 다른 요소를 더할 수 있습니다. 입력 핀은 EMI에 가장 민감합니다. 고정밀 NCS333ASN2T1G 연산 증폭기는 저역 통과 필터를 통합하여 EMI에 대한 민감도를 줄입니다.

설계 및 레이아웃 고려 사항

최적의 연산 증폭기 성능을 보장하기 위해, 설계자는 올바른 pc 기판 설계 관행을 따라야 합니다. 고정밀 연산 증폭기는 민감한 장치입니다. 예를 들어, 0.1마이크로패럿(µF) 감결합 커패시터를 공급 핀에 최대한 가깝게 배치해야 합니다. 또한 션트를 연결할 때 회로 기판 트레이스가 동일한 길이, 동일한 크기여야 하며 가능한 짧아야 합니다. 연산 증폭기와 션트 저항기는 기판의 같은 측에 있어야 하며 가장 높은 수준의 정확도를 요구하는 응용 제품의 경우 4단자 션트(켈빈 션트라고도 함)를 사용해야 합니다. 이러한 통합 기술을 통해 EMI 민감도를 줄일 수 있습니다.

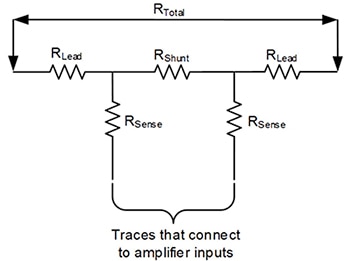

연결 시 항상 션트 제조업체의 권장 사항을 따르십시오. 부적절하게 연결될 경우 측정값에 원치 않는 표유 리드와 감지 저항이 추가되고 오차가 늘어날 수 있습니다(그림 6).

그림 6: 표유 저항(RLead 및 RSense)을 나타내는 2단자 션트 저항기에 대한 연결. (이미지 출처: ON Semiconductor)

그림 6: 표유 저항(RLead 및 RSense)을 나타내는 2단자 션트 저항기에 대한 연결. (이미지 출처: ON Semiconductor)

정확도는 입력 핀의 온도 종속적 오프셋 전압 변동의 영향을 받을 수 있습니다. 이러한 변동을 최소화하기 위해 설계자는 열전 계수가 낮은 금속을 사용하여 열원 또는 냉각 팬의 온도 변화를 방지해야 합니다.

결론

다양한 산업 응용 제품에서 정밀하고 정확한 신호 조정에 대한 요구가 늘어가고 있습니다. 이와 함께 저전력 콤팩트 솔루션에 대한 요구도 증대되고 있습니다. 연산 증폭기는 신호 조정에 중요한 구성 요소이지만, 설계자는 시간과 온도에 걸쳐 안정성을 보장하기 위해 자동 보정 기능과 다른 메커니즘을 추가해야 하므로 복잡성, 비용, 전력 소비가 늘어났습니다.

다행히도, 설계자는 시간과 온도에 걸쳐 연속적인 자동 보정 기능, 매우 낮은 오프셋 전압, 0에 가까운 드리프트를 제공하는 고성능 제로 드리프트 연산 증폭기를 사용할 수 있습니다. 이 증폭기는 또한 넓은 작동 범위에서 낮은 전력을 소비하고 콤팩트한 크기이며 높은 CMRR, 높은 PSRR, 높은 개방 루프 이득 및 산업 응용 제품을 위한 모든 주요 특성을 제공합니다.

권장 참고 자료

- Applying advanced sensors and algorithms for low-cost motion tracking(저비용 동작 추적을 위해 고급 센서 및 알고리즘 적용)

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.