FPGA 기본 사항 – 5부: Intel(Altera) FPGA 시작하기

DigiKey 북미 편집자 제공

2020-05-07

편집자 주: 최적의 처리 솔루션은 종종 RISC, CISC, 그래픽 프로세서 및 FPGA의 조합, FPGA 자체 또는 패브릭의 일부로 하드 프로세서 코어를 자랑하는 FPGA에 의해 제공됩니다. 하지만 많은 설계자들이 FPGA의 기능에 익숙하지 않고 그 진화 과정과 사용 방법을 잘 모릅니다. 여러 단원으로 구성된 이 시리즈의 1부에서는 FPGA를 자세히 소개하고, 2부에서는 Lattice Semiconductor의 FPGA 제품을 중점적으로 살펴보고, 3부에서는 Microchip Technology가 계열사 Microsemi Corporation을 통해 제공하는 FPGA 장치 제품군과 설계 도구를 중심으로 살펴보았습니다. 4부에서는 Xilinx의 부품 및 도구를 자세히 알아보았습니다. 이제 5부에서는 Intel에 인수되어 현재는 Intel의 Programmable Solutions Group(이하 Intel)으로 편입된 Altera의 제품을 살펴보겠습니다.

1부에서 설명한 대로 현장 프로그래밍 가능 게이트 어레이(FPGA)는 사용된 독립형 또는 이기종 아키텍처의 소중한 컴퓨팅 자산이 되는 많은 특성을 갖추고 있지만, 많은 설계자가 FPGA에 익숙하지 않고 이 장치를 설계에 통합하는 방법을 잘 모릅니다. 이 문제를 해결하는 한 가지 방법은 주요 벤더의 FPGA 아키텍처와 관련 도구를 자세히 살펴보는 것입니다.

상위 수준의 FPGA 옵션 개요

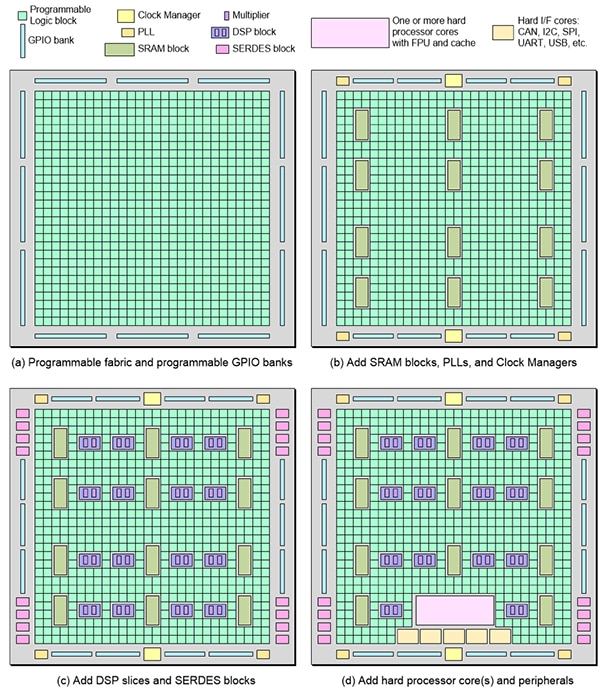

현재 다양한 유형의 FPGA가 출시되어 있고, 각 유형은 여러 기능이 다양한 형태로 조합되어 있습니다. FPGA의 중심에는 프로그래밍 가능 패브릭이 있습니다. 이는 프로그래밍 가능 논리 블록의 어레이로 표기되며 논리 소자(LE)라고도 합니다(그림 1(a)). FPGA 패브릭의 다음 승압에는 블록 RAM(BRAM)이라는 SRAM 블록과 위상 고정 루프(PLL), 클록 관리자가 포함됩니다(그림 1(b)). 디지털 신호 처리(DSP) 블록(DSP 슬라이스) 및 고속 직렬 변환기/직병렬 변환기(SERDES) 블록을 추가할 수도 있습니다(그림 1(c)).

그림 1: 가장 간단한 FPGA에는 프로그래밍 가능 패브릭과 구성 가능한 범용 IO(GPIO)만 포함되어 있고(a), 다른 아키텍처는 SRAM 블록, PLL 및 클록 관리자(b), DSP 블록 및 SERDES 인터페이스(c), 하드 프로세서 코어 및 주변 장치(d)로 이 기본 패브릭을 강화합니다. (이미지 출처: Max Maxfield)

그림 1: 가장 간단한 FPGA에는 프로그래밍 가능 패브릭과 구성 가능한 범용 IO(GPIO)만 포함되어 있고(a), 다른 아키텍처는 SRAM 블록, PLL 및 클록 관리자(b), DSP 블록 및 SERDES 인터페이스(c), 하드 프로세서 코어 및 주변 장치(d)로 이 기본 패브릭을 강화합니다. (이미지 출처: Max Maxfield)

프로그래밍 가능 패브릭에서 CAN, I2C, SPI, UART, USB와 같은 주변 장치 인터페이스 기능을 구현할 수 있지만, 대부분의 FPGA에서는 해당 기능이 실리콘에 하드 코어로 포함되어 있습니다. 마찬가지로 마이크로 프로세서를 프로그래밍 가능 패브릭에서 소프트 코어로 구현하거나 실리콘에서 하드 코어로 구현할 수 있습니다(그림 1(d)). 하드 프로세서 코어가 탑재된 FPGA를 SoC(시스템온칩) FPGA라고 합니다. FPGA마다 다른 시장 및 응용 분야를 대상으로 하는 다른 기능, 특징 및 용량 모음을 제공합니다.

Intel(Altera를 인수함), Efinix, Lattice Semiconductor, Microchip Technology(Atmel 및 Microsemi에 인수됨), Xilinx 등 많은 FPGA 벤더가 있습니다.

이러한 모든 벤더는 여러 FPGA 제품군을 현장에 배치하고 있습니다. 어떤 벤더는 SoC FPGA를 제공하고, 어떤 벤더는 인공 지능(AI) 및 머신 러닝(ML) 응용 분야를 대상으로 하는 장치를 제공하고, 또 어떤 벤더는 우주 응용 분야를 위한 방사선 내성 장치를 제공합니다. 서로 다른 다양한 제품군에 각각의 리소스를 제공하므로 작업에 가장 적합한 장치를 선택하는 것이 어려울 수 있습니다.

Intel FPGA 및 SoC FPGA 소개

Intel에서 제공하는 프로그래밍 가능 장치 제품의 성능과 기능은 적정 수준부터 최고 수준까지, 또한 기존 FPGA부터 SoC FPGA(예: FPGA 프로그래밍 가능 패브릭을 하나 이상의 강화된 프로세서 코어와 결합하는 장치)까지 다양합니다.

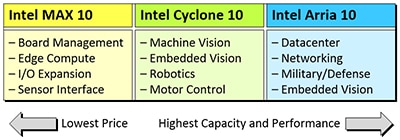

Intel은 Max 10, Cyclone 10, Arria 10을 포함하여 현재 제품 포트폴리오에 5개의 활성 FPGA 제품군이 있습니다(그림 2). 또한 Intel은 최고 사양의 하이엔드 Stratix 10과 최신 Agilex 장치를 갖추고 있습니다.

그림 2: 가장 경제적인 Max 10부터 최고 용량 최고 사양의 Arria 10까지 Intel의 5개 FPGA 제품군 중 3개 제품군의 대상 응용 분야와 시장은 기판 관리 및 I/O 확장부터 내장형 비전 및 군사/방위까지 다양합니다. Stratix 10 및 최신 Agilex 장치는 성능을 더욱 개선했습니다. (이미지 출처: Max Maxfield)

그림 2: 가장 경제적인 Max 10부터 최고 용량 최고 사양의 Arria 10까지 Intel의 5개 FPGA 제품군 중 3개 제품군의 대상 응용 분야와 시장은 기판 관리 및 I/O 확장부터 내장형 비전 및 군사/방위까지 다양합니다. Stratix 10 및 최신 Agilex 장치는 성능을 더욱 개선했습니다. (이미지 출처: Max Maxfield)

Intel Max 10 FPGA는 온칩 NOR 플래시 메모리를 통합하여 FPGA 구성을 유지합니다. 다른 제품군에는 SRAM 기반 구성 셀이 있으며 전원을 켤 때 기판 실장형 외부 메모리 장치나 시스템 내의 다른 위치(예: 외부 프로세서의 제어에 따름)에서 구성을 로드합니다. MAX 10 제품군을 제외하고 모든 다른 Intel FPGA 제품군은 FPGA 또는 강화된 마이크로 프로세서 시스템이 통합된 SoC FPGA로 제공됩니다.

MAX 10 FPGA의 통합 기능에는 아날로그 디지털 컨버터(ADC)와 이중 구성 플래시가 있으며, 단일 칩에서 두 이미지를 저장하여 상호 동적으로 전환할 수 있도록 해줍니다. 또한 MAX 10 FPGA는 Nios II 소프트 코어 내장형 프로세서를 지원하며 DSP 블록 및 소프트 이중 데이터 전송률 3(DDR3) 메모리 컨트롤러를 제공합니다.

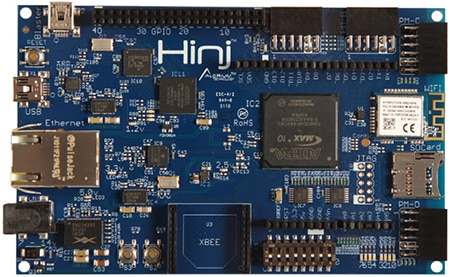

MAX 10 포트폴리오의 대표적인 장치에는 16000개의 논리 소자/셀, 총 562176비트 RAM 및 130개 입력/출력(I/O)을 제공하는 10M16SCU169I7P가 있습니다. MAX 10에 적합한 평가 기판으로 Intel의 EK-10M08E144를 사용할 수 있습니다. 다른 평가 기판에는 Alorium Technology, LLC의 FPGA IoT 센서 허브 개발 키트인 HINJKIT가 있습니다(그림 3). HINJKIT는 MAX 10 FPGA에 Arduino IDE에서 HINJKIT를 사용할 수 있도록 해주는 Alorium Technology의 AVR 호환 8비트 마이크로 컨트롤러가 포함되어 특히 흥미롭습니다. 또한 이 기판은 타사 IoT 캐리어 기판, 모듈 및 부속품을 위한 높은 수준의 인터페이스 유연성을 제공합니다.

그림 3: HINJKIT는 타사 IoT 캐리어 기판, 모듈 및 부속품을 위한 높은 수준의 인터페이스 유연성을 제공하는 Alorium의 MAX 10 FPGA 개발 플랫폼입니다. (이미지 출처: Alorium Technology)

그림 3: HINJKIT는 타사 IoT 캐리어 기판, 모듈 및 부속품을 위한 높은 수준의 인터페이스 유연성을 제공하는 Alorium의 MAX 10 FPGA 개발 플랫폼입니다. (이미지 출처: Alorium Technology)

Intel의 Cyclone 10 GX FPGA는 12.5GB 트랜시버 기반 기능, 1.4Gb/s 저전압 차동 신호(LVDS), 최대 1866Mb/s의 데이터 전송률을 지원하는 최대 72비트 폭 DDR3 SDRAM 인터페이스를 제공합니다. Cyclone 10 GX FPGA는 머신 비전, 비디오 연결, 스마트 비전 카메라와 같이 높은 대역폭 성능이 필요한 응용 제품에 최적화되었습니다.

그에 비해 Cyclone 10 LP FPGA는 I/O 확장, 센서 융합, 모터/동작 제어, 칩 간 브리징, 제어와 같은 낮은 정지 전력, 저가형 응용 제품에 최적화되었습니다. GX 및 LP 장치 제품군은 모두 수직 마이그레이션을 지원하므로, 설계자가 한 장치에서 설계를 시작하고 나중에 인접한 다양한 장치로 마이그레이션할 수 있습니다.

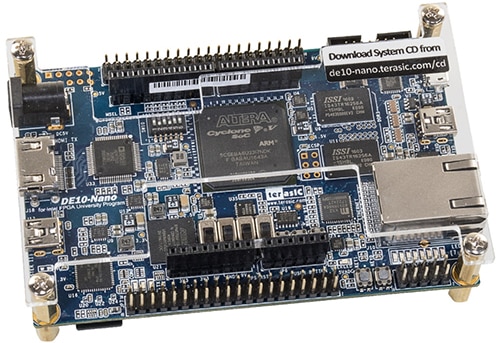

Cyclone 10 포트폴리오의 대표적인 제품에는 6272개 논리 소자/셀, 총 276480비트 RAM 및 176개 I/O를 제공하는 10CL006YU256A7G가 있습니다. Terasic Inc의 P0496 DE10-NANO Cyclone V SE SoC 키트(그림 4), P0553 TSoM Cyclone V SE 평가 기판(Cyclone V SoC FPGA 기반) 및 P0581 TSoM Cyclone V SE FPGA 평가 기판을 비롯하여 다양한 관련 개발 기판과 평가 기판 및 모듈을 사용할 수 있습니다. 이러한 기판에 제공되는 Cyclone V FPGA는 이전 세대 Cyclone 10 제품군입니다.

그림 4: 저가형 P0496 DE10-NANO 개발 키트는 Cyclone FPGA를 체험하여 평가할 수 있는 강력한 하드웨어 설계 플랫폼을 제공합니다. (이미지 출처: Terasic Inc.)

그림 4: 저가형 P0496 DE10-NANO 개발 키트는 Cyclone FPGA를 체험하여 평가할 수 있는 강력한 하드웨어 설계 플랫폼을 제공합니다. (이미지 출처: Terasic Inc.)

TSMC의 20nm 프로세스 기술을 기반으로 하는 Arria 10 장치는 이중 코어 Arm Cortex-A9 MPCore HPS(하드 프로세서 시스템)를 강화된 부동 소수점 DSP 블록을 포함하는 프로그래밍 가능 패브릭과 결합합니다. 또한 Arria 10 장치는 단일 고집적 패키지에서 내장형 고속 트랜시버, 하드 메모리 컨트롤러 및 프로토콜 지적 재산(IP) 컨트롤러를 모두 제공합니다.

Arria 10 포트폴리오의 대표적인 장치에는 220000개 논리 소자/셀, 총 13752320비트 RAM 및 240개 I/O를 제공하는 10AX022C4U19E3SG가 있습니다. 이 FPGA로 개발하는 데 적합한 플랫폼으로 Intel의 DK-DEV-10AX115S-A Arria 10 GX FPGA 평가 기판을 사용할 수 있습니다(그림 5). 이 기판을 사용하면 설계자가 Arria 10 기반 PCI Express(PCIe) 3.0 설계를 개발 및 테스트하고, DDR4, DDR3, QDR IV 및 RLDRAM III 메모리로 구성된 메모리 서브 시스템을 개발 및 테스트하고, FPGA 메자닌 카드(FMC) 커넥터를 통해 Intel 파트너가 제공하는 FMC 메자닌 카드에 연결하여 확장 가능한 모듈식 설계를 개발할 수 있습니다.

그림 5: DK-DEV-10AX115S-A Arria 10 GX FPGA 개발 키트는 PCIe 기반 설계, 메모리 서브 시스템 및 FMC 카드 기반 시스템을 개발 및 테스트하는 데 필요한 모든 하드웨어와 소프트웨어를 포함하는 완벽한 설계 환경을 제공합니다. (이미지 출처: Intel)

그림 5: DK-DEV-10AX115S-A Arria 10 GX FPGA 개발 키트는 PCIe 기반 설계, 메모리 서브 시스템 및 FMC 카드 기반 시스템을 개발 및 테스트하는 데 필요한 모든 하드웨어와 소프트웨어를 포함하는 완벽한 설계 환경을 제공합니다. (이미지 출처: Intel)

Intel의 Stratix 10 FPGA 및 SoC FPGA는 Intel Hyperflex FPGA 아키텍처를 제공합니다. 이 장치 라인의 FPGA는 28.3Gb/s(GX) ~ 57.8Gb/s에서 최대 10 TFLOPS의 부동 소수점 성능 및 트랜시버를 지원하여 처리량이 높은 시스템의 요구 사항을 충족합니다. 후자의 경우 최대 144개 트랜시버 레인에서 5G 통신, 클라우드 컴퓨팅, 네트워크 가상화 및 광학 전송 네트워크에 대한 대역폭 요구 사항을 충족합니다. 변형품에는 16GT/s에서 최대 x16 구성을 지원하는 PCIe Gen4 인터페이스와 선정된 Intel Optane DC 영구 메모리를 지원하는 새로운 메모리 컨트롤러가 있습니다.

Stratix 10 라인을 통한 개발은 Intel의 DK-DEV-1SGX-L-A Arria 10 GX FPGA 평가 기판에서 지원합니다(그림 6). 이 기판을 사용하면 설계자가 Stratix 10 기반 PCI Express(PCIe) 3.0 설계를 개발 및 테스트하고, DDR4, DDR3, QDR IV 및 RLDRAM III 메모리로 구성된 메모리 서브 시스템을 개발 및 테스트하고, FPGA 메자닌 카드(FMC) 커넥터를 통해 Intel 파트너가 제공하는 FMC 메자닌 카드에 연결하여 확장 가능한 모듈식 설계를 개발할 수 있습니다.

그림 6: DK-DEV-1SGX-L-A Stratix 10 GX FPGA 평가 기판은 PCIe 기반 설계, 메모리 서브 시스템 및 FMC 카드 기반 시스템을 개발 및 테스트하는 데 필요한 모든 하드웨어와 소프트웨어를 포함하는 완벽한 설계 환경을 제공합니다. (이미지 출처: Intel)

그림 6: DK-DEV-1SGX-L-A Stratix 10 GX FPGA 평가 기판은 PCIe 기반 설계, 메모리 서브 시스템 및 FMC 카드 기반 시스템을 개발 및 테스트하는 데 필요한 모든 하드웨어와 소프트웨어를 포함하는 완벽한 설계 환경을 제공합니다. (이미지 출처: Intel)

Intel의 FPGA 및 SoC FPGA를 통한 설계 및 개발

FPGA에 관한 이 시리즈의 1부에서 살펴본 바와 같이 이러한 장치를 설계하는 기존 방식에서는 설계자가 Verilog, VHDL과 같은 하드웨어 기술 언어(HDL)를 사용하여 레지스터 전송 레벨(RTL)이라는 추상화 레벨에서 설계 의도를 파악했습니다. 먼저 이러한 RTL 기술을 시뮬레이션하여, FPGA를 구성(프로그래밍)하는 데 사용되는 구성 파일을 생성하는 합성 도구에 전달된 후 필요에 따라 기술이 수행되는지 확인할 수 있습니다.

추상화의 다음 단계는 C/C++과 같은 프로그래밍 언어나 SystemC(이벤트 기반 시뮬레이션 인터페이스를 제공하는 C++ 클래스 및 매크로 세트)와 같은 특수 구현을 사용하여 설계 의도를 파악하는 것입니다. 이러한 방법은 각각 일반 C++ 구문을 사용하여 기술되는 동시 프로세스 시뮬레이션을 간소화합니다. 그런 기술을 일반 프로그램처럼 실행하여 분석하고 프로파일링한 후 고급 합성(HLS) 엔진에 전달하여 일반 합성 엔진에 공급되는 RTL을 출력할 수 있습니다.

개념적으로 더 높은 수준의 추상화에는 이기종 플랫폼 전반에서 실행되는 프로그램을 작성하기 위한 플랫폼인 OpenCL(개방형 컴퓨팅 언어)이 있습니다. FPGA 외에도 이러한 플랫폼에는 중앙 처리 장치(CPU), 그래픽 처리 장치(GPU), 디지털 신호 처리기(DSP) 및 기타 프로세서 또는 하드웨어 가속기가 포함되어 있습니다. OpenCL은 컴퓨팅 장치에서 플랫폼을 제어하고 프로그램을 실행하기 위한 애플리케이션 프로그래밍 인터페이스(API)와 함께 이러한 장치를 프로그래밍하기 위한 프로그래밍 언어(C99 및 C++11 기반)를 지정합니다.

Intel FPGA 및 SoC FPGA의 경우 사용자는 Intel Quartus Prime 설계 소프트웨어를 사용하여 모든 제품군에 대한 설계를 개발합니다. 이 소프트웨어는 Quartus Prime Pro Edition, Quartus Prime Standard Edition, Quartus Prime Lite Edition의 세 가지 버전으로 제공됩니다. Pro Edition과 Standard Edition은 유료 라이선스가 필요하고, Lite Edition은 무료로 다운로드할 수 있습니다.

Pro Edition은 Agilex, Stratix 10, Arria 10 및 Cyclone 10 GX 장치 제품군에서 FPGA 및 SoC FPGA의 고급 기능을 지원하도록 최적화되었으며, Standard Edition은 Cyclone 10 LP 장치 제품군과 이전 장치 제품군을 포괄적으로 지원하며, 라이선스 파일 없이 무료로 다운로드할 수 있는 Lite Edition은 대용량 장치 제품군에 대한 이상적인 진입점 역할을 합니다.

Intel은 Intel DSP Builder, Intel High Level Synthesis(HLS) Compiler, Intel FPGA SDK for OpenCL을 비롯하여 광범위한 추가 설계 도구 및 리소스를 제공합니다.

또한 OpenVINO 도구 키트의 Intel 배포판을 사용하면 개발자가 인공 지능(AI), 컴퓨터 비전, 오디오, 음성 및 언어 응용 제품을 구축하여 에지부터 클라우드까지 딥 러닝 추론을 지원할 수 있습니다. FPGA 이외에 이 도구 키트는 공통 API를 사용하여 Intel 아키텍처 및 AI 가속기(CPU, iGPU, Intel Movidius Vision Processing Unit(VPU), Intel Gaussian & Neural Accelerator(GNA) 등) 전반에서 이기종 실행을 지원합니다. 이 도구 키트는 Cyclone V GT FPGA 기반 OpenVINO 시험용 키트에 의해 지원됩니다.

결론

최적의 처리 설계 솔루션은 종종 프로세서 및 FPGA의 조합, FPGA 자체 또는 패브릭의 일부로 하드 프로세서 코어를 자랑하는 FPGA에 의해 제공됩니다. 첨단 기술로서 FPGA는 수년간 빠르게 발전하여 유연성, 처리 속도 및 전력 측면에서 많은 설계 요구 사항을 해결할 수 있으므로 지능형 인터페이스, 머신 비전, 인공 지능 등 광범위한 응용 분야에 유용합니다.

Intel의 프로그래밍 가능 장치 제품은 하위 등급의 기존 FPGA부터 최고급 SoC FPGA까지 전 범위를 포괄합니다. 위에서 살펴본 바와 같이 이러한 장치에서 설계를 생성할 수 있도록 Intel 및 기타 타사에서는 하드웨어 개발자, 소프트웨어 개발자, 인공 지능 및 컴퓨터 비전 시스템 작성자의 요구 사항을 충족하는 강력한 개발 키트 및 도구 제품군을 제공합니다.

추가 자료

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.