고정밀 산업용 감지 시스템 프런트 엔드 설계자

DigiKey 북미 편집자 제공

2019-05-02

산업 및 공정 제어 응용 제품은 업스트림 의사 결정을 위해 광범위한 정밀 온도, 압력, 변형 데이터를 수집합니다. 설계자의 과제는 이러한 응용 제품에는 주파수 도메인에서 높은 정확도를 유지하기 위해 여러 개의 고정밀 채널이 필요하다는 것입니다.

이 기사에서는 정확한 고성능 산업용 감지 및 신호 변환 프런트 엔드의 핵심 부품과 파라메트릭 요구 사항에 대해 설명합니다. 잡음은 정확도에 관한 결정적인 요인이므로 적합한 최종 솔루션은 잡음 문제를 해결합니다.

시스템 개요

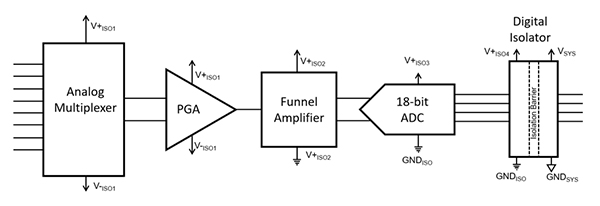

고정밀 18비트 산업용 감지 프런트 엔드 시스템은 산업용 신호 수준을 관리할 수 있는 비용 효율적이며 격리된 다중 채널 데이터 취득(DAQ) 구조로 구성되어야 합니다. 입력에서 출력까지, 설명할 다중 채널 고정밀 회로는 8입력 멀티플렉서로 시작해 단일 종단 또는 차동 입력 채널로 구성 가능합니다(그림 1). 이러한 멀티플렉서 입력은 공정 제어를 위해 온도, 압력 및 광학 센서 등 다양한 센서 입력을 받습니다.

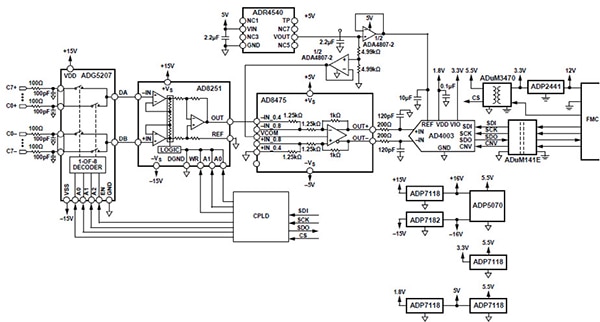

그림 1: 다중 채널 입력을 위한 8입력 다중 채널 고정밀 회로는 단일 종단 또는 차동 입력 채널로 구성 가능한 입력 멀티플렉서로 시작됩니다. (이미지 출처: Bonnie Baker)

그림 1에서 “PGA”로 표시된 프로그래밍 가능한 이득 계측 증폭기(PGIA)는 유사한 입력 및 출력 스윙 전압 능력을 지닌 입력 멀티플렉서를 따릅니다. 멀티플렉서와 PGIA 스테이지는 모두 최대 ±10V까지의 고전압 입력을 관리할 수 있습니다.

PGIA의 공통 모드 전압과 폭넓은 전압 출력 스윙은 18비트 아날로그 디지털 컨버터(ADC)의 단일 공급 입력 범위와 일치하지 않습니다. ADC의 신호 전압 범위를 준비하기 위해 시스템에는 깔때기 증폭기가 필요합니다. 깔때기 증폭기는 단일 레벨 조정, 단일 종단에서 차동으로의 변환 ,단일 공급 18비트 ADC의 입력 요구 사항 충족을 위한 감쇠 등 세 가지 기능을 수행합니다.

18비트 ADC 뒤에서 디지털 절연기가 전기적 분리를 제공합니다. 이러한 분리 스타일을 이용하면 신호 무결성에 대한 방해 없이 각 사이드 사이에 서로 다른 공통 모드 전압을 허용할 수 있습니다.

회로 세부정보

지금까지 설명한 바와 같이 분리된 다중 채널 DAQ 시스템에는 멀티플렉서, PGIA 스테이지, ADC 증폭기 구동기, 정밀 전체 차동 연속 근사화 레지스터(SAR) ADC가 있습니다. 시스템은 단일 ADC를 이용해 8개의 채널을 모니터링합니다. 하지만 ADC 구동기와 ADC는 잡음을 유발하는 주요 요인입니다(그림 2).

그림 2: 18비트 ADC가 있는 분리형 다중 채널 DAQ 시스템의 회로도입니다. ADC 및 ADC 구동기는 잡음을 유발하는 주요 요인입니다. (이미지 출처: Analog Devices)

잡음 수준은 이 응용 제품 회로에 장착될 부품의 유형을 결정하는 하나의 사양입니다.

적합한 부품 선택

그림 2의 입력 멀티플렉서는 Analog Devices의 ADG5207BCPZ-RL7로, 3.5pF의 초저정전 용량과 0.35pC의 전하 주입을 특징으로 하는, 래치업의 영향을 받지 않는 고전압 8채널 차동 멀티플렉서입니다. 이러한 저전하 주입을 통해 이 스위치는 낮은 결함 비율과 빠른 정착 시간이 필요한 샘플 앤 홀드 DAQ 회로에 적합하게 됩니다. ADG5207은 단일 종단 및 차동 입력 신호 모두를 수신하도록 구성될 수 있습니다. 회로에서 보이는 CPLD(복합 프로그래밍 가능 논리 소자)는 주소 핀을 이용해 ADG5207의 활성 채널을 선택합니다.

PGIA는 Analog Devices의 AD8251ARMZ-R7입니다. 이 장치는 1, 2, 4 및 8의 선택 가능한 이득을 제공합니다. 뒤이어, Analog Devices의 AD8475ACPZ-R7 선택 가능 이득, 전체 차동 깔때기 증폭기는 접지 공통 모드 전압에 대해 2.048V로의 레벨 조정과 0.4 및 0.8의 이득 설정을 제공합니다. AD8475는 10nV/√Hz의 저출력 잡음 스펙트럼 밀도를 나타냅니다. PGIA 및 깔때기 증폭기의 이득은 Analog Devices AD4003BCPZ-RL7 18비트 SAR ADC에 적합한 전체 범위 입력 신호를 제공할 수 있도록 결합됩니다(표 1).

|

표 1: AD8251 PGIA의 4가지 이득 구성에 해당하는 입력 및 출력 전압 범위 PGIA 및 AD8475 깔때기 증폭기의 이득은 AD4003BCPZ-RL7 18비트 SAR ADC에 적합한 전체 범위 입력 신호를 제공할 수 있도록 결합됩니다. (표 출처: Bonnie Baker)

AD4003BCPZ-RL7은 4.096V 참조에 대해 98dB의 일반적인 신호대 잡음비(SNR)를 제공하는 완전 차동 2MSPS, 18비트 정밀 SAR ADC입니다.

시스템 잡음 분석

정확도에 대한 영향으로 인해 고속 정밀 DAQ를 설계할 때는 잡음을 심각하게 고려해야 합니다. 잡음은 ADC의 디지털 출력의 AC 및 DC 정확도에 모두 영향을 미치는 주파수 도메인의 한 현상입니다. 잡음은 무작위 이벤트로, 잡음이 많은 회로는 단일 변환에 대해 절대적으로 정확한 결과를 제공하지만 다음 변환에서는 대단히 부정확한 결과를 도출할 수 있습니다. 설계자의 과제는 회로 내의 모든 장치에 대해 수락 가능한 잡음 기여를 결정하는 것입니다.

전체 시스템의 실효값(rms) 잡음은 AD4003 ADC의 입력에 참조되는 모든 장치의 RSS(합의 제곱근)와 동일하며 방정식 1을 이용해 계산됩니다.

![]() 방정식 1

방정식 1

여기서,

VnADG5207 = ADG5207 멀티플렉서 rms 잡음 기여

VnAD8251 = AD8251 PGIA rms 잡음 기여

VnAD8475 = AD8475 깔때기 증폭기 rms 잡음 기여

VnAD4003 = AD4003 18비트 ADC rms 잡음 기여

계산된 시스템 rms SNR은 AD4003의 전체 범위 입력 범위 또는 VREF를 사용하며 방정식 2를 이용해 계산됩니다.

![]() 방정식 2

방정식 2

AD4003 ADC 잡음: AD4003 ADC 잡음은 컨버터의 양자화 오류 및 내부 열 잡음의 함수입니다. AD4003의 rms 입력 전압 잡음의 계산은 방정식 3에 따라 전체 범위 입력 전압(VREF)과 작동 SNR을 사용합니다.

![]() 방정식 3

방정식 3

4.096V와 동일한 VREF가 포함된 AD4003의 SNR에 대한 규격서 사양은 약 98dB입니다.

AD8475 깔때기 증폭기 잡음: AD8475 rms 출력 잡음은 1kHz에서의 증폭기의 스펙트럼 잡음 밀도(AD8475)와 증폭기 회로의 대역폭 제한의 결합입니다. 0.4V/V의 이득을 제공하는 AD8475 대역폭은 150MHz와 동일합니다. 다음 레지스터-커패시터(RC) 필터의 3dB 코너 주파수는 6.63MHz입니다. AD8475와 출력 RC 필터의 결합은 방정식 4에 따라 6.63Mhz의 대역폭 제한을 발생시킵니다.

![]() 방정식 4

방정식 4

여기서,

AD8475 = 10nV/√Hz.

R = 200Ω

C = 120pF

BWRC = 1/(2xp x R x C) ~ 6.63MHz

AD8251 PGIA 잡음: AD8251의 rms 잡음 기여는 입력에 참조된 AD8251, 단위가 nV/√Hz인 1kHz 스폿 잡음(AD8251), 이득 설정(GAD8251), AD8475 (GAD8475)의 이득, AD4003 (BWRC) 입력에서의 잡음 필터 대역폭의 함수입니다. 이는 방정식 5를 이용해 계산됩니다.

![]() 방정식 5

방정식 5

AD8251의 값은 1V/V 이득에 대해 40nV/√Hz, 8V/V 이득에 대해 18nV/√Hz와 동일합니다.

ADG5207 멀티플렉서 잡음: Johnson-Nyquist 잡음 방정식은 멀티플렉서의 잡음 스펙트럼 밀도 및 결과 rms 잡음을 제공합니다. 방정식 6:

![]() 방정식 6

방정식 6

여기서,

kB = 볼츠만 상수 = 1.38 x 10-23

T = 온도(켈빈)

RON = 저항이 “켜진” 멀티플렉서(ADG5207 규격서에 따름)

이 공식(방정식 6)의 사용은 멀티플렉서가 계열 저항과 유사하게 작동하므로 적합합니다.

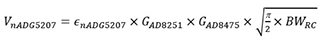

멀티플렉서의 스펙트럼 밀도 값(nADG5207)은 방정식 7을 이용해 ADG5207 rms 잡음 기여를 도출합니다.

방정식 7

방정식 7

잡음 분석 요약

그림 2의 각 부품에 대해 계산된 총 잡음 기여와 3.2의 누적 이득에 대한 결과 SNR은 84.7dB입니다. 총 잡음에 대한 가장 중대한 기여 요인은 AD8251 PGIA 및 AD4003 ADC입니다(표 2).

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

표 2: 3.2의 누적 이득에 대한 다중 채널 DAQ의 계산된 SNR 성능은 84.7dB입니다. (데이터 출처: Analog Devices)

회로 평가 및 테스트

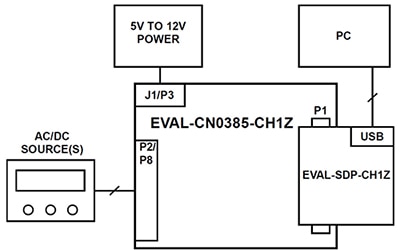

이 회로를 평가 및 테스트하기 위해 설계자는 그림 2 회로에 포함된 EVAL-CN0385-FMCZ 회로 평가 키트를 사용할 수 있습니다(그림 3).

그림 3: EVAL-CN0385-FMCZ 평가 기판은 이 기사에서 설명한 DAQ 프런트 엔드 설계를 실험하는 데 사용될 수 있습니다. (이미지 출처: Analog Devices)

CN-0385 설계 지원 패키지에는 완전한 회로도와 레이아웃 지원 자료가 포함되어 있습니다. 또한 평가 키트는 EVAL-SDP-CH1Z 컨트롤러 기판도 포함해 데이터 캡처를 용이하게 합니다(그림 4).

그림 4: DAQ 프런트 엔드를 평가하기 위한 테스트 설정 기능 레이아웃. (이미지 출처: Analog Devices)

EVAL-CN0385-FMCZ 기판의 성능 결과는 잡음 계산과 거의 일치하는 값을 보여줍니다(표 3).

|

표 3: 0.4, 0.8, 1.6, 3.2 누적 이득에 대한 10kHz 전체 범위 사인파 입력에 대한 EVAL-CN0385-FMCZ 기판의 SNR, 잡음 및 총 고조파 왜곡(THD). (데이터 출처: Analog Devices)

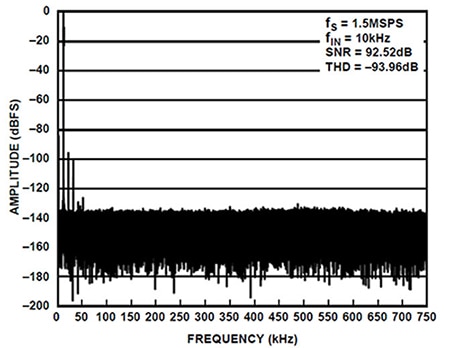

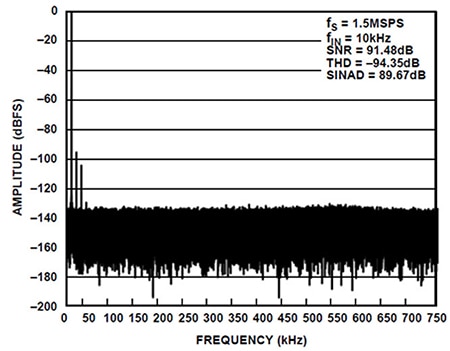

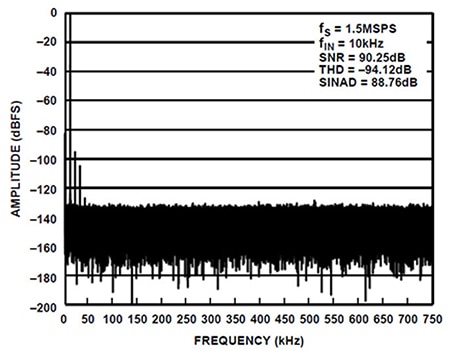

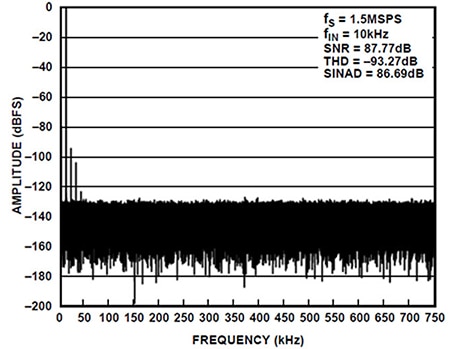

Audio Precision SYS-2700은 차동 입력 모드로 신호를 생성했습니다. 10kHz 입력 신호 고속 프리에 변환(FFT) 플롯이 표시됩니다(그림 5, 6, 7 및 8).

그림 5: 단일, 정적 채널의 이득 = 0.4에 대한 10kHz, 20V p-p 입력의 FFT. (이미지 출처: Analog Devices)

그림 6: 단일, 정적 채널의 이득 = 0.8에 대한 10kHz, 10V p-p 입력의 FFT. (이미지 출처: Analog Devices)

그림 7: 단일, 정적 채널의 이득 = 1.6에 대한 10kHz, 5V p-p 입력의 FFT. (이미지 출처: Analog Devices)

그림 8: 단일, 정적 채널의 이득 = 3.2에 대한 10kHz, 2.5V p-p 입력의 FFT. (이미지 출처: Analog Devices)

플롯에 표시된 바와 같이 EVAL-CN0385-FMCZ 평가 기판 내부의 ADG5207, AD8251, AD8475, AD4003 신호 체인은 앞의 계산과 매우 가까운 값에 매핑합니다.

결론

산업 및 공정 제어 환경에는 정밀한 온도, 압력 및 변형 데이터 수집을 포함한 폭넓은 데이터 수집 활동이 있습니다. 이러한 응용 분야에는 주파수 도메인에서 저잡음으로 높은 정확도를 유지하면서 멀티플렉싱된 고정밀 채널이 필요합니다. 이상적인 아날로그 측정 프런트 엔드에는 멀티플렉서, PGIA 및 18비트, 2.0MSPS 정밀 ADC가 있습니다. ADC는 활성 멀티플렉서 채널에서 신호를 샘플링합니다. 이 기사에서는 정확한 계산과 적합한 회로를 위한 보완 테스트 데이터를 제공합니다. 테스트 결과는 EVAL-CN0385-FMCZ 평가 기판 내부의 ADG5207, AD8251, AD8475 및 AD4003 신호 체인의 실제 결과를 앞의 계산과 매우 가까운 값에 매핑합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.