Design Gateway의 IP 코어를 사용하여 Xilinx VCK190 평가 키트에서 AI 응용 제품 기능 개선 가속화

2022-11-18

Xilinx의 Versional AI Core 계열 장치는 높은 계산 효율성 ASIC급 AI 컴퓨팅 엔진과 유연한 프로그래밍이 가능한 패브릭을 사용하여 AI 추론의 고유하고 가장 어려운 문제를 해결하도록 설계되어, 저전력 및 짧은 대기 시간을 제공하면서 작업 부하에 대해 효율성을 극대화하는 가속기가 있는 AI 응용 제품을 설계합니다.

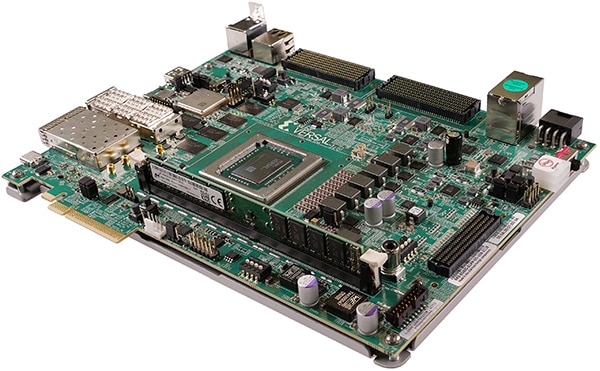

Versal AI Core 계열 VCK190 평가 키트는 포트폴리오 내에서 AI 성능이 가장 우수한 VC1902 장치를 갖추고 있습니다. 이 키트는 높은 처리량의 AI 추론 및 신호 처리 컴퓨팅 성능이 필요한 설계를 위해 제작되었습니다. 현재 서버급 CPU보다 100배 더 강력한 컴퓨팅 성능을 제공하고 다양한 연결 옵션을 제공하는 VCK190 키트는 클라우드에서 에지에 이르기까지 다양한 응용 제품을 위한 평가 및 시제품 제작 플랫폼입니다.

그림 1: Xilinx Versal AI Core 계열 VCK190 평가 키트. (이미지 출처: AMD, Inc)

그림 1: Xilinx Versal AI Core 계열 VCK190 평가 키트. (이미지 출처: AMD, Inc)

VCK190 평가 키트의 주요 특징

- 온보드 Versal AI Core 계열 장치

- Versal ACAP XCVC1902 양산용 실리콘 탑재

- 현재 서버급 CPU보다 100배 더 강력한 컴퓨팅 성능을 제공하는 AI 및 DSP 엔진

- 신속한 시제품 제작을 위해 사전 구축된 파트너 참조 설계

- 최첨단 응용 제품 개발을 위한 최신 연결 기술

- NVMe SSD 및 호스트 프로세서와 같은 고성능 장치 인터페이스를 위한 내장형 PCIe® Gen4 하드 IP

- 고속 100G 네트워크 인터페이스를 위한 내장형 100G EMAC 하드 IP

- DDR4 및 LPDDR4 메모리 인터페이스

- 공동 최적화 도구 및 디버그 방법

- Vivado® ML, Vitis™ 통합 소프트웨어 플랫폼, Vitis AI, AI 추론 응용 제품 개발을 위한 AI 엔진 도구

Xilinx의 Versal AI Core 계열 장치를 사용하여 AI 인터페이스 가속화

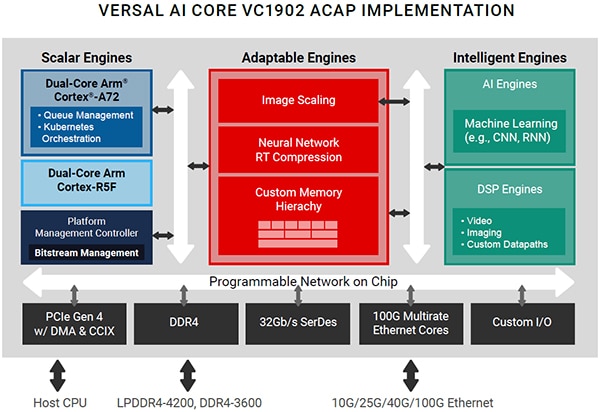

그림 2: Xilinx Versal AI Core VC1902 ACAP 장치 제품 구성도 (이미지 출처: AMD, Inc)

그림 2: Xilinx Versal AI Core VC1902 ACAP 장치 제품 구성도 (이미지 출처: AMD, Inc)

Versal® AI Core 적응형 컴퓨팅 가속 플랫폼(ACAP)은 광범위한 AI 작업 부하에 대해 하드웨어 및 소프트웨어 수준에서 역동적으로 적응할 수 있는 고도로 통합된 멀티코어 이기종 장치로, AI 에지 컴퓨팅 응용 제품 또는 클라우드 가속기 카드에 이상적입니다. 이 플랫폼은 내장형 컴퓨팅을 위한 차세대 스칼라 엔진, 하드웨어 유연성을 위한 적응형 엔진 및 지능형 엔진(추론과 신호 처리를 위한 DSP 엔진과 혁신적인 AI 엔진으로 구성됨)을 통합합니다. 그 결과로 AI/ML 작업 부하에 대한 기존의 FPGA 및 GPU의 성능, 대기 시간 및 전력 효율성을 능가하는 적응형 가속기가 탄생했습니다.

Versal ACAP 플랫폼 주요 사항

- 적응형 엔진

- 맞춤형 메모리 계층을 통해 가속기 커널의 데이터 이동 및 관리 최적화

- 신경망 RT 압축 및 이미지 스케일링을 포함한 사전 처리 기능 및 사후 처리 기능

- AI 엔진(DPU)

- XCVC1902 장치에서 최대 133 INT8 TOPS 성능을 보여주는 딥 러닝 프로세싱 유닛 또는 DPU로 불리는 타일 형식으로 배열된 벡터 프로세서

- CNN, RNN 및 MLP에 이르는 신경망에 이상적이며, 진화하는 알고리즘에 최적화할 수 있는 하드웨어

- 스칼라 엔진

- 쿼드 코어 ARM 처리 서브 시스템이며, 보안, 전력 및 비트스트림 관리를 위한 플랫폼 관리 컨트롤러

VCK190 AI 추론 성능

VCK190은 현재 서버급 CPU에 비해 100배 이상의 강력한 컴퓨팅 성능을 제공할 수 있습니다. 아래는 배치(Batch) = 6 기준 C32B6 DPU Core의 AI 엔진 구현을 기반으로 한 성능의 예입니다. DPU가 1250MHz에서 실행되는 VCK190의 다양한 신경망 샘플에 대한 처리량 성능(프레임/초 또는 fps)은 다음 표를 참조하십시오.

|

표 1: VCK190 AI 추론 성능의 예

VCK190 AI 성능에 대한 자세한 내용은 https://docs.xilinx.com/r/en-US/ug1354-xilinx-ai-sdk/VCK190-Evaluation-Board에서 Vitis AI 라이브러리 사용 안내서(UG1354), r2.5.0을 통해 확인하십시오.

Design Gateway의 IP 코어가 AI 응용 제품 성능을 높이는 방법은 무엇일까요?

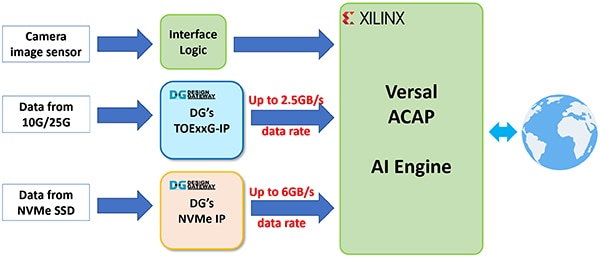

Design Gateway의 IP 코어는 CPU 관여 없이 네트워킹 및 데이터 스토리지 프로토콜을 처리하도록 설계되었습니다. 이것은 복잡한 프로토콜 프로세싱으로부터 CPU 시스템을 이상적으로 완전히 독립시킬 수 있게 하고, 계산 능력의 대부분을 AI 응용 제품에 할당할 수 있게 하며, 이를 통해 AI 추론, 사전 및 사후 데이터 처리, 사용자 인터페이스, 네트워크 통신 및 데이터 스토리지 액세스를 포함한 AI 응용 제품이 최선의 성능을 달성하도록 합니다.

그림 3: Design Gateway의 IP Core를 사용한 AI 응용 제품 사례의 제품 구성도. (이미지 출처: Design Gateway)

그림 3: Design Gateway의 IP Core를 사용한 AI 응용 제품 사례의 제품 구성도. (이미지 출처: Design Gateway)

Design Gateway의 TCP 오프로드 엔진 IP(TOExxG-IP) 성능

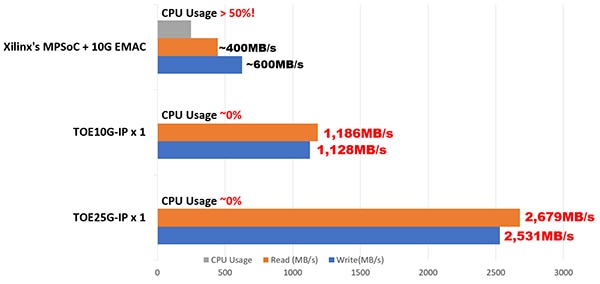

기존 CPU 시스템에서 10GbE 또는 25GbE 이상의 고속, 대용량 TCP 데이터 스트림을 처리하려면 CPU 시간의 50% 이상이 필요하므로 AI 응용 제품의 전반적인 성능이 저하됩니다. Xilinx의 MPSoC Linux 시스템에서 수행한 10G TCP 성능 테스트에 따르면 10GbE TCP 전송 중 CPU 사용량이 50% 이상이며, TCP 송수신 데이터 전송 속도는 10GbE 속도의 40~60% 또는 400MB/s~600MB/s만 도달할 수 있습니다.

Design Gateway의 TOExxG-IP Core를 구현하면 10GbE 및 25GbE를 통한 TCP 전송에 대한 CPU 사용량을 거의 0%로 줄일 수 있고 반면 이더넷 대역폭 활용을 거의 100%까지 높일 수 있습니다. 이는 순수 하드웨어 논리로 TCP 네트워크를 통해 직접적인 데이터 송수신을 가능하게 하며, 최소한의 CPU 사용량과 가능한 최저 대기 시간으로 Versal AI 엔진에 데이터를 공급할 수 있게 합니다. 아래 그림 4는 TOExxG-IP와 MPSoC Linux 시스템 간의 CPU 사용량 및 TCP 전송 속도를 비교한 내용을 보여줍니다.

그림 4: MPSoC Linux 시스템 및 Design Gateway TOExxG-IP 코어의 10G/25G TCP 전송의 성능 비교. (이미지 출처: Design Gateway)

그림 4: MPSoC Linux 시스템 및 Design Gateway TOExxG-IP 코어의 10G/25G TCP 전송의 성능 비교. (이미지 출처: Design Gateway)

Design Gateway의 Versal 장치용 TOExxG-IP

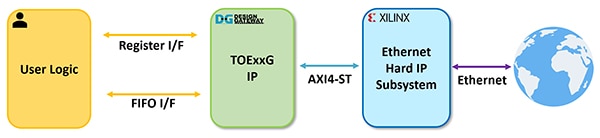

그림 5: TOExxG-IP 시스템 개요 (이미지 출처: Design Gateway)

그림 5: TOExxG-IP 시스템 개요 (이미지 출처: Design Gateway)

TOExxG-IP 코어는 TCP/IP 스택(하드와이어 논리에서)을 구현하고, 하위 계층 하드웨어 인터페이스를 위한 Xilinx의 EMAC Hard IP 및 이더넷 서브 시스템 모듈과 10G/25G/100G 이더넷 속도로 연결합니다. TOExxG-IP의 사용자 인터페이스는 제어 신호용 레지스터 인터페이스와 데이터 신호용 FIFO 인터페이스로 구성됩니다. TOExxG-IP는 AXI4-ST 인터페이스를 통해 Xilinx의 이더넷 서브 시스템과 연결하도록 설계되었습니다. 사용자 인터페이스의 클록 주파수는 이더넷 인터페이스 속도(예: 156.625MHz 또는 322.266MHz)에 따라 다릅니다.

TOExxG-IP의 특징

- CPU 필요 없이 전체 TCP/IP 스택 구현

- 하나의 TOExxG-IP로 하나의 세션 지원

- 다중 TOExxG-IP 사례를 사용하여 다중 세션 구현 가능

- 서버 모드와 클라이언트 모드를 모두 지원(수동/능동 열기 및 닫기)

- 점보 프레임 지원

- 표준 FIFO 인터페이스에 기반하는 간단한 데이터 인터페이스

- 단일 포트 RAM 인터페이스에 기반하는 간단한 제어 인터페이스

XCVC1902-VSVA2197-2MP-ES FPGA 장치의 FPGA 리소스 사용 정보는 아래 표 2에 나와 있습니다.

|

표 2: Versal 장치에 대한 구현 통계 예

TOExxG-IP에 대한 자세한 내용은 규격서를 참조하십시오. 규격서는 아래 링크의 Design Gateway 웹 사이트에서 다운로드할 수 있습니다

Design Gateway의 NVMe 호스트 컨트롤러 IP 성능

PCIe Gen3 x4 또는 PCIe Gen4 x4를 사용하는 NVMe 스토리지 인터페이스 속도는 최대 32Gbps 및 64Gbps의 데이터 속도를 제공합니다. 이는 10GbE 이더넷 속도보다 3~6배 더 빠릅니다. 가능한 최고의 디스크 액세스 속도에 도달하기 위해 CPU에서 복잡한 NVMe 스토리지 프로토콜을 처리하려면 10GbE를 통한 TCP 프로토콜 처리보다 더 많은 CPU 시간이 필요합니다.

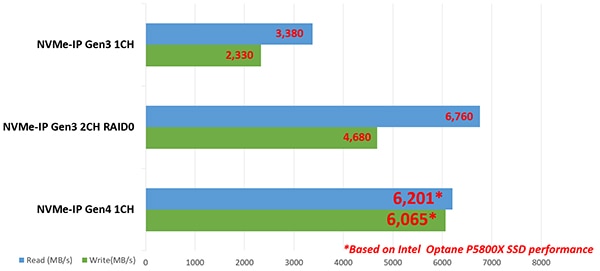

Design Gateway는 CPU 없이 NVMe SSD와 직접 통신할 수 있는 독립형 NVMe 호스트 컨트롤러로 실행 가능한 NVMe IP 코어를 개발하여 이 문제를 해결했습니다. 이를 통해 NVMe PCIe Gen3 및 Gen4 SSD 액세스의 높은 효율성과 성능이 가능하며, NVMe 프로토콜에 대한 지식 없이도 쉽게 사용할 수 있도록 사용자 인터페이스와 표준 기능을 단순화합니다. NVMe PCIe Gen4 SSD 성능은 NVMe IP로 최대 6GB/s의 전송 속도를 달성할 수 있습니다(그림 6).

그림 6: Design Gateway의 NVMe-IP 코어를 사용한 NVMe PCIe Gen3 및 Gen4 SS D의 성능 비교 (이미지 출처: Design Gateway)

그림 6: Design Gateway의 NVMe-IP 코어를 사용한 NVMe PCIe Gen3 및 Gen4 SS D의 성능 비교 (이미지 출처: Design Gateway)

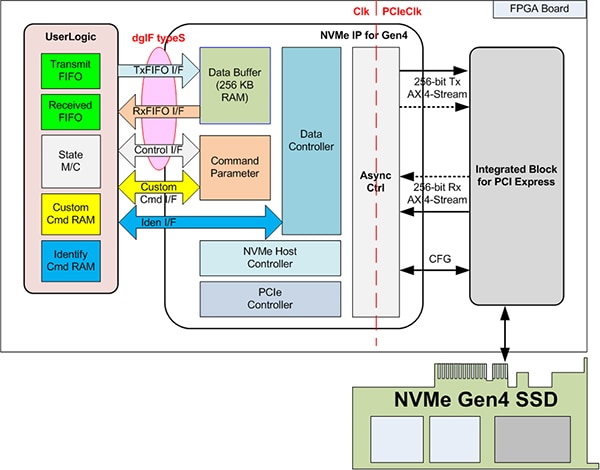

Design Gateway의 Versal 장치용 NVMe-IP

그림 7: NVMe-IP 시스템 개요 (이미지 출처: Design Gateway)

그림 7: NVMe-IP 시스템 개요 (이미지 출처: Design Gateway)

NVMe-IP의 특징

- 응용 제품 계층, 트랜잭션 계층, 데이터 링크 계층 및 물리층의 일부를 구현하여 CPU 또는 외부 DDR 메모리를 사용하지 않고 NVMe SSD 액세스 가능

- Xilinx PCIe Gen3 및 Gen4 하드 IP와 함께 작동

- 외부 메모리 인터페이스 없이 BRAM 및 URAM을 데이터 버퍼로 활용하는 기능

- 6개 명령 지원: Identify, Shutdown, Write, Read, SMART 및 Flush(선택적으로 조건부 명령 지원 가능)

XCVC1902-VSVA2197-2MP-E-S FPGA 장치의 FPGA 리소스 사용 정보는 표 2에서 확인할 수 있습니다.

|

표 3: Versal 장치에 대한 구현 통계 예

Versal 장치용 NVMe-IP에 대한 자세한 내용은 규격서를 참조하십시오. 규격서는 다음 링크의 Design Gateway 웹 사이트에서 다운로드할 수 있습니다

결론

TOExxG-IP와 NVMe-IP 코어는 TCP 및 NVMe 스토리지 프로토콜과 같은 컴퓨팅 및 메모리 집약적 프로토콜로부터 CPU 시스템을 완전히 해방하여, 실시간 AI 응용 제품에 매우 중요한 AI 응용 제품의 성능을 개선하는 데 도움이 될 수 있습니다. 이를 통해 Xilinx의 Versal AI Core 계열 장치는 네트워크 및 데이터 저장 프로토콜 처리로 인한 병목 현상이나 지연 없이 AI 추론을 수행할 수 있고 컴퓨팅 응용 분야에서 고성능을 발휘할 수 있습니다.

VCK190 평가 키트와 Design Gateway의 네트워크 및 저장 IP 솔루션은 Xilinx의 Versal AI Core 장치에서 FPGA 리소스를 가장 적게 사용하며 매우 높은 전력 효율성으로 AI 응용 제품에서 최고의 성능을 구현합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.