부하점 전력 변환 재구상하기

시스템 설계자에게 "가장 큰 당면 과제가 무엇인가요?"라고 묻는다면, 아마도 시스템을 구동하는 장치가 기판 공간의 30% ~ 50%를 차지한다는 것과, 추가 필터링 및 전자파 장해(EMI) 억제 부품이 필요하다는 사실이라고 답할 것입니다. 가전 응용 제품에서부터 데이터 센터와 네트워킹 제품에 이르기까지 대부분의 전자 시스템에서, 전력은 크기와 높이를 줄이기에 가장 제한이 많은 요소 중 하나입니다.

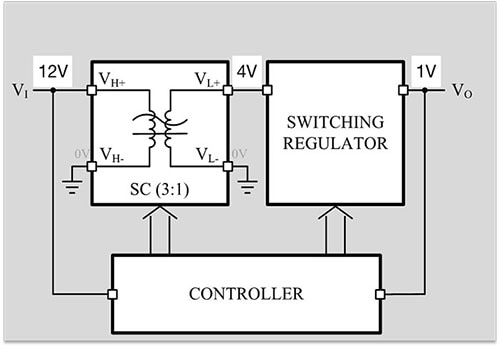

그림 1. Murata의 2단계 벅 아키텍처에는 충전 펌프와 벅 스위칭 조정기가 포함됩니다. (이미지 출처: Murata)

그림 1. Murata의 2단계 벅 아키텍처에는 충전 펌프와 벅 스위칭 조정기가 포함됩니다. (이미지 출처: Murata)

전통적으로 시스템 설계자는 12V와 같은 버스 레일에서 코어 및 응용 제품 프로세서, 시스템 ASIC, 메모리와 같은 전력 시스템 부하로 전류를 하강시키기 위해 벅 부하점(POL) 컨버터에 의존해 왔습니다. 벅 변환은 수십 년간 매우 유용하게 사용되었으며, 지속적으로 개선되고 발전하여 견고하고 비용 효율적인 솔루션으로 자리잡게 되었습니다. 그러나 출력 밀도를 실질적으로 개선하려면, 시스템 설계자들은 의례적인 개선 그 이상에 대해 생각할 수 있어야 합니다. 그렇기 때문에 Murata에서는 그림 1에 표시된 것과 같이 충전 펌프와 벅 스위칭 조정기로 구성된 2단계 POL 컨버터를 소개합니다.

많은 사람들에게는 2단계 아키텍처로 개선된 효율을 제공한다는 것이 언뜻 납득이 되지 않을 수 있습니다. 왜냐하면 각 단계의 효율이 함께 배가하기 때문입니다. 그러나 혁신적인 전환 커패시터 기술로 인해 충전 펌프는 사실상 무손실이며, 따라서 첫 변환 단계에서 상당한 효율을 제공합니다.

그림 1에서와 같이 12Vin에서 1Vout로의 통상적인 예를 고려할 때, 충전 펌프는 커패시터를 사용하여 입력 전압을 인수 3으로 나누어 12V에서 4V로 만듭니다. 두 번째 단계의 벅 인덕터는 마지막 변환으로 4V에서 1V의 부하로 만드는 더 간단한 작업을 하게 됩니다. 여기서 커패시터의 사용은 필수적인데, 그 이유는 커패시터가 인덕터에 비해 400배에 달하는 에너지 밀도를 제공하기 때문입니다. 커패시터 용량에 의존하는 솔루션은 본질적으로 더 높은 출력 밀도를 제공하게 됩니다. 이제 두 번째 단계 벅 조정기는 12Vin 전체가 아닌 4V의 낮은 입력 전압에서 작동합니다. 이를 통해 벅은 작은 출력 인덕터와 결합된 저전압, 고효율 전계 효과 트랜지스터(FET)를 사용하여 빠른 과도 응답으로 매우 높은 주파수에서 작동할 수 있는 고효율 벅 조정기를 만들어 냅니다.

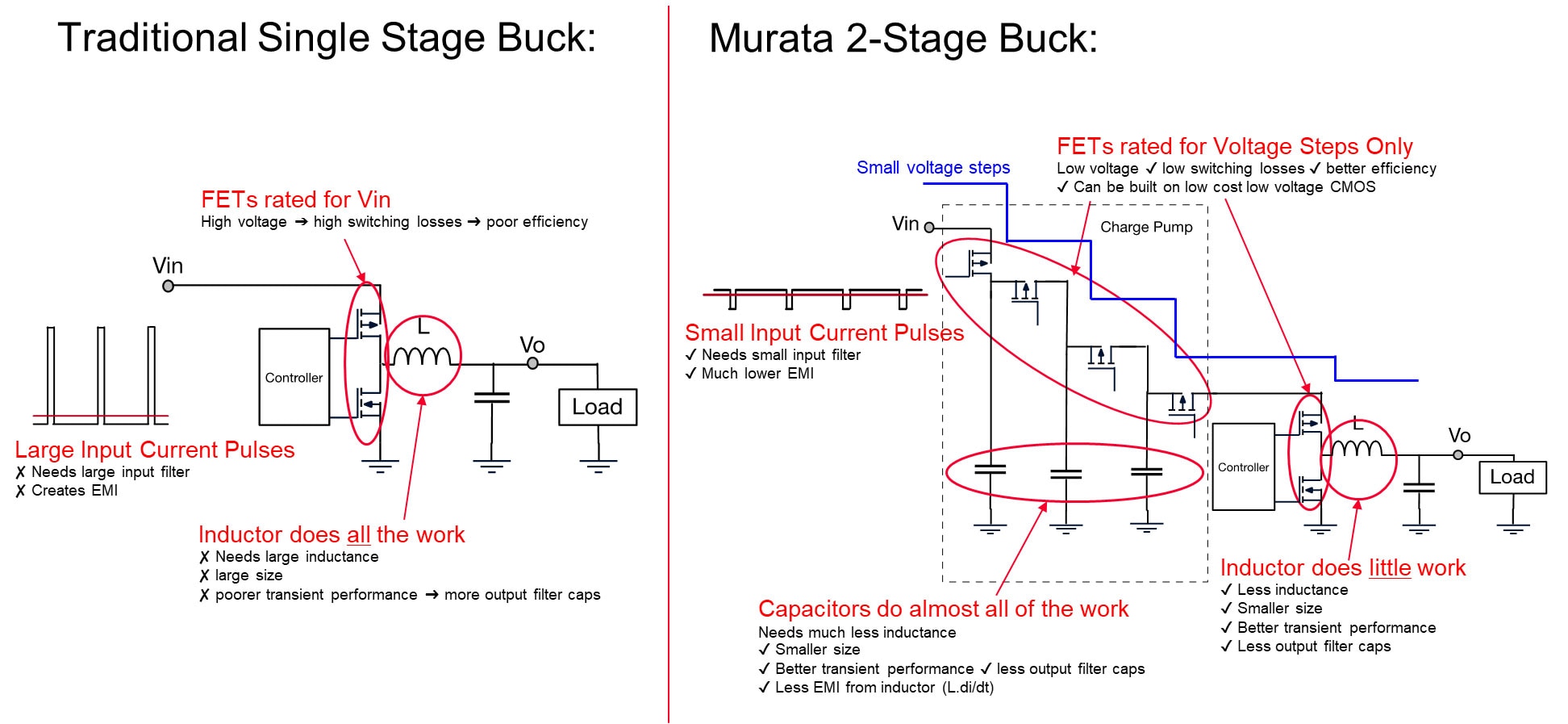

그림 2에서는 전통적인 단일 단계 벅을 2단계 벅 아키텍처와 면밀히 비교합니다.

그림 2. 전통적인 단일 단계 벅 컨버터와 Murata의 2단계 벅 컨버터 비교. (Image 출처: Murata).

그림 2. 전통적인 단일 단계 벅 컨버터와 Murata의 2단계 벅 컨버터 비교. (Image 출처: Murata).

더 전통적인 단일 단계 벅 방식이 12Vin에서 1 Vout로의 경우로 그림 2에 설명되어 있습니다. Vx 노드(FET의 중간값)은 접지부터 Vin과 누설 유도 용량 및 기생 유도 용량에 저장된 에너지 스파이크를 합산한 값까지 변화하고 있습니다. 이러한 방식에서는 고압 FET가 요구되며, 빠른 전압 변동 및 링잉으로 인해 EMI가 문제가 될 수 있습니다. 인덕터가 모든 작업을 수행하며 유도 용량이 비교적 높기 때문에, 효율과 과도 응답에 부정적인 영향을 미칩니다. 이에 더해, 하이사이드 FET는 12V:1V 경우의 불과 12분의 1(1/12 )에 해당하는 시간 동안만 전도합니다. 따라서 입력에 매우 높은 펄싱 전류가 생기므로, 추가적인 디커플링으로 전도성 EMI에의 영향을 줄여야 합니다. 이 매우 낮은 듀티 사이클 작동으로 인해, 매우 높은 스위칭 주파수에서의 작동도 불가능합니다.

그림 2에서 이 방식을 Murata의 2단계 구현과 대조해 보십시오. 충전 펌프는 정수의 간격으로 압력을 '계단식으로' 강하시키며(이 예에서는 12V를 8V로, 그 후 4V로), 따라서 각 단계에서는 4V만이 표시되고 저전압, 고효율 FET 기술을 활용할 수 있습니다. 벅 조정기는 변환의 마지막 단계를 수행합니다(4V:1V). 대부분의 작업은 첫 번째 단계 정전 용량 충전 펌프에서 이미 수행했습니다. 이 아키텍처를 통해 두 번째 단계 인덕터를 줄일 수 있어, 높은 과도 응답으로 고주파수에서 실행할 수 있는 초소형 저높이 설계가 가능합니다.

첫 번째 충전 펌프가, 50% 듀티 사이클로 실행되는 단계 두 개로 구현됩니다. 두 번째 단계 벅은 듀티 사이클의 25%에 가깝게 실행되어, 입력 전류 및 맥류가 감소됩니다. 이러한 두 가지 요인으로 인해 입력 리플과 컨버터의 EMI 프로파일이 최소화됩니다. 요약하자면, Murata의 2단계 아키텍처는 효율성, 크기 및 높이와 EMI의 면에서의 개선을 실현합니다.

더 자세한 정보는 Murata의 웨비나인 'How Murata is changing the power density paradigm'을 참조하세요.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum