올바른 스위칭 조정기 사용을 통해 효율성, 낮은 레일 잡음, 빠른 과도 응답 실현

DigiKey 북미 편집자 제공

2025-06-26

DC 레일의 품질은 무선 연결과 같이 신호 레벨이 낮은 아날로그 회로에 의존하는 응용 분야와 공급 레일 전압이 낮은 디지털 설계에서 시스템 성능을 유지하는 데 중요한 요소입니다. 변환 효율성, 출력 정확도, 안전성, 회선 및 부하 조절률 외에, DC 레일 품질도 내재된 잡음과 동적 부하 이동에 대한 과도 응답과 같은 요소에 의해 결정됩니다.

그러나 여러 세대를 거쳐 Analog Devices의 강력한 Silent Switcher 계열이 발전함에 따라 필요한 저잡음 DC 출력과 초고속 과도 응답을 제공할 수 있는(적절하게 사용할 경우) 기술이 탄생되었습니다.

이 기사에서는 사용이 편리한 고성능 DC/DC 스위칭 조정기와 이러한 조정기 사용을 통해 제공되는 이점 및 해결할 수 있는 문제를 중점적으로 살펴보겠습니다. 또한 Analog Devices의 응용 예를 사용하여 성능을 극대화하는 방법을 설명합니다.

Silent Switcher 제품군

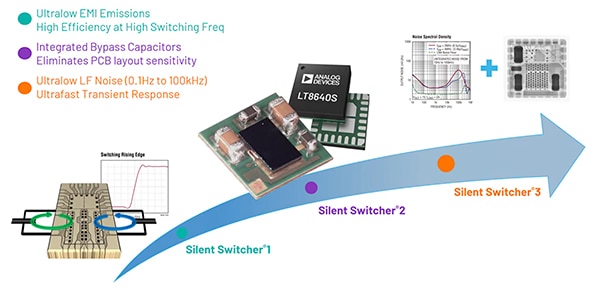

Analog Devices의 Silent Switcher 제품군 DC/DC 스위칭 조정기는 현재 3세대에 이르렀습니다. 1세대 Silent Switcher 1은 스위칭 조정기와 연관된 고주파 잡음을 줄이는 데 중점을 두었습니다. 이 제품은 낮은 전자기 간섭(EMI), 높은 효율성, 높은 스위칭 주파수(소형 관련 부품의 경우)라는 세 가지 주요 이점을 동시에 제공했습니다.

이후, Analog Devices는 1세대의 기능을 그대로 유지하면서 통합 정밀 커패시터, 더 콤팩트한 폼 팩터, 인쇄 회로 기판(PC 기판) 레이아웃에 대한 민감도 제거라는 이점을 더한 Silent Switcher 2를 소개했습니다.

3세대 Silent Switcher 3은 처음 두 세대 제품의 고유한 기능을 기반으로 합니다. 이 3세대 장치에는 빠른 과도 응답과 저주파 대역에서의 초저잡음을 비롯한 이점이 추가되었습니다(그림 1)

그림 1: Silent Switcher DC/DC 조정기의 각 후속 세대는 이전 세대의 특징과 기능을 그대로 유지하면서 향상된 기능을 추가했습니다(이미지 출처: Analog Devices).

그림 1: Silent Switcher DC/DC 조정기의 각 후속 세대는 이전 세대의 특징과 기능을 그대로 유지하면서 향상된 기능을 추가했습니다(이미지 출처: Analog Devices).

Simple Switcher 잡음 솔루션

처음 두 세대 제품의 저잡음을 달성하기 위해, 설계자는 여러 잡음원의 검토를 통해 잡음을 처리, 최소화, 제거할 수 있는 혁신적인 방법을 탐색했습니다. 이 과정에는 다면적인 접근 방식이 필요했습니다. 예를 들어, 스위치 모드 전원 공급 장치의 1차적인 잡음원은 정상 상태의 전류 흐름이 아니라 전류의 전환입니다. 기존 스위칭 조정기의 토폴로지에는 핫 루프라는 전류 흐름 경로가 있습니다. 핫 루프는 고주파 잡음이 공기 중으로 방출되어 EMI를 일으키는 1차 원인입니다. 1세대 Silent Switcher DC/DC 조정기는 핫 루프를 대칭적 형태의 2개 전류 루프로 혁신적으로 분할합니다. 이로 인해 반대 극성을 가진 두 개의 자기장이 생성되어, 방사 잡음 대부분이 상쇄됩니다.

Silent Switcher 2세대 장치는 입력 커패시터를 IC 패키지에 직접 통합함으로써 문제가 되는 핫 루프를 최소화합니다.

이 아키텍처는 높은 스위칭 주파수에서 높은 효율성을 위해 빠른 스위칭 에지를 지원하는 동시에 우수한 EMI 성능을 실현합니다. DC 입력 전압(VIN)의 내부 세라믹 커패시터는 고속 AC 전류 루프를 작게 유지하는 데 도움을 주어 성능을 더욱 개선합니다. Silent Switcher 아키텍처는 또한 매우 높은 주파수에서 효율성을 최대화하는 독점적 설계 및 패키징 기술을 사용하므로 CISPR 25 Class 5 피크 EMI 제한을 충족할 수 있습니다.

또한, 출력 전압이 부하 전류에 따라 달라지는 기술인 능동 전압 포지셔닝(AVP)이 사용됩니다. 출력 전압은 경부하 시 공칭 전압 위로, 최대 부하 시 공칭 전압 아래로 조정됩니다. DC 부하 조절률은 과도 성능을 개선하고 출력 커패시터 요구 사항을 최소화하도록 조정됩니다.

Silent Switcher 3 및 과도 응답

과도 응답은 갑작스러운 부하 변화에 대응하는 조정기의 기능을 의미하며 점점 더 중요한 파라미터가 되고 있습니다. 따라서 3세대 장치는 저주파 잡음(10Hz ~ 100kHz)을 최소화하는 것 이외에 초고속 과도 응답을 제공하는 데 중점을 두었습니다.

과도 응답에 대한 우려가 증가하는 이유는 신호 처리 장치와 시스템 온 칩(SoC)으로 인해 부하 과도 프로파일이 갑작스럽게 변화하는 경우가 많기 때문입니다. 이러한 부하 과도 현상은 고성능 RF 설계에 중요한 요소인 공급 전압에 장애를 일으킬 수 있습니다. 예를 들어, 공급 전압이 변동하면 시스템 클록 주파수에 큰 영향을 줄 수 있습니다.

따라서, RF SoC는 대개 부하 과도 현상이 발생하는 동안 블랭킹 시간을 적용합니다. 5G 응용 분야에서, 정보의 품질은 과도 시의 이러한 블랭킹 시간과 밀접하게 관련되어 있습니다. 따라서 전원 공급 장치에 대한 부하 과도 효과를 최소화하면 시스템 수준의 성능을 향상시킬 수 있습니다.

이러한 목표를 달성하기 위해 모놀리식 Silent Switcher 3 장치는 공격적인 보정에도 추가적인 안정화를 제공하는 초고성능 오차 증폭기 설계를 갖추고 있습니다. 4MHz(메가헤르츠)의 최대 스위칭 주파수는 IC가 고정 주파수 피크 전류 제어 모드에서 제어 루프 대역폭을 수백 kHz 범위 중반으로 푸시할 수 있도록 합니다. 또한 과도 응답을 방해하는 여러 미세 요소들을 완화하기 위해 다양한 혁신이 적용되었습니다.

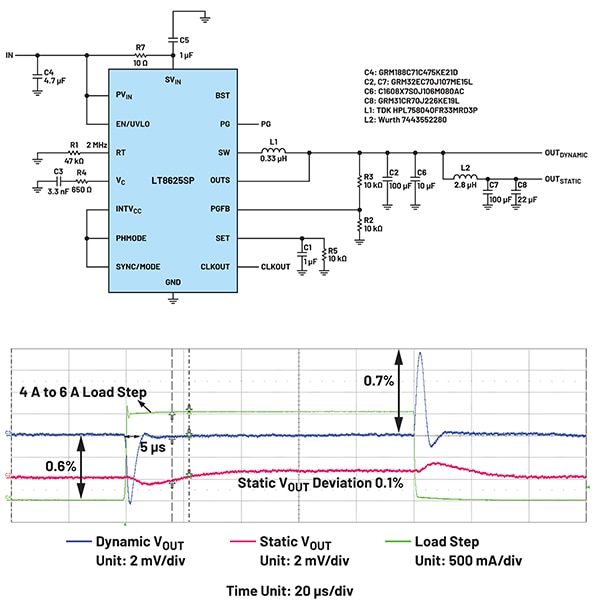

부하 분리 - 일반 설계에서, 1V 부하는 송신 및 수신 회로, 로컬 발진기(LO), 전압 제어 발진기(VCO)로 구성됩니다. 송신/수신 부하는 주파수 분할 듀플렉스(FDD) 작동 동안 부하 전류의 갑작스러운 변화를 경험합니다. 동시에, LO 및 VCO는 일정한 부하를 나타내지만 높은 정확도와 낮은 잡음이 요구됩니다.

이러한 장치의 높은 대역폭을 통해 설계자는 두 번째 인덕터(L2)로 동적 및 정적 부하를 분리하는 방식으로 조정기 IC에서 2개의 중요 1V 부하 그룹에 전력을 제공할 수 있습니다(그림 2, 상단). 부하 과도 응답이 빠르고, VOUT 편차가 최소한으로 유지되며 정적 부하에 영향을 미치지 않습니다(그림 2, 하단).

그림 2: 성능 개선을 위해 인덕터(L2)를 통해 동적 및 정적 RF 부하를 분리하는 Silent Switcher에 대한 응용 회로(상단). 부하 과도 응답이 빠르고 VOUT 편차가 최소한으로 유지되며 정적 부하에 영향을 미치지 않습니다(하단)(이미지 출처: Analog Devices).

그림 2: 성능 개선을 위해 인덕터(L2)를 통해 동적 및 정적 RF 부하를 분리하는 Silent Switcher에 대한 응용 회로(상단). 부하 과도 응답이 빠르고 VOUT 편차가 최소한으로 유지되며 정적 부하에 영향을 미치지 않습니다(하단)(이미지 출처: Analog Devices).

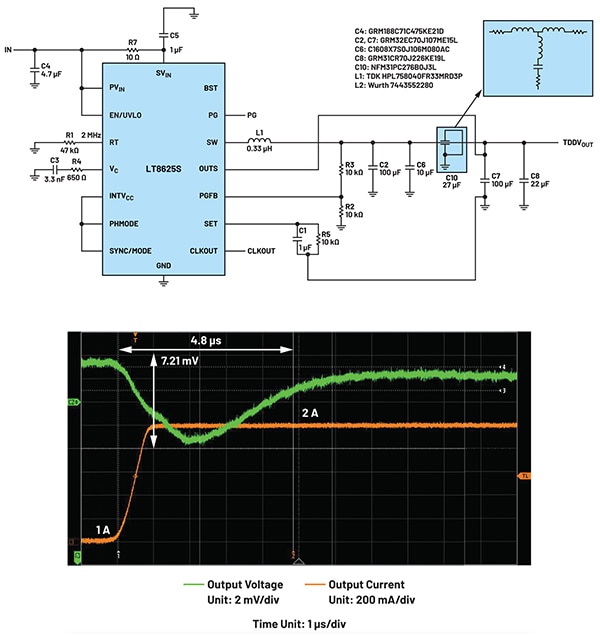

최소화된 등가 유도 용량에서의 포스트 필터링 - 시분할 듀플렉스(TDD) 모드에서는 송신/수신 모드 변환에 따라 잡음에 민감한 LO와 VCO에 부하가 걸리거나 해제됩니다. 따라서, 모든 부하가 동적으로 고려되므로 간소화된 회로를 사용할 수 있습니다. 그러나 이와 동시에, LO와 VCO의 낮은 리플 및 잡음 특징을 유지하기 위해 더 정밀한 포스트 필터링이 필요합니다.

3단자 커패시터를 피드스루 모드에서 사용하면 등가 유도 용량을 최소화하면서 충분한 포스트 필터링을 달성할 수 있어, 부하 과도 현상에 대해 빠른 대역폭을 유지할 수 있습니다(그림 3, 상단). 피드스루 커패시터는 원격 측의 출력 커패시터와 함께 2개의 추가적인 인덕터-커패시터(LC) 필터 스테이지를 형성합니다. 3단자 커패시터의 등가 직렬 유도 용량(ESL)으로 기인되는 전체 유도 용량은 매우 작으며 부하 과도 현상에 미치는 영향이 적습니다. 피드스루 커패시터는 과도 응답을 개선하면서 출력 전압 리플을 최소화합니다(그림 3, 하단).

그림 3: 통합된 동적/정적 RF 부하에 대한 응용 회로로, 부하 과도 현상에 대해 빠른 대역폭을 유지하기 위해 3단자 피드스루 커패시터(오른쪽 상단 코너)를 사용하여 등가 유도 용량이 최소화된 상태에서 포스트 필터링을 제공합니다. 피드스루 커패시터는 과도 응답을 개선하면서 출력 전압 리플을 최소화합니다(이미지 출처: Analog Devices).

그림 3: 통합된 동적/정적 RF 부하에 대한 응용 회로로, 부하 과도 현상에 대해 빠른 대역폭을 유지하기 위해 3단자 피드스루 커패시터(오른쪽 상단 코너)를 사용하여 등가 유도 용량이 최소화된 상태에서 포스트 필터링을 제공합니다. 피드스루 커패시터는 과도 응답을 개선하면서 출력 전압 리플을 최소화합니다(이미지 출처: Analog Devices).

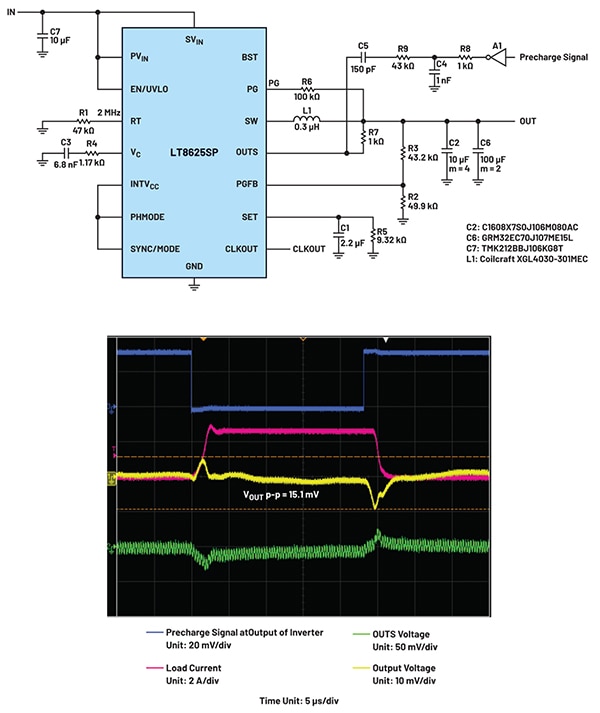

사전 충전 - 경우에 따라 신호 처리 장치에는 범용 I/O(GPIO)가 있습니다. 또한 신호 처리가 예약되어 있으며 과도 이벤트를 미리 알 수 있습니다. 이는 일반적으로 일부 FPGA 전원 공급 장치 설계에서 발생하며, 이러한 설계의 경우 공급 장치의 과도 응답에 전력을 공급하기 위해 사전 충전 신호가 생성될 수 있습니다.

일반적인 응용 회로에서(그림 4, 상단), FPGA가 실제 부하 전에 바이어스를 제공하기 위해 사전 충전 신호를 생성하는 경우, 이 전이를 통해 장치가 최소한의 VOUT 편차와 회복 시간으로 부하 외란을 수용할 수 있는 추가 시간을 갖을 수 있습니다(그림 4, 하단).

그림 4: 빠른 과도 응답을 제공하기 위해 사전 충전 신호가 오차 증폭기의 네거티브 입력 핀(OUTS)으로 공급됩니다. 조정기의 피드백은 사전 충전 신호와 부하 과도 현상의 영향을 받습니다(하단)(이미지 출처: Analog Devices).

그림 4: 빠른 과도 응답을 제공하기 위해 사전 충전 신호가 오차 증폭기의 네거티브 입력 핀(OUTS)으로 공급됩니다. 조정기의 피드백은 사전 충전 신호와 부하 과도 현상의 영향을 받습니다(하단)(이미지 출처: Analog Devices).

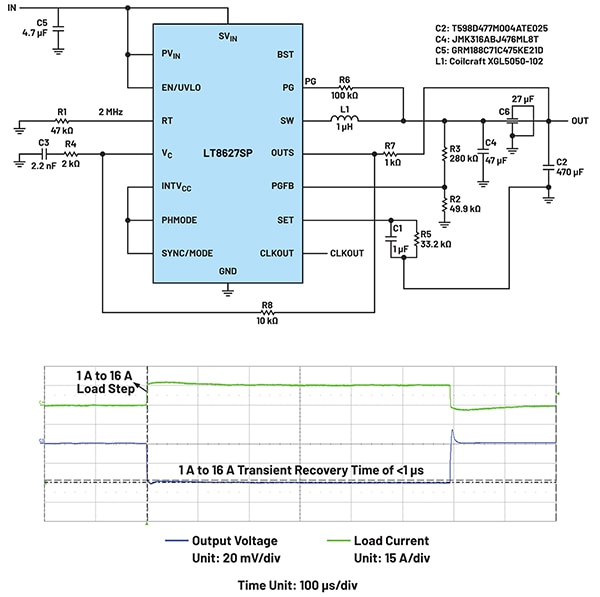

능동 드루핑 - 빔 형성기 응용 제품에서(그림 5, 상단), 공급 전압은 다양한 전력 레벨을 수용하기 위해 계속적으로 변경됩니다. 따라서 공급 전압에 대한 정확도 요구 사항은 대개 5% ~ 10%입니다. 이 경우, 부하 과도 동안 회복 시간을 최소화하면 데이터 처리 효율성이 최대화되기 때문에 전압 정확도보다 안정성이 더 중요합니다. 이 경우 드루핑 회로가 매우 적절한데, 드루핑 전압이 회복 시간을 줄이거나 심지어 제거할 수도 있기 때문입니다.(그림 5, 하단).

그림 5: OUTS와 VC 사이에 능동 드루핑 저항기(R8)를 배치하면 빠른 과도 회복을 달성할 수 있습니다(상단). 드루핑 과도 응답은 과도 회복 시간을 최소화하도록 지정되었습니다(하단)(이미지 출처: Analog Devices).

그림 5: OUTS와 VC 사이에 능동 드루핑 저항기(R8)를 배치하면 빠른 과도 회복을 달성할 수 있습니다(상단). 드루핑 과도 응답은 과도 회복 시간을 최소화하도록 지정되었습니다(하단)(이미지 출처: Analog Devices).

혁신을 구현하고 검증하는 장치

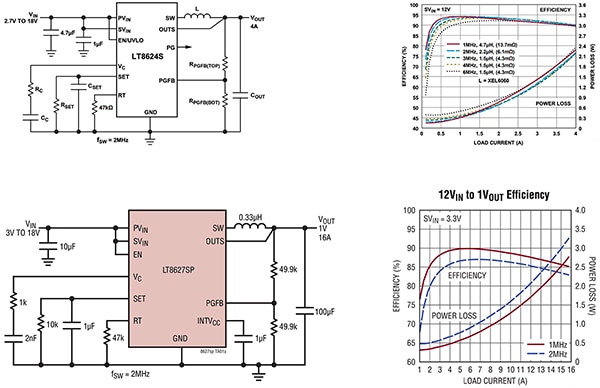

이러한 잡음-감소 및 과도-향상 개념은 모놀리식 Silent Switcher 3 장치 제품군으로 통합되었습니다. 이 제품군은 광범위한 전압 및 전류 최대값을 지원하며, 사용자에게 유연성 및 성능을 모두 제공합니다. LT8622SAV#PBF(그림 6, 상단) 및 LT8627SPJV#TRPBF(그림 6, 하단)의 두 가지 예를 통해 이를 명확하게 확인할 수 있습니다.

전류 및 전력 범위의 하한에 속하는 LT8622SAV#PBF는 2.7V ~ 18V의 입력을 위한 2A 연속-출력 스위처입니다. 이 스위처는 0V ~ (VIN - 0.5)V의 출력 전압 범위를 가지며, 이 범위는 단일 저항기를 통해 프로그래밍할 수 있습니다. 출력-전류 범위 대부분에서 효율성은 최소 90%, 최대 95%입니다.

그림 6: 일반적인 응용 구성의 2A LT8622로 해당 효율성 및 전력 손실 곡선이 함께 표시되어 있습니다(상단). 참고: LTC8624의 회로도는 LT8622의 회로도와 동일한 곡선을 나타내지만 4A 정격을 가집니다. 16A LT8627에 대한 동일한 정보도 표시되어 있습니다(하단)(이미지 출처: Analog Devices).

그림 6: 일반적인 응용 구성의 2A LT8622로 해당 효율성 및 전력 손실 곡선이 함께 표시되어 있습니다(상단). 참고: LTC8624의 회로도는 LT8622의 회로도와 동일한 곡선을 나타내지만 4A 정격을 가집니다. 16A LT8627에 대한 동일한 정보도 표시되어 있습니다(하단)(이미지 출처: Analog Devices).

LT8622SAV#PBF는 스위칭 조정기에서 초저주파(0.1Hz ~ 100kHz) 출력 잡음 성능을 제공하며 RMS 잡음이 4μVRMS에 불과합니다. 작동 주파수는 조정이 가능하며 300kHz ~ 6MHz에서 동기화될 수 있습니다. 이 장치는 작은 4mm × 3mm 크기의 20리드 LQFN 패키지로 제공됩니다.

더 높은 전력의 16A LT8627SPJV#TRPBF는 2.8V ~ 18V의 입력 전압을 지원하며 출력 전압은 0V ~ (VIN - 0.5)V의 범위 내에서 저항기를 통해 조정이 가능합니다. 효율성은 80%를 초과하며 중간 범위 스위트 스팟에서는 90%를 달성합니다(1MHz 스위칭 주파수 기준). 저주파 출력 잡음 성능은 2A LT8622SAV#PBF와 동일합니다.

작동 주파수도 조정 가능하며 300kHz ~ 4MHz에서 작동 및 동기화할 수 있습니다. 이 범위는 더 낮은 전류 모델보다 낮은 것입니다. 이 장치의 패키지는 선택적 방열판을 위해 뒷면이 노출되어 있는, 약간 더 큰 24리드 4mm × 4mm LQFN입니다.

결론

특히 최첨단 RF 분야의 혁신적 제품 설계자는 효율성을 요구하지만, 공급 전압에 대한 낮은 잡음과 빠른 과도 응답이 동반되어야 합니다. Analog Devices Silent Switcher 3 제품군의 DC/DC 조정기는 다양한 응용 분야에 걸쳐 잡음에 민감한 동적 부하 과도 성능에 최적화된 차세대 고효율 모놀리식 장치입니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.