코프로세서 아키텍처: 빠른 시제품 제작을 위한 내장형 시스템 아키텍처

2021-07-06

편집자 주 - 디지털 처리 성능과 처리량은 잘 알려져 있지만 코프로세서 아키텍처는 내장형 시스템 설계자에게 프로젝트 관리 전략을 구현하여 개발 비용을 절감하면서 출시 시간을 단축할 수 있는 기회를 제공합니다. 이 기사에서는 특히 이산 소자 마이크로 컨트롤러(MCU)와 이산 소자 현장 프로그래밍 가능 게이트 어레이(FPGA) 조합을 중심으로 이 아키텍처가 효율적이고 반복적인 설계 프로세스에 얼마나 적합한지를 보여줍니다. 연구 출처, 경험적 결과 및 사례 연구를 활용하여 이 아키텍처의 이점을 탐구하고 모범적인 응용 분야를 제시합니다. 이 기사를 읽고 나면 내장형 시스템 설계자가 해당 다목적 하드웨어 아키텍처를 구현할 시기와 방법을 더 잘 이해하게 될 것입니다.

소개

내장형 시스템 설계자는 설계 제약 조건, 성능 기대치, 일정 및 예산 문제로 인해 어려움을 겪고 있습니다. 이는 현대 프로젝트 관리에 반하지만 "빠른 오류", "민첩", "미래에 대비하는 IT", "파격적"이라는 이 역할의 불안정한 특성을 강조합니다. 이러한 기대치를 만족시키려는 애처로운 노력은 참혹할 정도이지만, 시장 전반에서 강화되어 왔고 앞으로도 그럴 것입니다. 이에 필요한 것은 혁신적인 반복 프로세스를 구현할 수 있는 설계 방식이며 대부분의 내장형 시스템과 마찬가지로 이는 하드웨어 아키텍처에서 시작됩니다.

마이크로 컨트롤러 장치(MCU)와 현장 프로그래밍 가능 게이트 어레이(FPGA) 기술을 강점을 합쳐놓은 하드웨어 아키텍처인 코프로세서 아키텍처는 내장형 설계자에게 아무리 까다로운 요구 사항도 충족할 수 있는 프로세스를 제공하는 동시에, 알려진 문제와 알려지지 않은 문제를 모두 해결하는 데 필요한 유연성을 제공합니다. 설계자는 반복적으로 조정 가능한 하드웨어를 제공하여 진행 상황을 보여주고, 중요한 이정표를 세우고, 빠른 시제품 제작 프로세스를 최대한 활용할 수 있습니다.

이 프로세스 내에는 개발 노력에 각각 고유한 가치를 더해줄 핵심 프로젝트 이정표가 있습니다. 이 기사에서는 이러한 용어로 마이크로 컨트롤러를 통한 디지털 신호 처리 이정표, 마이크로 컨트롤러를 통한 시스템 관리 이정표 및 제품 배포 이정표가 사용됩니다.

이 기사의 결론은 유연한 하드웨어 아키텍처가 경직된 방식보다 현대 내장형 시스템에 더 적합할 수 있다는 것을 보여줍니다. 뿐만 아니라 이 접근 방식은 프로젝트 비용과 출시 시간을 모두 개선할 수 있습니다. 이 입장을 고수하기 위해 주장, 제공된 예시 및 사례 연구를 사용합니다. 이 아키텍처가 제공하는 설계 유연성에서 각 이정표의 가치를 관찰해보면 적응형 하드웨어 아키텍처가 내장형 시스템 설계를 추진하는 강력한 원동력이라는 것을 알 수 있습니다.

코프로세서 아키텍처의 강점 탐구: 설계 유연성 및 고성능 처리

FPGA 설계는 일반적으로 고속 아날로그 디지털 컨버터(ADC)와 직접 연결하는 데 사용됩니다. 신호를 디지털화하고 FPGA로 판독한 다음 일부 디지털 신호 처리(DSP) 알고리즘을 이 신호에 적용합니다. 그러면 FPGA는 결과에 따라 결정을 내립니다.

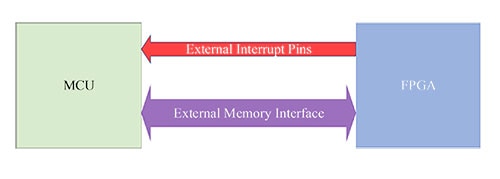

이러한 응용 분야가 이 기사에서 예제로 사용됩니다. 또한 그림 1은 MCU와 FPGA가 MCU의 외부 메모리 인터페이스를 통해 연결되는 일반적인 코프로세서 아키텍처를 보여줍니다. FPGA는 외부 SRAM(Static Random-Access Memory)의 일부인 것처럼 간주됩니다. 신호는 FPGA에서 MCU로 다시 전달되며 하드웨어 인터럽트 라인 및 상태 표시기 역할을 합니다. 신호를 사용하여 FPGA에서 MCU에 중요한 상태를 나타낼 수 있습니다. 예를 들어, ADC 변환이 준비되었거나, 오류가 발생했거나, 다른 중요 이벤트가 발생했다고 알려줍니다.

그림 1: 일반 코프로세서 구성도(MCU + FPGA). (이미지 출처: CEPD)

그림 1: 일반 코프로세서 구성도(MCU + FPGA). (이미지 출처: CEPD)

코프로세서 접근 방식의 강점은 위에 언급한 각 이정표의 결과물 내에 가장 잘 나타난다는 것입니다. 작업 또는 단계의 성과를 나열하고 성과를 가능하게 해준 지원을 평가하여 가치를 평가합니다. 다음 질문에 대답하면 이정표의 결과에 대한 전체적인 가치를 평가하는 데 도움이 됩니다.

- 프로젝트 종속성과 병목 현상이 제거되면 다른 팀원의 진행 상황이 지속적으로 빨라질 수 있습니까?

- 이정표의 성과가 병렬 실행 경로를 어떻게 지원합니까?

마이크로 컨트롤러를 통한 디지털 신호 처리 이정표

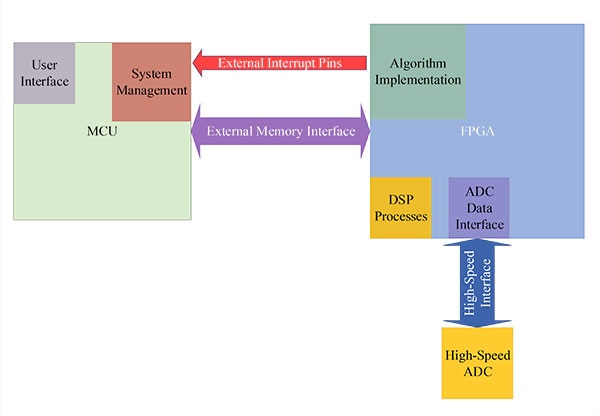

그림 2: 아키텍처 - 마이크로 컨트롤러를 통한 디지털 신호 처리 (이미지 출처: CEPD)

그림 2: 아키텍처 - 마이크로 컨트롤러를 통한 디지털 신호 처리 (이미지 출처: CEPD)

이 하드웨어 아키텍처에서 MCU의 전면 중앙 배치를 허용하는 첫 번째 개발 단계입니다. 모든 조건이 그대로라면 MCU 및 실행 가능한 소프트웨어 개발은 FPGA 및 하드웨어 기술 언어(HDL) 개발보다 더 적은 리소스와 시간이 소요됩니다. 따라서 MCU를 주 프로세서로 사용하여 제품 개발을 초기화하면 알고리즘을 더 빠르게 구현, 테스트 및 검증할 수 있습니다. 그러면 알고리즘 버그와 논리 버그를 설계 프로세스의 조기에 발견하고, 신호 체인의 상당 부분을 테스트 및 검증할 수 있습니다.

이 초기 이정표에서 FPGA는 고속 데이터 수집 인터페이스 역할을 합니다. 즉, 고속 ADC에서 데이터를 안정적으로 파이핑하고, MCU에 데이터가 사용 가능한지 알려주고, MCU의 외부 메모리 인터페이스에 이 데이터를 제공합니다. 이 역할은 HDL 기반 DSP 프로세스 또는 다른 알고리즘 구현을 포함하지 않지만, 그럼에도 불구하고 매우 중요합니다.

이 단계에서 수행되는 FPGA 개발은 제품 개발 노력과 시장 출시 모두에서 제품의 궁극적인 성공을 위한 토대를 구축합니다. 하위 수준 인터페이스에만 집중하여 중요한 작업을 테스트하는 데 적절한 시간을 배정할 수 있습니다. FPGA가 이 인터페이스 역할을 안정적이고 확실하게 수행하는 것만으로도 이 이정표를 자신 있게 결론지을 수 있습니다.

이 초기 이정표의 주요 결과에는 다음과 같은 이점이 포함됩니다.

- 전체 신호 경로(모든 증폭, 감쇠, 변환)를 테스트하고 검증합니다.

- 처음에 소프트웨어(C/C++)에서 알고리즘을 구현하여 프로젝트 개발 시간과 노력을 줄일 수 있습니다. 이는 향후 설계 단계를 승인하기 전에 이 프로젝트의 실효성을 확인해야 하는 경영진과 다른 이해관계자에게 매우 중요합니다.

- C/C++에서 알고리즘을 구현하면서 배운 내용을 소프트웨어-HDL 도구(예: Xilinx HLS)를 사용하여 HDL 구현에 직접 적용할 수 있습니다.

마이크로 컨트롤러를 통한 시스템 관리 이정표

그림 3: 아키텍처 - 마이크로 컨트롤러를 통한 시스템 관리 (이미지 출처: CEPD)

그림 3: 아키텍처 - 마이크로 컨트롤러를 통한 시스템 관리 (이미지 출처: CEPD)

이 코프로세서 접근 방식의 두 번째 개발 단계에서는 DSP 프로세스 및 알고리즘 구현을 MCU에서 FPGA로 이동합니다. FPGA는 여기서도 고속 ADC 인터페이스를 담당하지만, 다른 역할을 가정하여 FPGA에서 제공되는 속도 및 병렬화가 최대한 활용됩니다. 또한 MCU와 달리 DSP 프로세스 및 알고리즘 채널의 여러 인스턴스가 동시에 구현되어 실행될 수 있습니다.

MCU 구현에서 배운 교훈에 기반하여 설계자는 자신 있게 다음 이정표를 진행할 수 있습니다. 앞서 언급한 Xilinx의 Vivado HLS와 같은 도구는 실행 가능한 C/C++ 코드를 합성 가능한 HDL로 기능적으로 변환합니다. 이제 타이밍 제약 조건, 프로세스 파라미터 및 기타 사용자 환경 설정을 정의하고 구현해야 하지만, 핵심 기능은 유지된 상태로 FPGA 패브릭으로 변환됩니다.

이 이정표에서 MCU는 시스템 관리자 역할을 합니다. MCU는 FPGA 내부의 상태 및 제어 레지스터를 모니터링, 업데이트 및 보고합니다. 또한 MCU는 사용자 인터페이스(UI)를 관리합니다. 이 UI는 이더넷 또는 Wi-Fi 연결을 통해 액세스되는 웹 서버의 형태로 제공되거나, 사용 지점에서 사용자에게 액세스 권한을 부여하는 산업용 터치스크린 인터페이스로 제공될 수 있습니다. MCU의 새롭고 구체화된 역할에서 중요한 점은 컴퓨팅 집약적인 처리 작업을 완화하여 이제 MCU와 FPGA가 모두 적합한 작업에서 활용되고 있다는 것입니다.

이 이정표의 주요 결과에는 다음과 같은 이점이 포함됩니다.

- FPGA에 의해 DSP 프로세스 및 알고리즘 구현이 빠르게 병렬 실행됩니다.MCU는 응답성이 뛰어나고 간소화된 UI를 제공하고 제품 프로세스를 관리합니다.

- MCU 내에서 처음으로 개발되어 검증을 거쳤으므로 알고리즘 위험이 완화되고 합성 가능한 HDL로 변환됩니다. Vivado HLS와 같은 도구를 사용하여 이 변환을 보다 쉽게 진행할 수 있습니다. 또한 Vivado 설계 제품군과 같은 통합 시뮬레이션 도구를 통해 FPGA 관련 위험을 완화할 수 있습니다.

- 프로세스를 FPGA로 이동하여 이해관계자가 큰 위험에 노출되지 않습니다. 대조적으로 FPGA의 속도 및 병렬화 이점이 제공됩니다. 측정 가능한 성능 향상이 관찰되며 이제 이 설계에서 제조를 준비하는 데 집중할 수 있습니다.

제품 배포 이정표

FPGA에서 컴퓨팅 집약적인 프로세스를 해결하고 MCU에서 시스템 관리 및 사용자 인터페이스 역할을 처리하여 제품을 배포할 준비가 되었습니다. 이 논문에서는 알파 및 베타 릴리스 우회를 제안하지는 않지만, 이 이정표에서는 제품 배포를 위해 코프로세서 아키텍처가 제공하는 기능에 중점을 둡니다.

MCU와 FPGA는 모두 현장 업데이트 가능한 장치입니다. 많은 발전이 이루어져서 FPGA 업데이트가 소프트웨어 업데이트만큼 액세스하기 쉬워졌습니다. 또한 FPGA가 MCU의 어드레서블 메모리 공간 내에 있으므로 MCU는 전체 시스템에 대한 액세스 포인트 역할을 할 수 있습니다. 즉, 자체 업데이트와 FPAG용 업데이트를 모두 수신할 수 있습니다. 최종 사용자별로 조건에 따라 업데이트를 예약, 배포 및 맞춤 설정할 수 있습니다. 사용자 및 사용 사례 로그를 유지 관리하고 특정 빌드 구현과 연결할 수 있습니다. 이 데이터 세트에서 제품을 현장에 배치한 이후에도 성능을 지속적으로 상술하고 개선할 수 있습니다.

이 종합 시스템 업데이트 가능성의 강점이 공간 기반 응용 분야만큼 명확하지는 않습니다. 제품이 출시되고 나면 유지보수와 업데이트를 원격으로 수행해야 합니다. 이는 변화하는 논리 조건만큼 간단할 수도 있지만, 통신 변조 체계를 업데이트하는 것만큼 복잡할 수도 있습니다. FPGA 기술에서 제공되는 프로그래밍 가능성과 코프로세서 아키텍처는 이 기능 범위를 전체적으로 수용하면서 방사선 내성 강화 부품을 선택할 수 있습니다.

마지막으로 이 이정표는 점진적으로 비용이 감소됩니다. 비용 절감, 부품 명세서(BOM) 변경 및 기타 최적화가 이 이정표에서 나타날 수도 있습니다. 현장 배포 중에 저렴한 MCU 또는 성능이 낮은 FPGA에서도 제품이 잘 작동한다는 것을 알 수 있습니다. 코프로세서로 인해 아키텍처 설계자는 응용 제품의 요구 사항을 초과하는 기능을 제공하는 부품에 집착하지 않아도 됩니다. 또한 부품을 구입할 수 없는 경우 아키텍처에서 새 부품을 설계에 통합할 수 있습니다. 제품 프로세스를 모두 처리하려고 시도하는 고성능 DSP 또는 MCU나 단일 칩 시스템온칩(SoC) 아키텍처에서는 그렇지 않습니다. 코프로세서 아키텍처는 기능과 유연성을 효율적으로 조율하여 개발 단계와 출시 과정에서 설계자에게 더 많은 선택지와 자유를 제공합니다.

연구 및 관련 사례 연구 지원

위성 통신 예

간단히 말해서 코프로세서의 가치는 작업을 하드웨어에서 실행하여 가속화 및 간소화 혜택을 누릴 수 있도록 주 처리 장치를 오프로드하는 것입니다. 그런 설계는 컴퓨팅 속도와 기능을 개선하고, 이 기사에서 언급한 대로 개발 비용을 절감하고 개발 시간을 단축하는 이점이 있습니다. 우주통신 시스템 영역은 이러한 혜택이 가장 매력적인 영역 중 하나입니다.

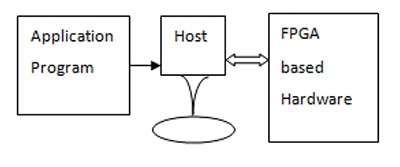

간행물 FPGA based hardware as coprocessor에서 G. Prasad 및 N. Vasantha는 주문형 반도체(ASIC)의 초기 개발비(NRE) 또는 하드 아키텍처 프로세스의 응용 분야별 제한 없이 PFGA 내부 데이터 처리에 위성통신 시스템의 컴퓨팅 요구 사항이 결합되는 방식을 자세히 설명합니다. 마이크로 컨트롤러를 통한 디지털 신호 처리 이정표에서 설명한 대로 설계는 대부분의 컴퓨팅 집약적 알고리즘을 수행하는 응용 프로세서에서 시작됩니다. 이 시작 지점에서는 중앙 처리 장치(CPU)에서 대부분의 클록 주기를 소비하는 소프트웨어의 주요 섹션을 파악한 후 해당 섹션을 HDL 구현으로 마이그레이션합니다. 그래픽 표현은 지금까지 살펴본 것과 매우 유사하지만, 응용 프로그램을 독립 블록으로 나타내도록 선택하여 호스트(프로세서) 또는 FPGA 기반 하드웨어에서 실현될 수 있습니다.

그림 4: 위성통신 예에서 사용된 응용 프로그램, 호스트 프로세서 및 FPGA 기반 하드웨어

그림 4: 위성통신 예에서 사용된 응용 프로그램, 호스트 프로세서 및 FPGA 기반 하드웨어

PCI(Peripheral Component Interconnect) 인터페이스와 호스트 프로세서의 직접 메모리 액세스(DMA)를 활용하면 주변 장치 성능이 획기적으로 향상됩니다. 대부분은 랜덤화 해제 프로세스의 향상에 기인합니다. 이 프로세스를 호스트 프로세서의 소프트웨어에서 실행할 경우 시스템의 실시간 응답에 병목 현상이 발생했습니다. 하지만 FPGA로 이동하면 다음과 같은 이점이 제공됩니다.

- 랜덤화 해제 프로세스가 병목 현상 없이 실시간으로 실행됩니다.

- 호스트 프로세서의 컴퓨팅 오버헤드가 획기적으로 감소되어 이제 원하는 로깅 역할을 효율적으로 수행할 수 있습니다.

- 전체 시스템의 전체 성능이 향상됩니다.

모든 이점은 ASIC 관련 비용 없이 실현되며 프로그래밍 가능 논리[5]의 유연성이 보장됩니다. 위성통신은 많은 문제점이 있지만 이 방식을 사용하면 이러한 요구 사항을 충족하고 설계 유연성을 지속적으로 제공할 수 있습니다.

자동차 인포테인먼트 예

자동차 내부 엔터테인먼트 시스템은 안목 있는 소비자를 위한 차별화 기능입니다. 대부분의 자동차 전자 장치와 달리 이 장치는 눈에 쉽게 띄고 탁월한 응답 시간과 성능을 제공할 것으로 기대됩니다. 하지만 설계자는 설계의 현재 요구 사항과 미래에 요구되는 유연성 사이에서 종종 압박을 받게 됩니다. 이 예에서는 신호 처리 및 무선 통신의 구현 요구 사항을 사용하여 코프로세서 하드웨어 아키텍처의 강점을 강조합니다.

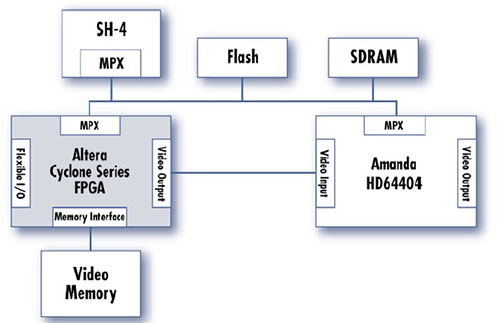

Delphi Delco Electronics Systems corporation에서 게시한 기본적인 자동차 엔터테인먼트 시스템 아키텍처 중 하나를 사용했습니다. 이 아키텍처에서는 Hitachi의 HD64404 Amanda 주변 장치인 컴패니언 ASIC가 실장된 SH-4 MCU를 채택했습니다. 이 아키텍처는 자동차 시장의 기준 엔터테인먼트 기능의 75% 이상을 충족하지만, 비디오 처리 응용 제품 및 무선 통신을 처리하는 기능이 부족했습니다. 이 기존 아키텍처에 FPGA를 포함하여 이 기존 설계 방식에 유연성과 기능을 추가할 수 있습니다.

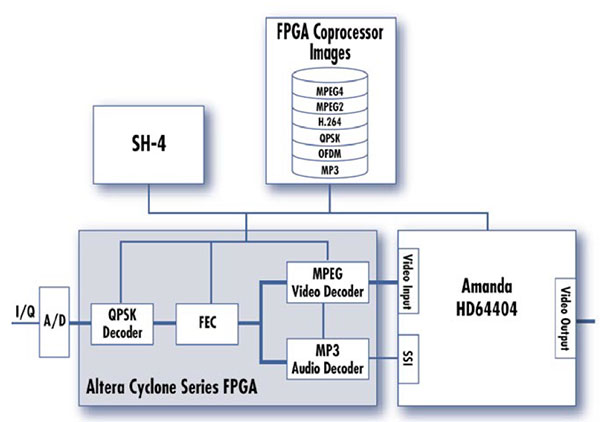

그림 5: infotainment의 FPGA 코프로세서 아키텍처 예제 1.

그림 5: infotainment의 FPGA 코프로세서 아키텍처 예제 1.

그림 5 아키텍처는 비디오 처리와 무선 통신 관리 모두에 적합합니다. DSP 기능을 FPGA에 푸시하여 Amanda 프로세서는 시스템 관리 역할을 수행하고 무선 통신 스택을 구현할 수 있습니다. Amanda와 FPGA가 모두 외부 메모리에 액세스할 수 있으므로, 시스템의 프로세서와 부품 간에 데이터를 빠르게 교환할 수 있습니다.

그림 6: infotainment의 FPGA 코프로세서 아키텍처 예제 2.

그림 6: infotainment의 FPGA 코프로세서 아키텍처 예제 2.

그림 6의 두 번째 인포테인먼트는 수신되는 고속 아날로그 데이터와 비디오 응용 분야에 필요한 압축 및 인코딩을 모두 처리할 수 있는 FPGA의 기능을 강조합니다. 실제로 모든 기능을 FPGA로 푸시하고 병렬 처리를 통해 실시간으로 처리할 수 있습니다.

기존 하드웨어 아키텍처에 FPGA를 포함하여 기존 하드웨어의 검증된 성능을 유연성 및 미래에 대비한 경쟁력과 결합할 수 있습니다. 기존 시스템 내에서도 코프로세서 아키텍처는 설계자에게 다른 아키텍처에서 제공하지 않는 선택 옵션을 제공합니다[6].

빠른 시제품 제작 이점

빠른 시제품 제작 프로세스에서는 특히 프로젝트의 중요 경로 내에서 작업을 병렬로 실행하고, "버그" 및 설계 문제를 빠르게 식별하고 데이터 및 신호 경로를 검증하여 많은 제품 개발 영역을 포괄합니다. 하지만 이 프로세스에서 간소화되고 효과적인 결과를 얻으려면 필요한 프로젝트 영역에 대한 충분한 전문 지식이 있어야 합니다.

기본적으로 하드웨어 엔지니어, 내장형 소프트웨어 또는 DSP 엔지니어, HDL 엔지니어가 있어야 합니다. 이제 여러 역할을 충족할 수 있는 여러 분야에 정통한 전문가들이 많이 있지만, 프로젝트에서 이러한 노력을 조율하기 위한 부담은 여전히 존재합니다.

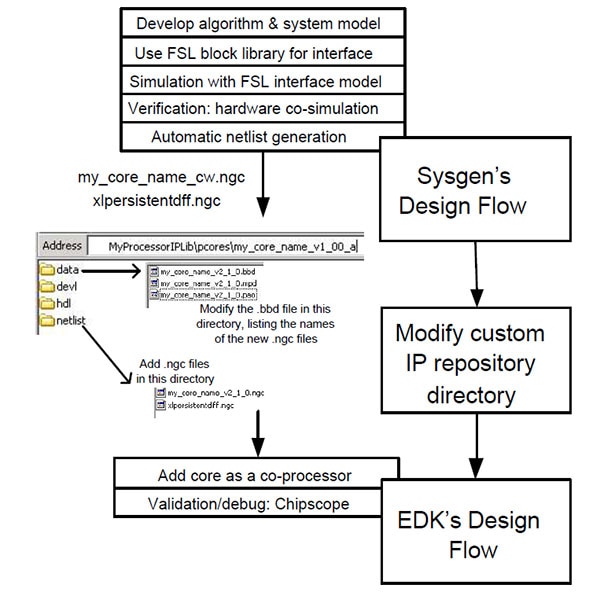

논문 An FPGA based rapid prototyping platform for wavelet coprocessors에서 저자는 코프로세서 아키텍처를 사용하면 단일 DSP 엔지니어가 모든 역할을 효과적이고 효율적으로 이행할 수 있다고 강조했습니다. 이 연구에서 팀은 MATLAB의 Simulink 도구 내에서 원하는 DSP 기능의 설계와 시뮬레이션을 시작했습니다. 이 도구는 두 가지 기본 기능을 처리했습니다. 즉 1) 시뮬레이션을 통해 원하는 성능을 확인하고 2) 향후에 선택할 설계 옵션을 비교하고 참조할 수 있는 기준을 설정했습니다.

시뮬레이션 후 중요 기능을 파악하여 여러 코어로 나누었습니다. 바로 FPGA 내에서 합성할 수 있는 소프트 코어 부품 및 프로세서입니다. 이 작업에서 가장 중요한 단계는 코어와 부품 사이의 인터페이스를 정의하고 데이터 교환 성능을 원하는 시뮬레이션 성능과 비교하는 것이었습니다. 이 설계 프로세스는 내장형 시스템의 Xilinx 설계 흐름과 밀접한 관련이 있으며 아래 그림 7에 요약되어 있습니다.

그림 7: 구현 설계 흐름

그림 7: 구현 설계 흐름

시스템을 합성 가능한 코어로 분할하여 DSP 엔지니어는 신호 처리 체인의 가장 중요한 측면에 집중할 수 있습니다. 또한 FPGA 내에서 다른 소프트 코어 프로세서 또는 부품을 수정하거나, 배선하거나, 구현하기 위해 하드웨어 또는 HDL에 대한 전문 지식이 필요하지 않습니다. 설계자가 인터페이스와 데이터 형식만 알고 있다면 신호 경로를 완벽하게 제어하고 시스템 성능을 세분화할 수 있습니다.

경험적 결과 – 이산 소자 코사인 변환 사례 연구

경험적 결과는 내장형 시스템 설계자의 코프로세서 아키텍처에 필요한 유연성을 확인하고, 현대 FPGA 도구에 사용 가능한 성능 향상 옵션을 보여 줍니다. 앞서 언급한 것과 같은 향상이 다른 하드웨어 아키텍처에는 제공되지 않거나 영향이 감소될 수 있습니다. 이산 소자 코사인 변환(DCT)을 컴퓨팅 집약적인 알고리즘으로 선택하고, C 기반 구현부터 HDL 기반 구현까지 진행 상황을 결과의 중심에 두었습니다. 이 알고리즘은 패턴 인식 및 필터링을 위한 신호 처리에 사용되므로 DCT를 선택했습니다[8]. 경험적 결과는 저자와 동료들이 2020년~2021년에 Xilinx 제휴 파트너 인증을 받기 위해 실시한 실험실 실습에 기반합니다.

이 작업에 사용된 도구 및 장치는 다음과 같습니다.

- Vivado HLS v2019

- 평가 및 시뮬레이션 장치는 xczu7ev-ffvc1156-2-e입니다.

C 기반 구현부터 시작하여 DCT 알고리즘은 두 16비트 숫자 어레이를 수락합니다. 어레이 “a”는 DCT에 대한 입력 어레이이고, 어레이 “b”는 DCT의 출력 어레이입니다. 따라서 데이터 폭(DW)은 16으로 정의되고 어레이 (N) 내부 요소 수는 1024/DW 또는 64입니다. DCT 행렬의 크기(DCT_SIZE)는 8로 설정됩니다. 즉, 8 x 8 행렬이 사용됩니다.

이 기사의 전제에 따라 C 기반 알고리즘 구현을 사용하면 설계자가 알고리즘 기능을 빠르게 개발하여 검증할 수 있습니다. 중요한 고려 사항이긴 하지만 이 검증에서는 실행 시간보다 기능에 더 높은 가중치를 둡니다. 이 알고리즘의 궁극적인 구현은 하드웨어 가속화, 루프 언롤 및 기타 기술이 즉시 제공되는 FPGA에서 실행되므로 이 가중치 적용은 허용됩니다.

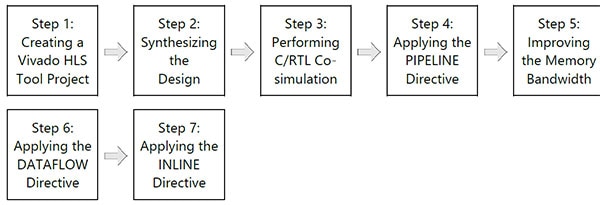

그림 8: Xilinx Vivado의 HLS 설계 흐름

그림 8: Xilinx Vivado의 HLS 설계 흐름

Vivado HLS 도구 내에서 DCT 코드가 프로젝트로 생성된 경우 다음 단계에서는 FPGA 구현에 대한 설계 합성을 시작합니다. 다음 단계에서는 알고리즘 실행을 MCU에서 FPGA로 이동할 경우의 가장 큰 이점 중 일부가 명확해집니다. 참고로 이 단계는 위에서 설명한 마이크로 컨트롤러를 통한 시스템 관리 이정표와 동일합니다.

최신 FPGA 도구를 사용하면 복잡한 알고리즘을 최적화하고 성능을 크게 향상시킬 수 있습니다. 결과를 분석하기 전에 유의해야 할 몇 가지 중요한 용어가 있습니다.

- 대기 시간 – 모든 루프 반복을 실행하는 데 필요한 클록 주기 수[10]

- 간격 – 루프의 다음 반복에서 데이터 처리를 시작하기 이전의 클록 주기 수[11]

- BRAM – Block Random Access Memory

- DSP48E – UltraScale 아키텍처를 위한 디지털 신호 처리 슬라이스

- FF – 플립플롭

- LUT – 대조표

- URAM – Unified Random-Access Memory(단일 트랜지스터로 구성 가능)

|

||||||||||||||||||||||||||||||||||||||||

표 1: FPGA 알고리즘 실행 최적화 결과(대기 시간 및 간격)

|

표 2: FPGA 알고리즘 실행 최적화 결과(리소스 활용률)

기본

기본 최적화 설정은 C 기반 알고리즘을 합성 가능한 HDL로 변환할 때의 변경되지 않는 결과에 기반합니다. 최적화를 사용할 수 없으며, 다른 최적화를 효율적으로 이해하기 위한 성능 참조용으로 사용될 수 있습니다.

파이프라인 내부 루프

PIPELINE 지시문은 기존 데이터가 파이프라인에 있는 동안 새 데이터 처리를 시작할 수 있도록 Vivado HLS에 내부 루프를 언롤하도록 지시합니다. 따라서 새 데이터 처리를 시작하기 전에 기존 데이터가 완료될 때까지 기다릴 필요가 없습니다.

파이프라인 외부 루프

PIPELINE 지시문을 외부 루프에 적용하여 이제 외부 루프 연산이 파이프라이닝됩니다. 하지만 이제 내부 루프 연산이 동시에 실행됩니다. 이 지시문을 외부 루프에 직접 적용하면 대기 시간과 간격이 반으로 감소됩니다.

어레이 분할

이 지시문은 루프 내용을 어레이에 매핑하여 어레이 내 단일 소자에 대한 모든 메모리 액세스를 평면화합니다. 그러면 많은 RAM이 소비되지만 알고리즘 실행 시간이 반으로 단축됩니다.

데이터 흐름

이 지시문을 사용하면 설계자가 각 입력 판독 사이의 대상 클록 주기 수를 지정할 수 있습니다. 이 지시문은 최상위 함수에 대해서만 지원됩니다. 이 수준에 노출되는 루프와 함수에서만 이 지시문을 사용할 수 있습니다.

인라인

INLINE 지시문은 내부와 외부의 모든 루프를 평면화합니다. 이제 행 프로세스와 열 프로세스가 동시에 실행될 수 있습니다. 이 지시문이 더 많은 FPGA 리소스를 소비하더라도 필요한 클록 주기 수는 최소로 유지됩니다.

결론

코프로세서 하드웨어 아키텍처는 내장형 설계자에게 개발 단계부터 제품 출시 이후까지 설계 유연성을 유지하는 고성능 플랫폼을 제공합니다. 먼저 C 또는 C++, 프로세스, 데이터 및 신호 경로에서 알고리즘을 검증하고 상대적으로 짧은 시간 내에 중요 기능을 확인할 수 있습니다. 그러면 프로세서 집약적 알고리즘을 코프로세서 FPGA로 전환하여 설계자가 하드웨어 가속 및 강화된 모듈식 설계의 이점을 누릴 수 있습니다.

부품이 단종되거나 최적화기 필요한 경우 동일한 아키텍처에서 이러한 변경을 허용할 수 있습니다. 인터페이스는 그대로 유지하면서 새 MCU와 새 FPGA를 설계에 적용할 수 있습니다. MCU와 FPGA는 모두 현장에서 업데이트 가능하므로 사용자별 변경 및 최적화를 현장에서 또는 원격으로 적용할 수 있습니다.

마지막으로 이 아키텍처는 MCU의 개발 속도와 가용성을 FPGA의 성능 및 확장성과 결합합니다. 모든 개발 단계에서 최적화 및 성능이 향상되므로 코프로세서 아키텍처는 오늘날의 설계 그 이상에 대해 아무리 까다로운 요구 사항도 충족할 수 있습니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.