동기식 디지털 시스템에서 지연 없는 클록 버퍼를 평가 및 사용하여 타이밍을 보호하는 방법

DigiKey 북미 편집자 제공

2019-07-18

디지털 시스템 성능이 향상되면서 설계자는 클록 분배 타이밍의 차이 또는 불확실성을 방지하기 위해 클록 생성 및 분배 회로 설계에 더욱 세심한 주의를 기울여야 합니다. 이러한 문제는 시스템 성능을 저하하거나, 타이밍 마진을 줄이거나, 기능적인 오류를 발생시킬 수 있습니다. 타이밍 스큐 관련 문제를 방지하기 위해 설계자는 지연 없는 클록 버퍼를 사용할 수 있습니다.

일반 동기식 디지털 시스템에서는 일반 클록을 사용하여 작업을 순차적으로 유지합니다. 시스템이 원하는 속도로 작동하도록 유지하려면 이 클록을 모든 순차적 소자에 배분해야 합니다. 타이밍 스큐를 줄이기 위해 폐쇄 루프 제어를 사용하는 경우가 많습니다. 지연 없는 클록 버퍼에서는 버퍼링된 클록 출력을 레퍼런스 클록 입력에 맞춰서 거의 완벽한 클록 타이밍을 보장하기 위해 위상 고정 루프(PLL)를 사용합니다.

이 기사에서는 지연 없는 클록 버퍼를 설명하고 Cypress Semiconductor, Integrated Device Technology Inc.(IDT) 및 ON Semiconductor의 샘플 솔루션을 사용하여 지연 없는 클록 버퍼를 작동하는 방식을 살펴본 다음 클록 스큐를 제어할 수 있는 방법을 자세히 살펴봅니다. 또한 이러한 장치의 안정성을 보장하는 테스트 방법을 알아봅니다.

클록 스큐

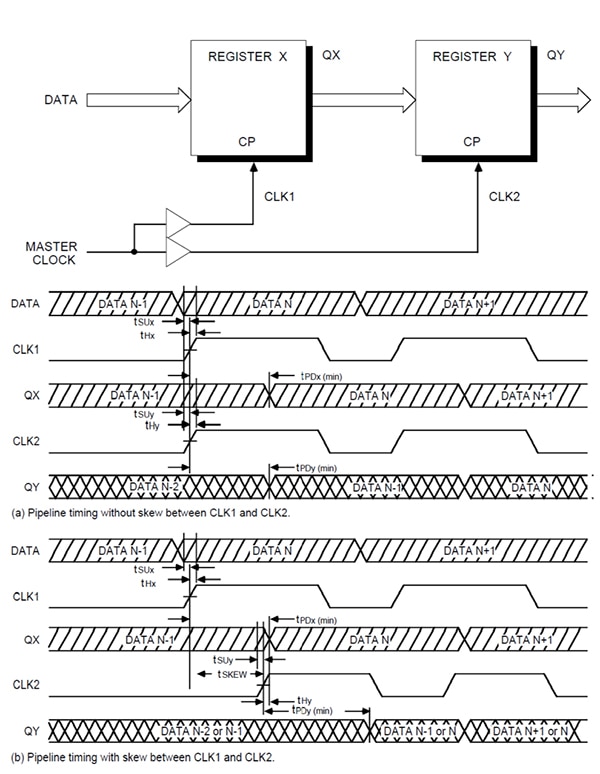

동기식 디지털 시스템에서 회로의 부품마다 클록 도달 시간이 달라서 클록 스큐가 발생할 수 있습니다. 클록 스큐는 타이밍 마진을 줄이고 시스템 고장을 일으킬 수 있습니다(그림 1).

그림 1: 클록 시간 스큐가 파이프라인 레지스터 작동에 미치는 영향을 보여주는 간단한 예입니다. 스큐된 클록은 설정 및/또는 유지 요구 사항을 위반하여 비확정 출력 상태로 될 수 있습니다. (이미지 출처: IDT)

그림 1: 클록 시간 스큐가 파이프라인 레지스터 작동에 미치는 영향을 보여주는 간단한 예입니다. 스큐된 클록은 설정 및/또는 유지 요구 사항을 위반하여 비확정 출력 상태로 될 수 있습니다. (이미지 출처: IDT)

두 개의 레지스터로 구성되는 간단한 동기식 시스템을 고려하십시오. 데이터가 레지스터를 통해 파이프라인되므로 레지스터 X의 출력 QX가 레지스터 Y의 입력이 됩니다. 클록은 독립 버퍼와 지정된 CLK1 및 CLK2를 통해 레지스터에 공급됩니다. 구성도(a)에 표시된 대로 클록 간에 스큐가 없는 경우 레지스터 설정(tSUx) 및 유지(tHx) 시간 요구 사항을 충족하는 데이터 상태 N이 레지스터의 전파 지연 후 첫 번째 클록 에지에서 레지스터 X 출력 QX에 클록됩니다. CLK2의 동일한 클록 에지에서 레지스터는 QX의 이전 상태인 N-1을 판독하고 레지스터의 전파 지연 후 출력 QY에 표시합니다.

구성도(b)와 같이 CLK1과 CLK2 사이에 시간 스큐가 있는 경우 CLK2가 발생할 때 QX의 상태가 전환 중일 수 있습니다. 레지스터 Y의 입력이 레지스터 설정 또는 유지 요구 사항을 충족하지 않고 출력이 확정되지 않아 오류가 발생할 수 있습니다.

클록 스큐를 최소화하기 위해 설계자는 인쇄 회로 트레이스 길이를 일치시키고, 전파 지연이 비슷한 버퍼 및 기타 클록 부품을 선택하고 여러 클록 소스의 부하를 균형 조정합니다. 이러한 기술은 도움이 되지만 일반적으로 클록 스큐를 적절히 제어하려면 지연 없는 클록 버퍼를 사용해야 합니다.

클록 스큐 제어

클록 스큐는 다양한 원인으로 인해 발생합니다. 다양한 길이의 인쇄 회로 상호 연결을 통해 경로가 지정되는 클록 신호가 가장 명확합니다. 다른 스큐 소스로는 다른 전파 지연을 가진 다른 활성 소자를 통과하는 클록, 부하가 다른 클록 버퍼, 버퍼의 온도 차이 등이 있습니다. 이 중 일부 효과는 제어할 수 있지만 설계자는 PLL을 사용하여 클록을 레퍼런스 클록과 다시 동기화하기 위해 활성 소자를 사용하는 경우가 많습니다.

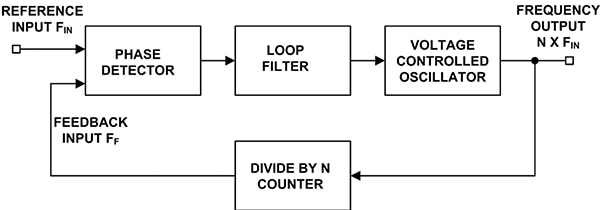

PLL 회로는 주파수 및 위상 제어에 사용됩니다. PLL 회로를 주파수 배율기, 복조기, 추적 발생기 또는 클록 복구 회로로 구성할 수 있습니다. 응용 분야마다 다른 특성이 요구되지만 모든 응용 분야에서는 그림 2에 표시된 것과 동일한 기본 회로 개념을 사용합니다.

그림 2: 주파수 배율기로 구성된 PLL의 제품 구성도. 기본적으로 전압 제어 발진기(VCO)의 위상을 제어하는 피드백 제어 시스템입니다. (이미지 출처: DigiKey)

그림 2: 주파수 배율기로 구성된 PLL의 제품 구성도. 기본적으로 전압 제어 발진기(VCO)의 위상을 제어하는 피드백 제어 시스템입니다. (이미지 출처: DigiKey)

그림 2는 주파수 배율기로 구성된 PLL의 제품 구성도를 보여줍니다. 이 회로는 모든 PLL에서 일반적으로 작동하며, 기본적으로 VCO의 위상을 제어하는 피드백 제어 시스템입니다. 입력 신호는 위상 검파기의 입력 중 하나에 적용됩니다. 다른 입력은 N으로 나누기 카운터 출력의 피드백 신호입니다. 일반적으로 두 신호의 주파수는 거의 동일합니다.

위상 검파기의 출력은 두 입력 간 위상 차이에 비례하는 전압입니다. 이 신호는 루프 필터에 적용됩니다. 루프 필터는 PLL의 동적 특성을 결정합니다. 필터링된 신호는 VCO를 제어합니다. VCO의 출력은 주파수 레퍼런스 입력(FIN)에 공급되는 입력의 N배에 해당하는 주파수 위치입니다. 이 출력 신호는 N으로 나누기 카운터를 통해 위상 검파기로 다시 전송됩니다.

일반적으로 루프 필터는 PLL 응용 분야에 필요한 특성에 적합하도록 설계됩니다. PLL이 신호를 취득하고 추적하는 경우 루프 필터의 대역폭은 고정 입력 주파수가 필요한 경우보다 더 큽니다. PLL에서 허용되고 고정되는 주파수 범위를 캡처 범위라고 합니다. PLL이 고정되고 신호를 추적 중인 경우 PLL이 따르는 주파수 범위를 추적 범위라고 합니다. 일반적으로 추적 범위는 캡처 범위보다 더 큽니다. 또한 PLL 루프 필터에 따라 고정 상태를 유지하면서 신호 주파수가 변경될 수 있는 속도가 결정됩니다. 이를 최대 슬루율이라고 합니다. 루프 필터 대역폭이 좁을수록 달성 가능한 위상 오류가 더 적습니다. 따라서 응답이 느려지고 캡처 범위가 작아집니다. 클록 응용 분야에 사용되는 PLL은 주로 고정 주파수에서 작동합니다.

지연 없는 클록 버퍼

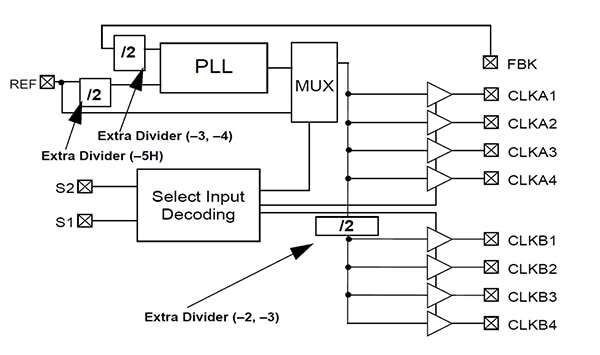

지연 없는 버퍼는 단일 레퍼런스 클록 입력에서 여러 클록 출력을 생성하여 클록 신호를 버퍼링할 수 있는 장치입니다. 여러 버퍼링된 클록 출력은 레퍼런스 클록 입력에 비해 지연이 거의 없거나 전혀 없고 출력 간의 스큐가 낮습니다. 그림 3은 Cypress Semiconductor CY2308SXC-3T 지연 없는 버퍼의 간소화된 제품 구성도를 보여줍니다.

그림 3: CY2308SXC-3T 8 출력 지연 없는 버퍼에서는 PLL을 사용하여 모든 출력을 제로 타임 스큐에 동기화합니다. (이미지 출처: Cypress Semiconductor)

그림 3: CY2308SXC-3T 8 출력 지연 없는 버퍼에서는 PLL을 사용하여 모든 출력을 제로 타임 스큐에 동기화합니다. (이미지 출처: Cypress Semiconductor)

지연 없는 버퍼는 레퍼런스 입력(REF)과 피드백 입력(FBK)을 위상 검파기의 입력으로 허용하는 집적 PLL에 내장되어 있습니다. 피드백 입력은 사용자가 선택한 출력 중 하나에 의해 구동됩니다. PLL의 내부 위상 검파기는 VCO의 출력 위상을 조정하여 두 입력에 위상 또는 주파수 차이가 없도록 합니다. 버퍼링된 클록 출력 중 하나와 그 부하가 위상 검파기를 통해 PLL에 피드백 신호로 제공되도록 선택합니다. 출력의 부하 변경에 상관없이 PLL은 출력 부하 변경을 동적으로 보정하여 출력 부하에 상관없이 입력부터 피드백을 구동하는 출력까지 지연이 없도록 합니다.

CY2308 제품군에는 10MHz ~ 133MHz의 주파수 범위에 대해 작동하는 네 가지 출력의 두 뱅크가 있습니다. 출력 시간 스큐에 대한 입력은 250ps보다 작고 출력 간의 클록 스큐는 200ps보다 작습니다. 피드백 입력에 사용되는 출력의 부하 정전 용량을 변경하여 출력 시간 스큐에 대한 입력을 조정할 수 있습니다.

이 제품군은 다양한 구성의 2로 나누기 분할기를 제공합니다. 선택된 부품은 제품 구성도에 표시된 대로 그런 두 분할기를 가진 “-3” 변형입니다. 이 구성에서는 레퍼런스 클록 입력 주파수의 2배 또는 4배에 달하는 출력을 얻을 수 있습니다.

가장 일반적으로 사용되는 지연 없는 버퍼는 5개 출력으로 구성되며 다양한 제조업체에서 구입할 수 있습니다. Cypress Semiconductor CY2305SXI-1HT, IDT 2305-1DCGI8 및 ON Semiconductor NB2305AI1HDR2G는 매우 비슷한 장치입니다. 세 장치는 모두 버퍼링된 클록 출력 5개, 단일 CLKOUT 포트, 클록 출력 쿼드 뱅크를 제공합니다. CY2308과 달리 PLL 피드백 지점이 단일 CLKOUT 신호에 고정됩니다.

지연 없는 버퍼 역학

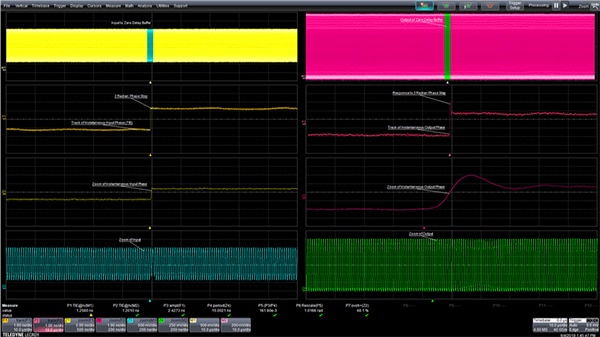

지연 없는 버퍼의 PLL은 기본적으로 피드백 제어 시스템입니다. PLL 루프 필터에 의해 역학이 제어됩니다. 모든 제어 시스템과 마찬가지로 과도 입력에 대응하여 피드백 루프 역학을 평가해야 합니다. 한 가지 방법은 입력을 단계별로 변경하여 단계별 응답을 평가하는 것입니다(그림 4).

그림 4: 66.67MHz에서 1라디안 위상 단계를 사용하여 CY2305 지연 없는 버퍼의 단계 응답 평가. 왼쪽 상단 그리드는 입력 신호이고 오른쪽 상단 그리드는 출력입니다. (이미지 출처: DigiKey)

그림 4: 66.67MHz에서 1라디안 위상 단계를 사용하여 CY2305 지연 없는 버퍼의 단계 응답 평가. 왼쪽 상단 그리드는 입력 신호이고 오른쪽 상단 그리드는 출력입니다. (이미지 출처: DigiKey)

입력 신호는 66.67MHz 사인 파형이며 취득된 신호 시간의 가운데에 1라디안 단계가 옵니다. 이 파형은 임의 파형 생성기(AWG)에서 생성되었습니다. CY2305 지연 없는 버퍼의 입력과 출력은 모두 오실로스코프에서 분할별 시간 기반을 10µs로 설정하여 취득했습니다.

그림 4의 왼쪽 상단 그리드는 입력 신호이고 오른쪽 상단 그리드는 출력입니다. 시간 간격 오류(TIE)는 이상적인 위치에 대한 측정된 클록 에지의 시간 차이이며 파형별로 측정됩니다. 기본적으로 고정 클록 속도로 참조되는 신호의 순간적인 위상입니다(이 경우 66.67MHz). 입력과 출력의 각 클록 주기에 대한 TIE 값은 TIE 트랙이라는 파형으로 표시됩니다.s 입력에 대한 트랙은 왼쪽 상단에서 두 번째 그리드입니다. 여기서 위상의 단계는 2.4ns 진폭으로 표시됩니다. 이 값은 66.67MHz 클록 주파수에 대한 1라디안 위상 변이를 나타냅니다.

오른쪽 상단에서 두 번째 트레이스는 출력의 TIE 트랙입니다. 출력 트랙은 일부 오버슈트를 보여주며 입력 변경에 일치하는 새로운 평균값에 정착됩니다. 위쪽에서 세 번째 트레이스는 왼쪽 입력과 오른쪽 출력의 가로로 확장된 확대/축소 트레이스를 보여줍니다. 입력 단계에 대한 세부 정보는 명확한 전이를 보여줍니다.

출력을 확대/축소하면 일부 오버슈트가 나타났다가 약 500ns의 대략 1주기에서 새 평균값으로 빠르게 정착됩니다. 이는 대규모 위상 단계에서 정상 작동하는 단계 응답입니다. 빠르게 정착되므로 불안정한 진동 반응의 흔적이 없습니다.

두 하단 트레이스는 입력(왼쪽)과 출력(오른쪽)의 가로로 확장된 보기를 보여줍니다. 대규모 위상 단계는 입력에 정확히 표시되지만 느린 출력 응답은 이 시간 단위에 올바로 표시되지 않습니다.

결론

고성능 디지털 시스템 설계자는 클록 분배 타이밍의 차이 또는 불확실성을 방지하기 위해 클록 생성 및 분배 회로 설계에 더욱 세심한 주의를 기울여야 합니다. 이러한 문제는 시스템 성능을 저하하거나, 타이밍 마진을 줄이거나, 기능적인 오류를 발생시킬 수 있습니다.

설명한 바와 같이 지연 없는 버퍼는 여러 클록 신호를 전파하고 마스터 클록 신호와 동기화된 상태로 유지할 때 유용한 능동 제어 도구입니다. 이 버퍼는 감지된 출력에서 부하가 크게 변경되더라도 탁월한 추적 성능을 제공합니다. 하지만 표시된 대로 설계자는 지연 없는 버퍼의 피드백 루프 역학을 신중하게 평가하여 응용 분야의 요구 사항을 충족하는지 확인해야 합니다.

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.