아날로그 기본 사항: 샘플 앤 홀드 회로의 작동으로 ADC 정확성을 보장하는 방법

DigiKey 북미 편집자 제공

2020-04-22

"실제" 환경의 아날로그 신호를 업스트림 처리 가능한 디지털 신호로 변환하는 것은 오디오 녹음, 사물 인터넷(IoT), 산업용 IoT(IIoT), 사물 인공 지능(AIoT)을 비롯한 전자 시스템의 기본적인 기능입니다. 하지만 이러한 변환을 효과적이고 효율적으로 수행하려면 간과되기 쉬운 기본 원칙과 단계를 이해해야 합니다.

예를 들어, 아날로그 디지털 컨버터(ADC) 입력에 일반 아날로그 신호가 적용되면 진폭이 계속해서 변경되고 변환을 마치면 시작할 때와 달라지는 것을 감안할 때 신호는 얼마나 정확히 "보관" 및 "샘플링" 될까요? 이 진폭 변경 또는 스큐로 인해 심각한 오류가 발생할 수 있습니다. 신호를 변환하는 데 많은 시간이 걸리는 고분해능 ADC의 경우 특히 그렇습니다. 설계자는 이러한 오류의 근원을 파악하여 제거해야 합니다.

이 기사에서는 ADC용 샘플 앤 홀드(S&H) 또는 트랙 앤 홀드(T&H) 회로를 사용하여 진폭 스큐를 차단하는 방법을 보여 줍니다. S&H(또는 T&H)는 입력을 실제로 샘플링하며 입력 안티앨리어싱 저역 통과 필터와 ADC 사이에서 작동합니다. 또한 이 기사에서는 S&H IC의 특성과 선택 기준을 설명하고 통합 S&H와 함께 ADC를 살펴봅니다. 이해를 돕기 위해 응용 분야에 따라 다양한 특성을 가진 Texas Instruments, Maxim Integrated 및 Analog Devices의 장치를 예를 들어 보여 줍니다.

ADC에서 샘플 앤 홀드의 역할

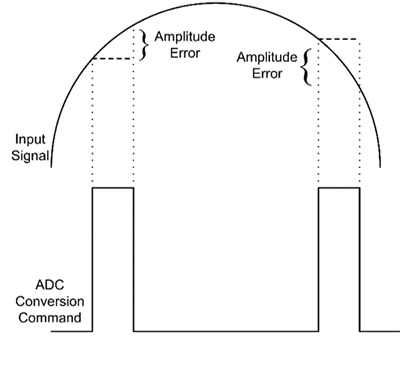

DC가 아닌 신호가 ADC 입력에 적용되면 진폭이 계속해서 변경됩니다. 하지만 아날로그 디지털 변환 공정은 간격 제한이 있으므로 해당 기간 동안 ADC 입력 진폭이 변경됩니다(그림 1). 이 진폭 스큐로 인해 심각한 오류가 발생할 수 있습니다.

그림 1: ADC에 다양한 입력 신호가 포함될 경우 디지털화 중 신호 진폭 변화로 인해(하단) 진폭 오류(상단)가 발생할 수 있습니다. (이미지 출처: DigiKey)

그림 1: ADC에 다양한 입력 신호가 포함될 경우 디지털화 중 신호 진폭 변화로 인해(하단) 진폭 오류(상단)가 발생할 수 있습니다. (이미지 출처: DigiKey)

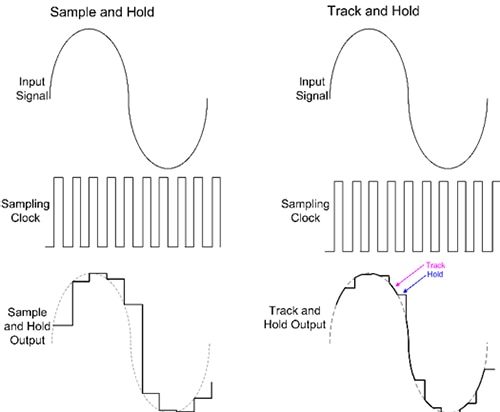

신호를 샘플링하고 변환이 진행 중인 동안 고정 진폭을 유지하려면 ADC에서 진폭 스큐를 방지하는 것이 중요합니다. 이를 위해 ADC용 S&H 또는 T&H 회로를 사용합니다(그림 2).

그림 2: S&H(왼쪽) 회로와 T&H(오른쪽) 회로의 주된 차이점은 추적 기간에 있습니다. 즉, S&H 회로는 짧고 T&H 회로는 깁니다. (이미지 출처: DigiKey)

그림 2: S&H(왼쪽) 회로와 T&H(오른쪽) 회로의 주된 차이점은 추적 기간에 있습니다. 즉, S&H 회로는 짧고 T&H 회로는 깁니다. (이미지 출처: DigiKey)

두 회로는 모두 변환 공정 기간 동안 입력 신호를 샘플링하고 샘플링된 전압을 일정하게 유지합니다. T&H 회로 출력(오른쪽)에서는 샘플링할 신호가 적용될 때까지 입력 신호를 추적한 다음 ADC 변환 기간 동안 샘플 값을 유지합니다. S&H에서는 샘플 애퍼처가 더 짧고 일련의 샘플링된 레벨이 출력됩니다(왼쪽). T&H와 S&H의 주요 차이점은 추적 기간에 있습니다. 즉, S&H는 매우 짧고 T&H는 훨씬 더 깁니다. 두 회로는 모두 신속한 전환을 바탕으로 신호 입력에 연결된 스토리지 커패시터를 분리합니다. 이 기사의 나머지 부분에서는 'S&H'를 'S&H 또는 T&H'와 같은 의미로 사용하겠습니다.

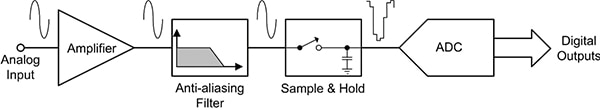

S&H 단계는 입력을 실제로 샘플링하며 입력 안티앨리어싱 저역 통과 필터와 ADC 사이에서 작동합니다. 저역 통과 필터에서는 안티앨리어싱 대역 제한을 수행하며 S&H에 앞서서 샘플링 전에 신호 대역을 제한하여 앨리어싱을 방지해야 합니다(그림 3).

그림 3: 디지타이저 신호 경로에서 S&H는 안티앨리어싱 저역 통과 필터와 ADC 사이에 위치합니다. (이미지 출처: DigiKey)

그림 3: 디지타이저 신호 경로에서 S&H는 안티앨리어싱 저역 통과 필터와 ADC 사이에 위치합니다. (이미지 출처: DigiKey)

따라서 S&H 이전의 신호는 모두 아날로그 신호입니다. S&H 출력은 ADC에 공급되는 샘플링된 파형입니다.

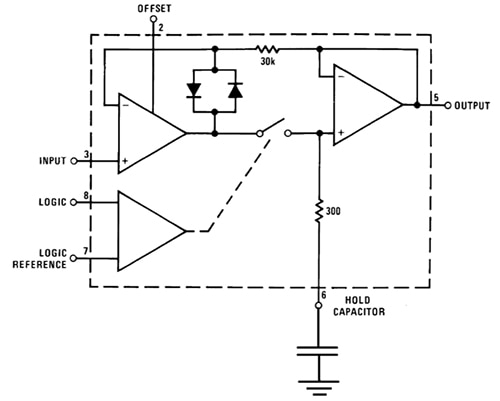

일반적인 S&H 장치

Texas Instruments LF398MX/NOPB S&H 집적 회로(IC)의 제품 구성도는 기본 회로 구성을 보여 줍니다(그림 4). S&H는 빠른 전환과 고품질 커패시터를 사용하여 구현됩니다. LF398MX/NOPB의 경우 커패시터가 IC 외부에 있습니다. 스위치가 닫히면 커패시터가 입력 신호 전압 레벨로 충전됩니다. 스위치가 열리면 ADC에서 디지털화할 때까지 커패시터에서 해당 전압을 유지합니다. 이 S&H에서는 FET를 양극 트랜지스터와 결합하는 bi-FET 기술을 사용하여 높은 DC 정확도(0.002%(통상))와 매우 낮은 전압 강하(초당 83µV 미만(통상))로 빠른 취득(0.01% 진폭 오류에서 6µs 미만)을 지원합니다. 내부 증폭기는 스위치와 홀드 커패시터를 버퍼링합니다.

S&H의 취득 시간은 홀드 커패시터의 값(0.001µF ~ 0.1µF 범위 이내)에 따라 달라집니다. 외부 홀드 커패시터는 유전체 흡수와 누설이 적어야 합니다. 폴리스타이렌, 폴리프로필렌 및 테플론 커패시터가 권장됩니다.

그림 4: Texas Instruments LF398MX/NOPB S&H의 제품 구성도는 주요 부품(고속 스위치, 외부 홀드 커패시터)을 보여 줍니다. (이미지 출처: Texas Instruments)

그림 4: Texas Instruments LF398MX/NOPB S&H의 제품 구성도는 주요 부품(고속 스위치, 외부 홀드 커패시터)을 보여 줍니다. (이미지 출처: Texas Instruments)

S&H 특징

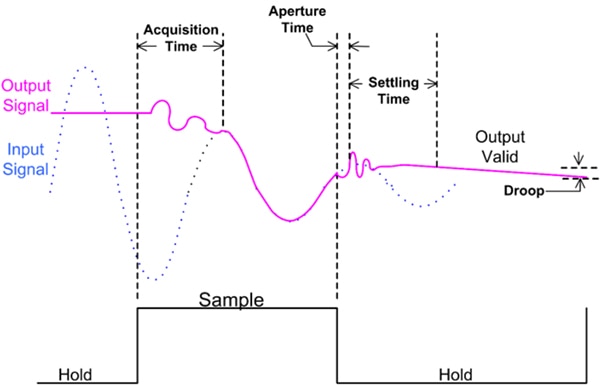

S&H 장치에는 작동을 설명하는 많은 특정 용어가 있습니다(그림 5).

그림 5: 일반 S&H 동적 특성의 정의에는 취득 시간, 정착 시간, 애퍼처 시간, 진폭 강하가 있습니다. (이미지 출처: DigiKey)

그림 5: 일반 S&H 동적 특성의 정의에는 취득 시간, 정착 시간, 애퍼처 시간, 진폭 강하가 있습니다. (이미지 출처: DigiKey)

취득 시간은 S&H에서 입력 신호 추적을 시작할 때까지 스위칭부터 샘플 모드까지 걸리는 시간이며, 홀드 커패시터 값, 스위치 계열 저항 및 신호 경로의 함수입니다. 홀드 모드로 복귀할 때 장치에서 추적을 중지하고 홀드 값을 유지하기 시작할 때까지 시간 지연이 발생할 수 있습니다. 이 시간이 애퍼처 시간입니다. 애퍼처 시간은 구동기 및 스위치의 전파 지연에 관한 함수입니다. 애퍼처 불확실성 또는 지터는 클록 변화와 잡음으로 인한 애퍼처 시간 변화입니다.

홀드 모드에서는 모드를 시작한 후 장치가 정착할 때까지 홀드 값에 대한 오류 구간 이내의 시간 간격이 있으며, 이 시간을 정착 시간 또는 홀드 정착 시간이라고 합니다. 정착 시간에는 스위치 구동기와 홀드 커패시터 간의 원치 않는 전하 전송이 포함되며, 이를 홀드 단계 또는 받침대 오류라고 합니다. 홀드 단계의 크기는 mV 범위 이내이며 신호의 전체 범위를 최대한 높게 유지하여 효과를 최소화할 수 있습니다.

S&H의 최단 샘플링 기간은 취득 시간, 애퍼처 시간 및 정착 시간의 합계입니다. 가능한 최대 샘플링 속도는 취득 시간, 애퍼처 시간 및 정착 시간 합계의 역입니다.

홀드 모드에 있는 동안 홀드 커패시터의 누설로 인해 S&H 홀드 값이 감소할 수 있습니다. 이 전압 증가를 강하라고 하며, 일반적으로 mV/초의 강하 레이트로 지정됩니다.

S&H 구성

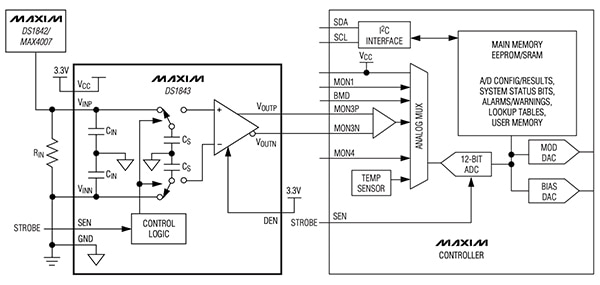

S&H IC는 응용 분야의 니즈에 따라 다양한 구성으로 사용할 수 있습니다. 차동 출력 트랜스듀서(예: 가속도계, 스트레인 게이지, 광학 전류 모니터) 연결과 같은 차동 입력이 필요한 응용 분야를 고려해 보십시오. Maxim Integrated DS1843D+TRL은 이러한응용 분야를 위한 S&H IC의 좋은 예입니다(그림 6).

그림 6: 이 일반 작동 회로에 표시된 것처럼 Maxim Integrated DS1843+TRL은 이중 홀드 커패시터를 사용하여 차동 샘플링을 구현하는 차동 S&H입니다. (이미지 출처: Maxim Integrated)

그림 6: 이 일반 작동 회로에 표시된 것처럼 Maxim Integrated DS1843+TRL은 이중 홀드 커패시터를 사용하여 차동 샘플링을 구현하는 차동 S&H입니다. (이미지 출처: Maxim Integrated)

표시된 DS1843+TRL은 버스트 모드 수신 신호 강도 표시기(RSSI) 측정을 위한 일반 광학 라인 전송 응용 제품에 속합니다. Maxim Integrated DS1842/MAX4007은 레퍼런스 입력에 연결된 애벌런치 광 다이오드에서 전류를 미러링하는 전류 모니터입니다. 출력 전류는 저항기 RIN을 통해 전달되어 전압으로 변환됩니다. 이 전압은 완전 차동 샘플링 스위치와 커패시터, CS, 차동 출력 버퍼로 구성되는 DS1843에 의해 다르게 측정됩니다. 이 S&H에서는 각각 양극 차동 입력과 음극 차동 입력에 연결된 두 5pF 커패시터를 사용합니다. 낮은 정전 용량 값은 짧은 취득 시간을 보장합니다. 이 장치는 300ns 미만의 고속 샘플 (취득) 시간을 자랑합니다. S&H의 홀드 시간은 100µs 이상입니다.

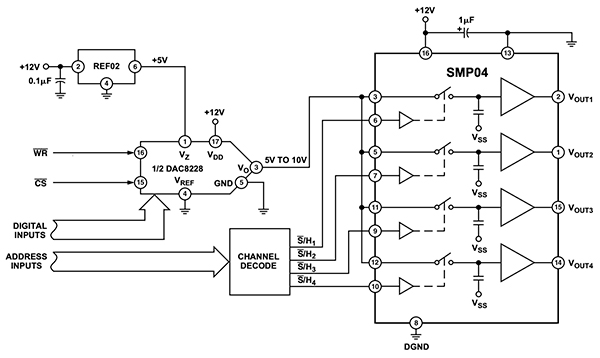

단일 IC 패키지에서 4개 또는 8개 S&H 회로를 보유한 장치를 사용할 수 있습니다. 예를 들어, Analog Devices의 SMP04ESZ-REEL 4중 S&H가 있습니다. SMP04ESZ-REEL은 4개의 S&H 회로를 공통 패키지에 통합하는 CMOS 장치이며 취득 시간은 7µs이고 강하 레이트는 2mV/s에 불과합니다(그림 7).

또한 그림 7은 디지털 아날로그 컨버터(DAC)에서 S&H를 사용하여 DAC에서 코드 전이에 의해 발생하는 과도 출력 또는 결함을 방지할 수 있는 방법을 보여 줍니다.

그림 7: Analog Devices SMP04 4중 S&H에는 4개의 독립 S&H 회로와 정합 버퍼 증폭기가 포함되어 있습니다. 표시된 회로에서는 SMP04를 사용하여 DAC 출력을 네 개의 채널로 다중화합니다. (이미지 출처: Analog Devices)

그림 7: Analog Devices SMP04 4중 S&H에는 4개의 독립 S&H 회로와 정합 버퍼 증폭기가 포함되어 있습니다. 표시된 회로에서는 SMP04를 사용하여 DAC 출력을 네 개의 채널로 다중화합니다. (이미지 출처: Analog Devices)

그림에서는 SMP04를 통해 DAC 출력을 네 개의 다중화된 채널로 분할하여 DAC 출력을 다중화합니다. S&H 회로를 사용하면 결함 이후까지 DAC의 출력을 선택적으로 지연시켜서 DAC 출력을 평활화할 수 있습니다.

S&H 회로를 여러 개 사용하면 다중화된 입력을 파이프라이닝하여 ADC의 처리량을 높일 수 있습니다. 여기서는 여러 S&H를 멀티플렉서 출력에 공통으로 연결합니다. ADC를 S&H 중 하나에 연결하여 변환에 대한 입력 수준을 유지합니다. 각 S&H는 서로 다른 멀티플렉서 채널을 취득하여 ADC에 연결되므로, 첫 번째 S&H는 다른 다중화된 채널에 자유롭게 연결됩니다. 이 파이프라이닝 기술을 사용하면 ADC 신호 경로에서 S&H 취득 시간이 제거됩니다.

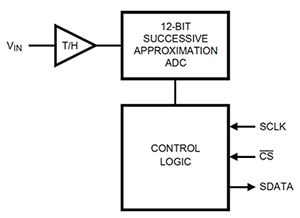

많은 ADC가 통합 패키지 내에서 S&H 또는 T&H 회로를 통합합니다. 예를 들면 50kS/s ~ 200kS/s 범위 이내의 샘플링 속도로 작동하는 T&H가 내장된 12비트 연속 근사화 레지스터(SAR) ADC인 Texas Instruments ADC121S021CIMFX가 있습니다. 이 ADC는 배선 레이아웃을 간소화하는 고속 직렬 출력 버스를 제공합니다(그림 8).

그림 8: Texas Instruments ADC121S021은 T&H 회로가 내장된 12비트 단일 채널 SAR ADC입니다. (이미지 출처: Texas Instruments)

그림 8: Texas Instruments ADC121S021은 T&H 회로가 내장된 12비트 단일 채널 SAR ADC입니다. (이미지 출처: Texas Instruments)

이 ADC는 일반적으로 T&H가 내장된 많은 ADC 회로를 통합하여 pc 기판 레이아웃을 간소화하고 부품 수를 최소화할 수 있도록 도와줍니다. 차동 입력 연결, 다중화된 입력, ADC에 내장형 T&H 또는 S&H 회로가 없는 경우를 비롯한 특수 구성에서는 외부 T&H 회로가 사용됩니다.

결론

오디오 녹음부터 최고급 IIoT 또는 AI 분석까지 아날로그 신호를 디지털 신호로 변환하는 가장 기본적인 기능에서는 S&H 또는 T&H 회로에 주의해야 합니다. 이러한 회로는 변환 중에 ADC에 대한 입력 전압을 일정하게 유지하므로 아날로그 디지털 변환 공정 중에 전압 스큐 오류를 최소화하는 데 필수적입니다. S&H는 ADC에 내장되거나 외부에 장착될 수 있지만 안티앨리어싱 저역 통과 필터와 ADC 사이의 신호 경로 내에 있어야 합니다. 위에서 살펴본 바와 같이 다양한 설계 응용 분야에 맞는 많은 구성(단일, 차동, IC당 여러 장치)이 있습니다. 이러한 응용 분야는 DAC에서 코드 전환에 의해 발생되는 과도 출력 또는 결합 방지 등으로 확장되고 있습니다.

권장 참고 자료

면책 조항: 이 웹 사이트에서 여러 작성자 및/또는 포럼 참가자가 명시한 의견, 생각 및 견해는 DigiKey의 의견, 생각 및 견해 또는 DigiKey의 공식 정책과 관련이 없습니다.